- •Міністерство освіти і науки україни

- •Методичні вказівки

- •Укладачі в.В. Скородєлов, о.Ф. Даниленко, г.В. Гейко.

- •Зміст Вступ..................................................................................................................................4

- •Рекомендована література……………………………………………………………..17 Вступ

- •1. Індивідуальні завдання

- •Задача 4

- •Задача 5

- •1.2. Задачі до другого модуля - «Комп'ютерна схемотехніка»

- •Задача 1

- •Задача 2

- •Задача 3

- •Задача 4

- •Задача 5

- •Задача 6

- •2. Методика виконання завдань та приклади рішення задач

- •2.1 Модуль 1 – «Комп’ютерна електроніка»

- •2.2 Модуль 2 – «Комп’ютерна схемотехніка»

- •3. Рекомендації щодо оформлення звіту

- •«Комп’ютерна електроніка та схемотехніка»

- •Рекомендована література

2.2 Модуль 2 – «Комп’ютерна схемотехніка»

Задача 2

Побудуйте тригер заданого типу на основі інтегральних мікросхем, які вміщують базові тригери, і необхідних логічних елементах. Вихідні дані: тип заданого тригера - Т; синхронізація – зворотна статична; кількість ступенів – 2; Тип мікросхем базового тригера – К155ТМ5.

У відповіді приведіть: функціональну схему; таблицю станів; умовне графічне позначення; короткий опис принципу дії та часову діаграму.

Рішення:

При розробці заданої схеми враховуємо, що інтегральна мікросхема К555ТМ5 має у своєму складі чотири D-тригера з прямою статичною синхронізацією [5].

Як відомо [2,3], на основі D-тригера можна побудувати Т-тригер. Для цього необхідно організувати зворотний зв’язок між інверсним виходом тригера Q та його інформаційним входом D а вхідні сигнали подавати на синхровхід С. Таким чином, вхід С базового D -тригера перетвориться в лічильний вхід Т заданого Т-тригера.

В даному випадку необхідно побудувати двоступеневий Т-тригер. Його можна побудувати по класичній схемі MS–тригерів [2,3]. При цьому можна використати два базових D-тригера і організувати зворотний зв’язок між інверсним виходом другого тригера (Q2) та інформаційним D-входом першого тригера.

Крім цього, в заданому для побудови тригері необхідно забезпечити також зворотну статичну синхронізацію. В даному випадку заданий тригер повинен переключатися (змінювати свій стан на протилежний) з приходом на лічильний вхід Т кожного наступного негативного перепаду вхідного сигналу з «1» в «0». Для забезпечення цього необхідно використати допоміжний інвертор на Т-вході тригера, що будується. За допомогою цього інвертора забезпечується перетворення однофазного інверсного вхідного сигналу в парафазний. При цьому, вхідний непроінвертований сигнал необхідно подати на синхровхід С другого базового D–тригера, а проінвертований – на аналогічний вхід першого базового D–тригера.

Функціональна схема розроблюваного тригера приведена на рисунку 2.5. З цієї схеми видно, якщо на вхід «Т» приходить «1», то перший D-тригер працює в режимі збереження інформації, а другий D-тригер переключається (в нього переписуються дані («0» або «1»), які зберігаються в першому тригері).

При зміні на Т-вході сигналу з «1» до «0» (негативний перепад) перший тригер переключається (змінює свій стан на протилежний), а другий D–тригер тепер працює в режимі збереження інформації).

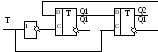

Рисунок 2.5

На рисунку 2.6 приведено умовне графічне позначення розробленого тригера, а в таблиці 2.1 приведена таблиця його станів.

Рисунок 2.6

Таблиця 2.1

|

Вхід |

Виходи | |

|

Т |

Q1 |

Q2 |

|

1 |

1 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

0 |

0 |

0 |

|

1 |

1 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

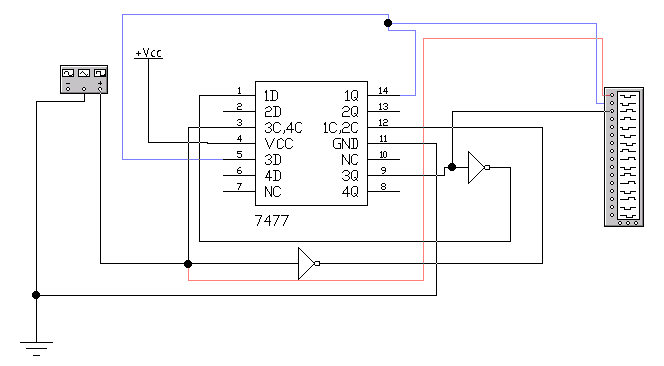

Промоделюємо розроблену схему за допомогою пакету EWB: аналогом мікросхеми К555ТМ5 являється мікросхема SN7477J, яка знаходиться в бібліотеці цифрових мікросхем. Так як в цій мікросхемі (як і в К155ТМ5) на виводи виведені тільки прямі виходи базових D–тригерів, то необхідно використати ще один допоміжний інвертор для організації інверсного виходу (Q2). Обидва інвертори можна взяти з бібліотеки логічних елементів. Для цих цілей можна використати також логічні елементи з бібліотеки цифрових мікросхем.

Джерелом вхідних сигналів може служити функціональний генератор, який в даному випадку працює в режимі генерації прямокутних імпульсів. Цей генератор беремо з бібліотеки приладів. Для цих цілей можна використати і генератор слів, який також є в бібліотеці приладів.

Часову діаграму роботи розроблюваного тригера можна одержати за допомогою 16-канального логічного аналізатора, який можна взяти з бібліотеки приладів. Схема для моделювання наведена на рисунку 2.7.

Рисунок 2.7

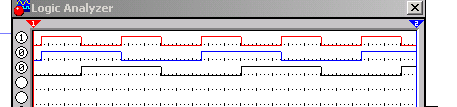

Часові діаграми приведені на рисунку 2.8. На цьому рисунку показано: «Т» - це вхід розробленого тригера, «Q1» – це вихід першої ступені (тобто вихід першого D-тригера, який входить в склад мікросхеми SN7477J), «Q2» - це вихід другої ступені (тобто вихід другого D-тригера, який також входить в склад мікросхеми SN7477J).

Т Q1 Q2

Рисунок 2.8

Як видно з рисунку 2.8, переключення тригера відбувається по негативному фронті імпульсу на вході «Т», а це і є зворотна синхронізація. Таким чином, розроблений тригер працює правильно.