Федеральное агентство по образованию

Санкт-Петербургский государственный

электротехнический университет «ЛЭТИ»

Кафедра ВТ

Реферат № 2

по дисциплине

«Проектирование дискретных устройств на VHDL»

на тему

«Язык VHDL. История, стандарты, обзор возможностей.

Типовая структура файла с описанием устройства»

Выполнил:

Группа:

Санкт-Петербург

2013

Оглавление

Оглавление 2

История 3

Стандарты языка VHDL 3

Возможности VHDL 3

Язык VHDL является международным стандартом в автоматизации проектирования цифровых систем. В основном он предназначен для точного описания проектируемых систем и моделирования их на начальных этапах. Возможности языка позволяют описывать алгоритмы функционирования систем, а также имеет средства для описания параллельных процессов.

История

В начале 60-х годов стали появляться языки описания аппаратуры. На тот момент их было совсем немного, в частности LOTIS, EPICURE, CDL, HARGOL, CASSANDRE, DDL. Но к началу 70-х годов количество языков превысило две сотни.

Как результат в 1973 году была предпринята попытка разработать стандарт такого языка. Проект назывался CONLAN. К 1983 году проект завершился полным определением языка. CONLAN стал основой для VHDL.

Первыми, кто поддержал VHDL, стала компании IBM, Intermetrix и Texas Instruments. С их появлением в проекте язык стал стремительно развиваться. В 1985 году появилась версия 7.2, которая удовлетворяла большинству требований и была принята как стандарт Министерством обороны США. В декабре 1987 года окончательная версия была принята как стандарт IEEE Std 1076-1987.

Стандарты языка vhdl

Есть два международных стандарта, это IEEE Std 1076-2002 и IEEE Std 1076-2008 «IEEE Standard VHDL Language Reference Manual». Также есть российский стандарт ГОСТ Р 50754-95 «Язык описания аппаратуры цифровых систем VHDL. Описание языка».

Возможности vhdl

На языке VHDL можно описать проекты разной степени сложности. Его возможности позволяют построить модель на разных уровнях абстракции, выполнять моделирование, вести документирование проекта, генерировать тесты.

Основой VHDL является язык ADA. Как результат он многое наследует из него. Для расширения возможностей были дополнительно введены понятия модельного времени, сигнала, события и других.

Принцип построения:

-

функциональная иерархия и рекурсия

-

структурная иерархия

-

представление системы в виде параллельно функционирующих взаимодействующих процессов

-

использование абстрактных типов данных

-

использование событийного моделирования

-

поддержка различных уровней абстракции и детализации представления проекта.

Основные средства языка VHDL это:

-

библиотеки

-

модули интерфейса, тела, конфигурации

-

процедуры и функции

-

перечисляемые, числовые и физические типы данных, а также массивы

-

множество объектов: константы, переменные, сигналы, порты и другие

-

логические и арифметические операции

-

последовательные и параллельные операторы

Давайте рассмотрим подробней средства языка.

Классы

Они жестко определены и их всего три – константа, переменная и сигнал. Константа и переменные нам знакомы, а вот сигнал служит для описания цифровых схем и обладает многими свойствам реальных сигналов в цифровой технике. Для использования объекта, его нужно сначала определить, как и в большинстве языков программирования:

constant gnd : bit :='1';

variable y : bit;

signal z : bit;

Дальше мы можем использовать эти объекты в коде.

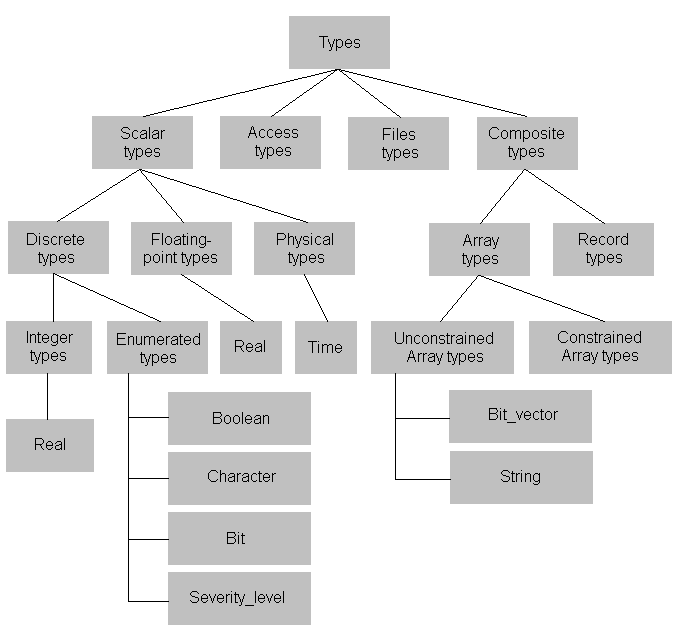

Типы данных

Используется библиотека std. В сути все просто:

логический type boolean is (false,true);

битовый type bit is (‘0’,’1’);

символьный type character s ();

перечисляемый type severity_level is (note, warning, error, failure);

целый type integer is range -2147483647 to 2147483647;

вещественный type real is range -1.0E308 to 1.0E308;

Имеются подтипы данных. Они описаны в std:

подтип натуральных чисел subtype natural is integer range 0 to integer'high;

подтип положительных чисел subtype pozitive is integer range 1 to integer'high;

Описание массивов и векторов:

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

signal adddr : bit_vector (7 downto 0);

constant txt : string := "VHDL";

Библиотека std подключается к проекту по умолчанию, нам сразу доступны типы данных и их не требуется переопределять.

классификация типов данных

Массивы

При работе с массивами в VHDL есть момент, которые нужно учитывать - как правило, синтезаторы не работают с многомерными массивами. Исключение составляет массив векторов.

заданная размерность массива type type_name is array (range) of element_type;

без размерности массива type type_name is array (type range <>) of element_type;

Массивы применяются для описания шин, регистров, счетчиков, сумматоров, ОЗУ и т.д.

Операции

Операций не так много и большинство нам знакомы:

логические операции: and, or, nand, nor, xor, xnor;

операции сравнения: =, /=, <, <=, >, >=;

операции сдвига: sll, srl, sla, sra, rol, ror;

операции сложения: +, -, &;

операции смены знака числа;

умножение деление: *, /, mod, rem;

прочие операции: **, abs, not.

Операторы языка

Операторы в VHDL могут быть синтезируемые и не синтезируемые. Также они делятся на последовательные, параллельные, простые и составные.

Последовательные операторы определяют алгоритм выполнения подпрограмм и процессов. Их выполнение идет в том порядке, в котором они расположены в коде.

assert (последовательный);

case;

exit;

if;

loop;

next;

null;

report;

return;

wait;

Параллельные процессы используют для определения блоков и процессов. Выполняются параллельно и порядок не зависит от расположения в коде.

assert (параллельный);

block;

generate;

process;

применение компонентов (port map ...);

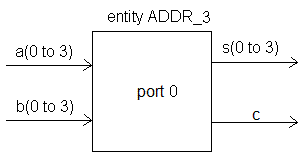

Интерфейсы

Передаваемые в архитектуру параметры, входные и выходные сигналы, оформляются по определенным правилам.

entity NAME is

generic (

перечисляем параметры

);

port (

описываем порты

);

begin

end NAME;

Пример интерфейса

Есть возможность создавать программы без связи с внешним миром. Например:

library ieee;

use ieee.std_logic_1164.all;

entity TEST is

end TEST;

Архитектура программы

В ней содержится две части:

-

Описание деклараций

-

Исполняемые операторы

Общий принцип построения:

architecture NAME_ARCHITECTURE of NAME_ENTITY is

пишем типы данных;

описываем функции;

описываем сигналы:

и т.д.

begin

исполняемые операторы.

end NAME_ARCHITECTURE;

Кстати, язык VHDL позволяет иметь в коде несколько архитектурных тел.

architecture a1 of HAND is

…

end a1;

architecture a2 of HAND is

…

end a2;

Атрибуты

У объектов в языке VHDL есть различные атрибуты. Их можно разделить на предопределенные и пользовательские.

Предопределенные имеют 3 группы: атрибуты массивов, атрибуты сигналов, атрибуты типов данных.

Атрибуты массивов:

A'left(N) Левая граница N-го индекса массива А

A'right(N) Правая граница N-го индекса массива А

A'high(N) Верхняя граница N-го индекса массива А

A'low(N) Нижняя граница N-го индекса массива А

A'range(N) Диапазон N-го индекса массива А

A'reverse_range(N) Обратный диапазон N-го индекса массива А

A'length(N) Длина диапазона N-го индекса массива А

Атрибуты сигналов:

S'active TRUE, если было присвоение, но текущее значение еще прежнее

S'delayed(t) Значение сигнала, существовавшее на время t перед вычислением данного атрибута

S'event TRUE, если происходит изменение сигнала

S'last_active Время от последнего присвоения значения сигналу до момента вычисления атрибута

S'last_event Время от последнего изменения сигнала до момента вычисления атрибута

S'last_value Последнее присвоенное сигналу значение

S'stable(t) TRUE, если не происходило изменение сигнала в течение времени t

S'transaction TRUE, если происходит очередное присвоение значения сигналу

S'quiet FALSE, если было присвоение, но текущее значение еще прежнее

Атрибуты типов данных

T'base Базовый тип данных

T'left Левая граница значений T

T'right Правая граница значений T

T'high Верхняя граница значений T

T'low Нижняя граница значений T

T'pos(X) Позиция значения Х в наборе значений Т

T'val(N) Значение элемента в позиции N набора значений Т

T'succ(X) Значение в наборе значений T, на одну позицию большее X

T'pred(X) Значение в наборе значений T, на одну позицию меньшее X

T'succ(X) Значение в наборе значений T, на одну позицию вправо от X

T'pred(X) Значение в наборе значений T, на одну позицию влево от X

Подпрограммы

Всего 2 вида – функции и процедуры. В std_logic_1164 описаны разные функции. В коде программы можно просто обращаться к ним по имени. Например:

If falling_edge(ale) then

…

end if;

Библиотеки

Как и многие другие языки, VHDL дает возможность подключать различные библиотеки с заранее написанным кодом. Библиотеки могут быть скомпилированными для определенного САПР или быть в исходных кодах. По умолчанию они компилируются в библиотеку work. В общем виде библиотека выглядит так:

package package_name is

описываем сигналы и константы

объявляем функций, процедуры

…

end package_name;

package body package_name is

…

end package_name;

Для использования собственной библиотеки ее нужно подключить:

library ieee, EASY, work;

use ieee.std_logic_1164.all;

use my.biblio.all;

Пример типового кода

library ieee;

use ieee.std_logic_1164.all;

entity dec is

port (res, ale, cs : in std_logic;

addr : in std_logic_vector(15 downto 5);

cs_er, cs_ram : out std_logic);

end dec;

architecture dec_arch of dec is

begin

process (res, ale)

signal s_cs_ram, s_cs_er : std_logic;

begin

if (res = '1') then

s_cs_ram <= '0';

s_cs_er <= '0';

elsif rising_edge(ale) then

if (addr = "00000000000") then

s_cs_ram <= '1';

s_cs_er <= '0';

elsif (addr = "00000000001") then

s_cs_ram <= '0';

s_cs_er <= '1';

else

s_cs_ram <= '0';

s_cs_er <= '0';

end if;

end if;

end process;

cs_ram <= s_cs_ram and cs;

cs_er <= s_cs_er and cs;

end dec_arch;