Лабораторная1

.docФедеральное агентство по образованию

Санкт-Петербургский государственный

электротехнический университет «ЛЭТИ»

Кафедра ВТ

Отчет по лабораторной работе №1

Выполнили:

Группа:

Санкт-Петербург

2013

Современный проектный поток

Цель работы

Целью работы является произвести синтез простейшей комбинационной схемы, смоделировать ее поведение и произвести имплементацию в реальную схему FPGA.

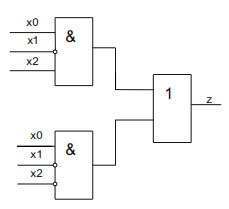

Ниже приведена схема исследуемого устройства:

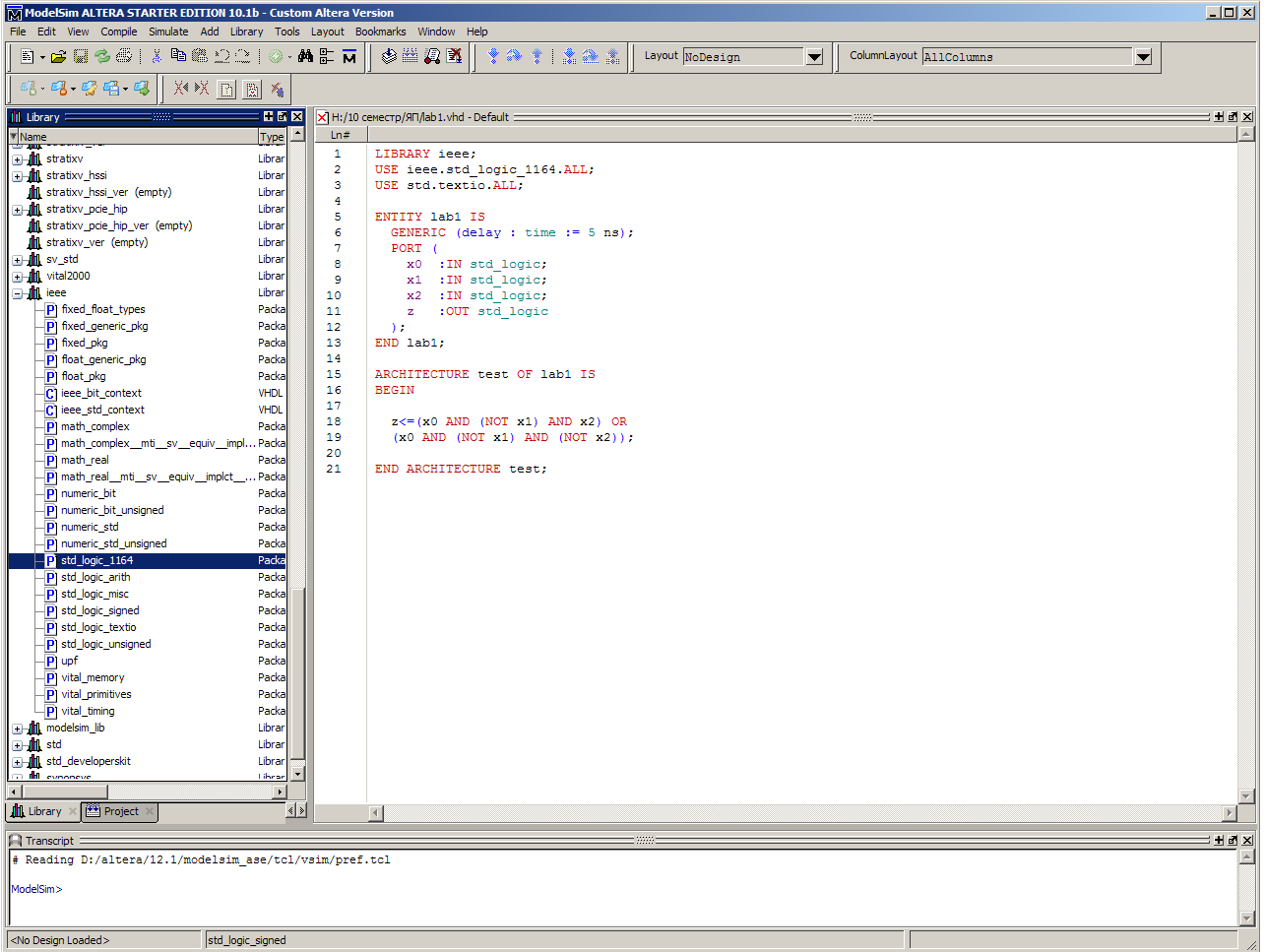

Исходный текст программы:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE std.textio.ALL;

ENTITY lab1 IS

GENERIC (delay : time := 5 ns);

PORT (

x0 :IN std_logic;

x1 :IN std_logic;

x2 :IN std_logic;

z :OUT std_logic

);

END lab1;

ARCHITECTURE test OF lab1 IS

BEGIN

z<=(x0 AND (NOT x1) AND x2) OR

(x0 AND (NOT x1) AND (NOT x2));

END ARCHITECTURE test;

Работа в ModelSim

Для работы будем использовать ModelSim версии 10.1b

Запускаем программу и создаем новый проект. Добавляем листинг логического устройства в наш проект.

После компиляции рабочего проекта в окне списка «Библиотеки» появилась наша библиотека «work» с вложенными объектами.

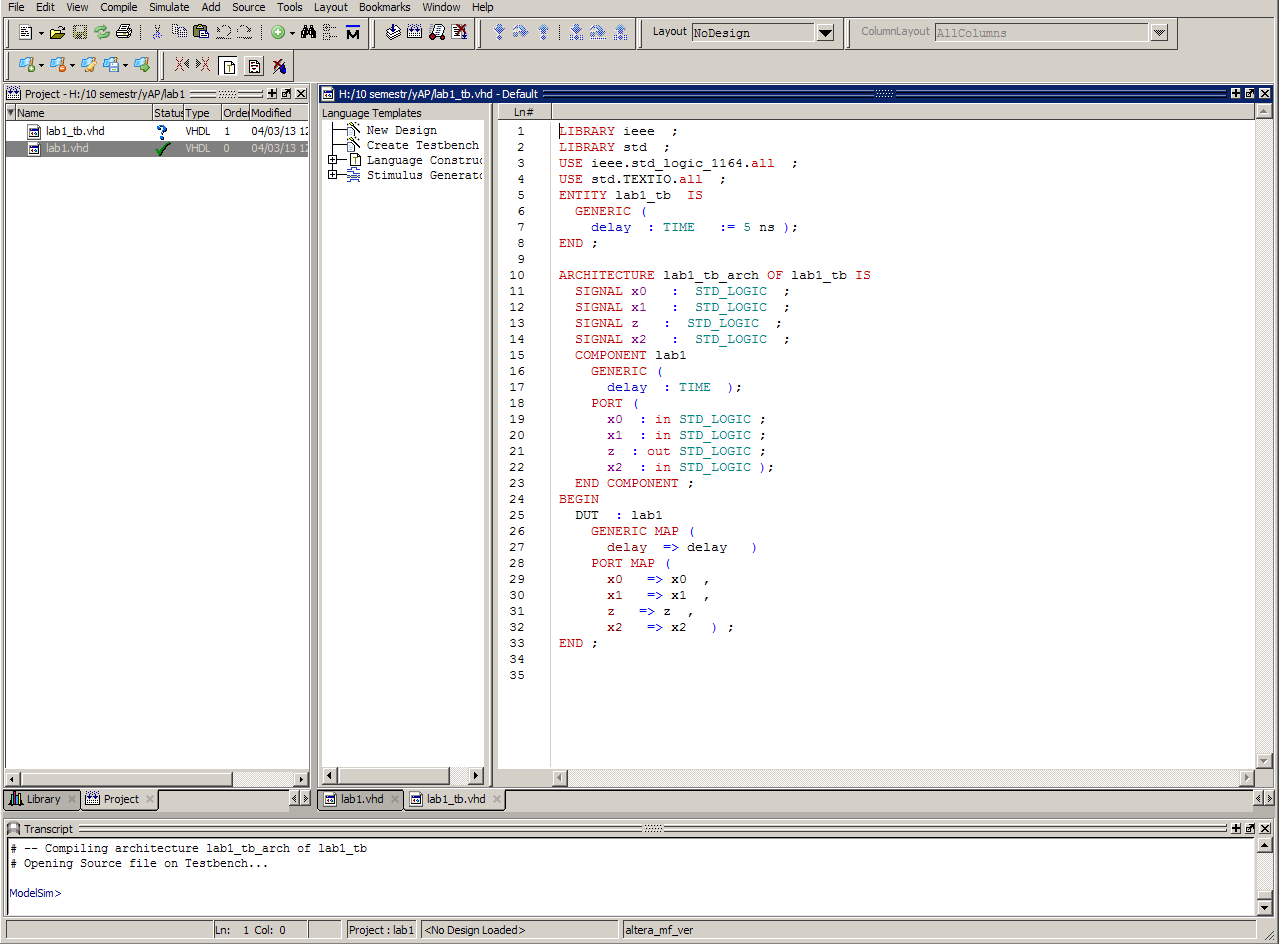

Для проверки функциональности нашего устройства требуется создать испытательный стенд. В результате в теле архитектуры было объявлено наше устройство и к нему подключены все необходимые сигналы.

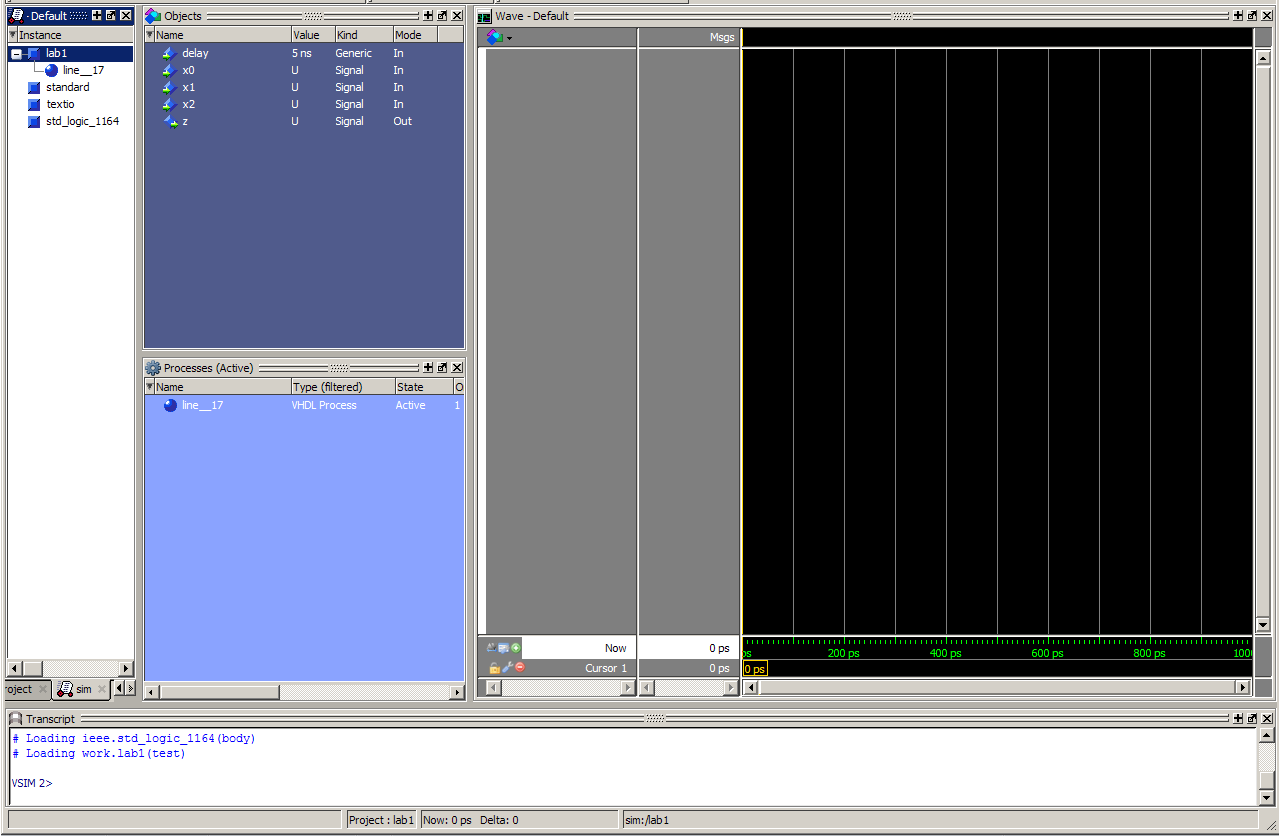

Производим загрузку готового проекта в систему моделирования.

Задаем тестовую последовательность командой force x0 0 0, 1 25 -repeat 50. После этого запускаем симуляцию на 100ns: run 100ns