- •2013 Оглавление

- •Общая архитектура процессоров Базовая структура

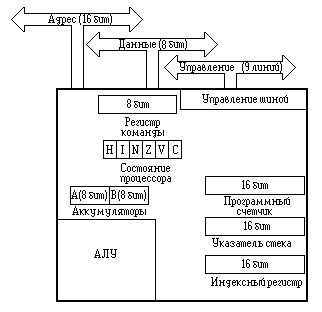

- •Архитектура микропроцессора

- •Обзор архитектур микропроцессоров

- •Регистровая программная модель

- •Устройство управления

- •Особенности программного и микропрограммного управления

- •Команды микропроцессора

- •Режимы адресации

- •Тенденции развития архитектуры микропроцессоров

Обзор архитектур микропроцессоров

Выделяют 2 типа архитектур:

CISC, которая характеризуется полным набором команд

RISC, которая определяет систему с сокращенным набором команд одинакового формата и выполняемых за один такт

CISC

Процессор имеет полный набор команд. Архитектура характеризуется следующим набором свойств:

нефиксированное значение длины команды

арифметические действия кодируются в одной команде

небольшое число регистров, каждый из которых выполняет строго определённую функцию

Формально все х86 процессоры до Pentium Pro являются CISC, к ним же относится Motorola МС6800.

У данной архитектуры есть несколько явных недостатков:

высокая стоимость аппаратной части

сложности с распараллеливанием вычислений

RISC

Процессор имеет сокращенный набор команд. Архитектура характеризуется следующим набором свойств:

фиксированная длина машинных инструкций

специализированные команды чтения и записи для операций с памятью

большое количество регистров общего назначения

отсутствие микропрограмм внутри самого процессора

У данной архитектуры есть несколько явных недостатков:

на выполнение ряда функций требуется потратить несколько команд

удлинение кода программы

увеличение загрузки памяти

В большинстве случаев в микроконтроллерах разных устройств используется RISC архитектура.

Если определить в качестве основной характеристики разрядность, то есть 2 типа:

с фиксированной разрядностью и списком команд (однокристальные);

с наращиваемой разрядностью (секционные) и микропрограммным управлением.

Анализируя адресные пространства программ и данных, можно определить микропроцессоры с архитектурой фон Неймана, где память программ и память данных находятся в едином пространстве и нет никаких признаков, указывающих на тип информации в ячейке памяти. Вторая архитектура Гарвардской лаборатории, где память программ и память данных разделены, имеют свои адресные пространства и способы доступа к ним.

Давайте более подробно рассмотрим основные типы архитектурных решений, выделяя связь со способами адресации памяти.

Регистровая программная модель

Данные можно хранить не только в ячейках оперативной памяти, но и в регистрах. Регистры располагаются в самом процессоре, как следствие доступ к ним осуществляется намного быстрей, чем к ячейкам памяти. В результате выполнение программы происходит заметно быстрей.

Команды получают возможность обратиться к операндам, расположенным в одной из двух запоминающих сред - оперативной памяти или в регистрах.

Размер регистра обычно фиксирован и совпадает с размером слова (16 разрядов). К любому регистру можно обратиться непосредственно, поскольку регистры представлены в виде массива запоминающих элементов. Типичным является выполнение арифметических операций только в регистре, при этом команда содержит два операнда:

оба операнда находятся в регистре

один операнд в регистре, а второй в оперативной памяти.

За каждым регистром закреплено определенное имя. По назначению и способу использования они делятся на группы:

регистры общего назначения: AX, BX, CX, DX, SI, DI, BP, SP

сегментные регистры: CS, DS, SS, ES

указатели команд: IP

регистр флагов: Flags

АХ

– аккумулятор

АХ

– аккумулятор

BX – база

СХ – счетчик

DX – данные

SI – индекс источника

DI – индекс приемника

BP – указатель базы

SP – указатель стека

IP – указатель команды

SS – сегмент стека

DS – сегмент данных

CS – сегмент команд

ES – дополнительный сегмент

Регистры общего назначения можно использовать в любых арифметических, логических и других машинных операциях. Каждый из них имеет определенную специализацию: некоторые команды требуют, чтобы их операнд или операнды обязательно находились в определенных регистрах.

Сегментные регистры не участвуют в арифметических и логических операциях. Они используются для сегментирования адресов, которое является разновидностью модификации адресов и которое используется для сокращения размера команд.

В регистре указателя команд находится адрес команды, которая будет выполнена после завершения текущей.

Регистры флагов делятся на две группы: флаги условий и флаги состояний. Каждый такой регистр занимает 1 бит и принимает значение 1 (флаг установлен) или 0 (флаг сброшен).

Например, в i8086 таких флагов 9, все они собраны в 16-разрядный регистр Flags.

CF – флаг переноса, OF – флаг переполнения, ZF – флаг нуля, SF – флаг знака, PF – флаг четности, AF – флаг дополнительного переноса, DF – флаг направления, IF – флаг прерываний, TF – флаг трассировки.

Также к данному типу архитектуры можно отнести микропроцессор фирмы Zilog. Процессор Z80 имел расширенную систему команд, один номинал питания и способности исполнять программы, написанные для i8080.

В дополнение к основному набору РОН, в кристалле был реализован второй комплект регистров. Это значительно упрощало работу при вызове подпрограмм или процедур обслуживания прерываний, поскольку можно было использовать для них альтернативный набор регистров, избегая сохранения в стеке содержимого РОНов для основной программы с помощью операций PUSH. Кроме того, в систему команд был включен ряд инструкций, ориентированных на обработку отдельных битов. МП Z80 применялся в системах Sinclair ZX, Sinclair Spectrum.

Микропроцессор фирмы Motorola имел ряд преимуществ. Кристалл МС6800 требовал для работы одного номинала питания, а система команд оказалась весьма прозрачной. Архитектура также имела ряд особенностей.

МС6800 содержал 2 аккумулятора, и результат операции АЛУ мог быть помещен в любой из них. У МП было реализовано автоматическое сохранение в стеке содержимого всех регистров процессора при обработке прерываний. Кстати процедура восстановления РОН из стека тоже выполнялась аппаратно.

2. Стековая архитектура дает возможность создать поле памяти с упорядоченной последовательностью записи и выборки информации. В общем случае команды неявно адресуются к элементу стека, расположенному на его вершине, или к двум верхним элементам стека.

3. Архитектура, ориентированная на оперативную память, обеспечивает высокую скорость работы и большую информационную емкость регистров и стека. Но это возможно, если они организуются в оперативной памяти.

Архитектура этого типа не предполагает явного определения аккумулятора, регистров общего назначения или стека. Все операнды команд адресуются к области основной памяти.

С точки зрения важности для пользователя под архитектурой в общем случае понимают совокупность следующих компонентов и характеристик:

разрядности адресов и данных;

состава, имен и назначения программно-доступных регистров;

форматов и системы команд;

режимов адресации памяти;

способов машинного представления данных разного типа;

структуры адресного пространства;

способа адресации внешних устройств и средств выполнения операций ввода/вывода;

классов прерываний, особенностей инициирования и обработки прерываний.