лаб_4_сумматор / DisLaba4OTChET

.docxЦель работы: ознакомление с устройством и принципами функционирования арифметического сумматора.

Порядок выполнения работы:

-

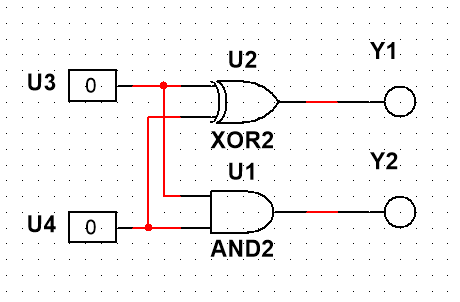

Собрать в Multisim логическую схему полусумматора (рисунок 1)

-

Подключить входы и выходы логических элементов, запустить моделирование и проверить соответствие работы схемы полусумматора и его таблицы функционирования (таблица 1)

-

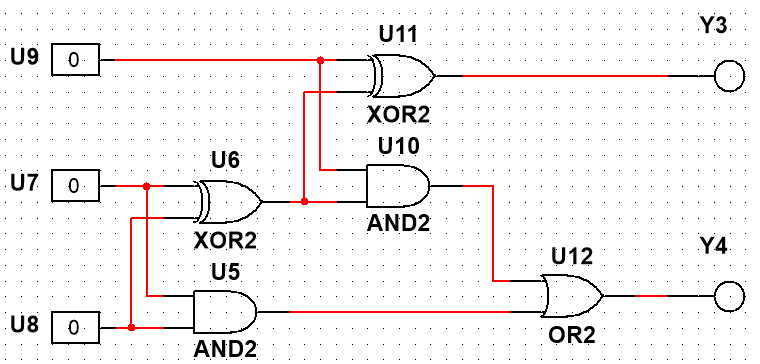

Собрать логическую схему полного сумматора (рисунок 2). Изучить его работу

-

Соединить четыре сумматора в единую схему 4-разрядного сумматора. Проверить работоспособность собранной схемы

Полусумматор

Рис.1

Логическая схема

Рис.2 Условное обозначение

Табл.1 Таблица функционирования

|

A |

B |

S |

C |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

Полный

сумматор

Рис.3 Логическая схема

Рис.4 Условное обозначение

Табл.2 Таблица функционирования

|

Ai |

Bi |

Ci |

Si |

Ci+1 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

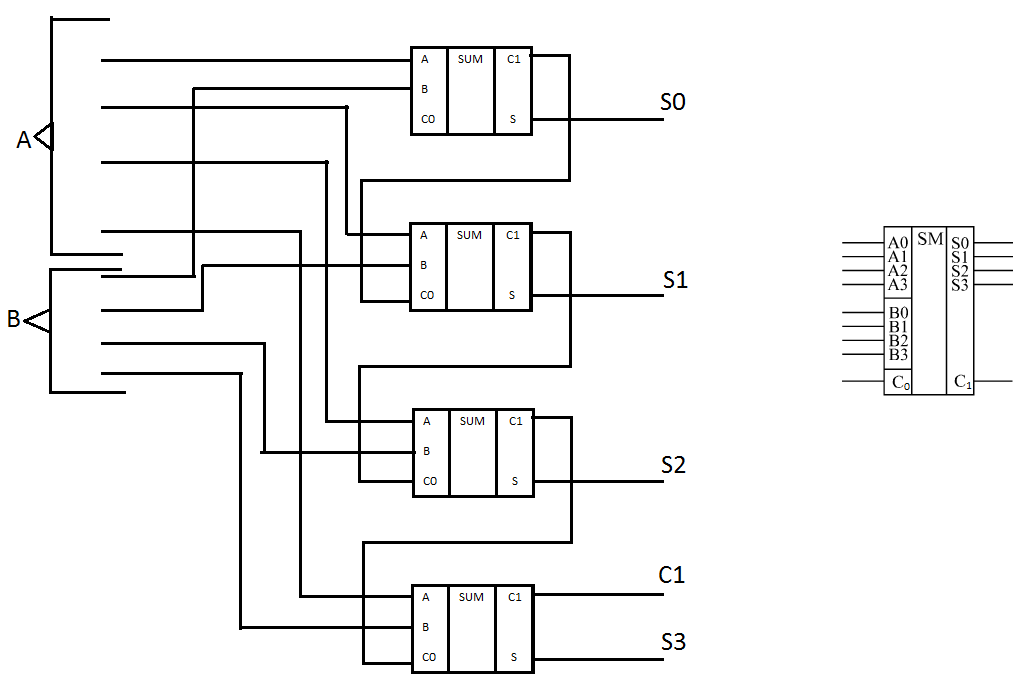

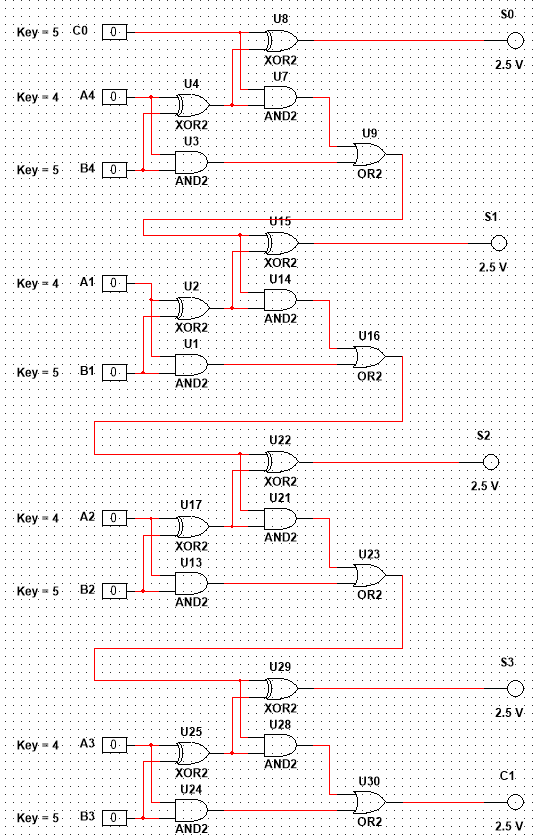

Четырех разрядный сумматор

Рис.5 Схема соединения и условное обозначение

Рис.6 Схема в Multisim

Ответы на вопросы:

1) Что такое полусумматор и сумматор? В чем их отличия?

Полусумматор – комбинационное логическое устройство, имеющее два входа и два выхода, реализующее операцию суммирования без учета переноса данных из соседнего младшего разряда.

Сумматор – логическое комбинационное устройство, выполняющее операцию арифметического сложения двоичных чисел.

Полусумматор отличается от полного сумматора тем, что не имеет входа переноса из предыдущего разряда

2) Какие логические элементы используются для построения полусумматора и какие выходные сигналы формирует каждый элемент? (???)

XOR – исключающее или; S

AND – и; C

3) Каким образом соединить сумматоры для увеличения разрядности?

Помимо выходных разрядов суммы и выхода переноса, сумматоры имеют вход расширения (другое название - вход переноса) С для объединения нескольких сумматоров с целью увеличения разрядности. Если на этот вход приходит единица, то выходная сумма увеличивается на единицу, если же приходит нуль, то выходная сумма не увеличивается. Если используется одна микросхема сумматора, то на ее вход расширения С необходимо подать нуль.

4) Что определяет быстродействие работы многоразрядного сумматора?

Задержка передачи сигнала переноса от младшего разряда к старшему.

5) Какие способы повышения быстродействия многоразрядного сумматора вы знаете?

Параллельное суммирование с последовательным переносом