Классификация

архитектур вычислительных систем

Ha |

|

M |

N |

d |

|

|

a |

|

de |

Автор - Никитин А.А.

Общие принципы функционирования |

Наиболее важные параметры |

||||

|

Введение |

|

• |

топология связи между |

|

|

параллельных машин |

|

|

• |

организация памяти |

• |

векторно-конвейерные |

|

|

|

|

• |

массивно-параллельные |

|

|

|

процессорами |

• компьютеры с широким командным |

• |

синхронность работы |

|||

|

словом |

|

|

|

отдельных устройств |

• |

систолические массивы |

|

|

• |

способ исполнения |

• |

гиперкубы |

Основной вопрос - что |

|

арифметических операций |

|

• |

спецпроцессоры |

|

заложить в основу |

|

|

• |

мультипроцессоры |

|

классификации |

|

|

• |

стоимость компьютера |

|

|

||

• |

иерархические |

|

Правильная классификация |

||

• |

потоки данных и команд |

|

|||

• |

кластерные компьютеры |

|

помогает: |

||

• |

пословный и поразрядный |

• разобраться с тем, что |

|||

• |

dataflow |

|

параллелизм |

|

представляет собой каждая |

• |

матричные ЭВМ |

|

|

|

архитектура |

• понять как архитектуры

Классификация•облегчать пониманиемнениютого, чтоСкилликорнадостигнуто должна : взаимосвязаны между собой

сегодняшний день в области архитектур вычислительных систем, и какие архитектуры имеют лучшие перспективы в будущем;

•подсказывать новые пути организации архитектур - речь идет о тех классах, которые в настоящее время по разным причинам пусты;

•показывать, за счет каких структурных особенностей достигается увеличение производительности различных вычислительных систем; с этой точки зрения, классификация может служить моделью для анализа производительности.

Классификация

Флинна

d |

|

|

|

|

|

|

|

|

|

|

|

ata |

|

|

|

|

|

|

|

|

|

к |

|

fl |

|

|

|

|

|

|

||

онве |

ow и |

вект |

|

|

||||||

|

йе |

р |

ор |

н |

||||||

прол |

|

|

|

|

|

|||||

е |

|

|

ные |

м |

|

|

|

|||

|

|

тают |

|

аши |

||||||

|

|

|

|

|

||||||

самая ранняя и наиболее |

Классификация базируется на понятии потока |

известная классификация |

- последовательности элементов |

|

обрабатываемых процессором |

Конвейерные машины

пуст

MISD - множественный поток команд и одиночный поток

данных. Мультипроцессорные системы

BBN Butterfly |

переполнен |

различными |

|

Intel Paragon |

архитектурам |

и |

MIMD - множественный поток команд и множественный поток данных.

Однопроцессорные

последовательные

компьютеры VAX 11/780

CRAY-1

SISD - одиночный поток команд и одиночный поток данных

|

|

|

|

|

ы |

р |

|

||

|

|

|

иц |

с |

ILLIAC IV |

||||

|

|

р |

|

|

с |

о |

|||

|

т |

|

|

е |

|

|

ICL DAP |

||

а |

|

|

ц |

|

|

|

|||

М |

|

|

о |

|

|

|

|

|

|

|

р |

в |

|

|

|

|

|||

|

п |

|

|

|

|

|

|||

|

|

|

о |

|

|

|

|

|

|

SIMD - одиночный поток команд и множественный поток данных.

Патч для архитектуры Флинна

Дополнения Ванга и Бриггса

Схема классиф |

|

|

ик |

|

ации на |

при |

иб |

олее |

|

|

ме |

|

нима при оценке |

|

б |

п |

азовых |

ри |

|

нц |

|

|

ипов р |

|

аб |

|

от |

|

ы к |

|

ом |

|

пь |

|

ют |

|

ера. |

Детализирует классы архитектур SIMD,SISD,MIMD

Класс SISD разбивается на два |

В классе MIMD авторы различают |

|

|||||||||||||||||||||||||||

• вычислительные системы со |

|

|

|||||||||||||||||||||||||||

подкласса: |

|

|

|||||||||||||||||||||||||||

слабой связью между |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

• архитектуры с |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

процессорами, к которым они |

|

|

|||||||||||||||||||||||||||

единственным |

|

|

|||||||||||||||||||||||||||

относят все системы с |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

функциональным |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

распределенной памятью, |

|

|

|

|

|||||||||||||||||||||||||

устройством, например, PDP- |

|

|

|

|

|||||||||||||||||||||||||

например, Cosmic Cube, |

|

|

|

|

|

|

|

||||||||||||||||||||||

11; |

|

|

|

|

|

|

|

||||||||||||||||||||||

• и вычислительные системы с |

|

|

|||||||||||||||||||||||||||

• архитектуры, имеющие в |

|

|

|||||||||||||||||||||||||||

сильной связью (системы с общей |

|

||||||||||||||||||||||||||||

своем составе несколько |

|

||||||||||||||||||||||||||||

памятью), куда попадают такие |

|

||||||||||||||||||||||||||||

функциональных устройств - |

|

||||||||||||||||||||||||||||

компьютеры,П |

как C.mmp, BBN |

|

|

|

|||||||||||||||||||||||||

CDC 6600, CRAY-1, FPS AP-120B, |

|

|

|

|

у |

сто |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

Butterfly, CRAYд |

Y-йMP,кл Denelcor HEP. |

|

||||||||||||||||||||||||||

В класс SIMD вводится два подкласса: |

|

|

л |

я р |

|

|

|

|

а |

сс |

|

|

|

|

|

|

|

|

|

||||||||||

CDC Cyber 205, FACOM 200. |

|

|

|

|

|

|

|

|

|

|

|

M |

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

з |

р |

|

|

|

|

|

|

|

I |

|

|

|

|

|

||

•архитектуры с пословно- |

|

|

при |

|

|

|

|

|

або |

|

|

|

|

|

S |

|

|

|

|

||||||||||

|

|

нц |

|

|

|

|

|

|

|

|

|

D п |

ол |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

ип |

|

|

|

тк |

и |

|

|

|

|

ез |

||||||||||

последовательной обработкой |

|

|

кон |

|

|

|

|

|

|

|

|

|

иал |

|

|

|

|

|

|

|

|

|

|

|

е |

||||

|

|

ц |

е |

пц |

|

ь |

н |

о |

н |

|

|

|

|

н |

|||||||||||||||

информации - ILLIAC IV, PEPE, BSP; |

пра |

|

|

|

|

|

ов |

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

к |

т |

|

|

ий в |

т |

|

|

|

|

ы |

|

|

|

||||||||||||||||

|

|

в |

|

|

|

|

|

ике |

|

|

|

|

|

|

|

|

|

х |

|

|

|||||||||

•архитектуры с разрядно- |

|

ыч |

|

|

|

|

|

|

|

|

по |

|

|

|

еор |

|

|

|

|

|

|||||||||

|

|

и |

с |

|

|

|

|

|

с |

|

|

|

|

|

|

ии |

и |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

т |

рое |

|

|

|

|

|

|

||||||||

последовательной обработкой - |

|

|

|

|

|

|

|

лит |

|

|

|

|

|

ния |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

ель |

ны |

|

|

|

|

|

|

|||||||||||

STARAN, ICL DAP. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

х |

сис |

|

|

|

|

||||

Классификация |

Л |

|

|

|

|

|

|

|

||||||||||||||||||||||

ю |

|

|

|

|

|

|

||||||||||||||||||||||||

|

бая |

|

|

|

|

|

||||||||||||||||||||||||

|

|

В |

|

|

|

|

||||||||||||||||||||||||

|

|

|

С |

- точка на |

|

|

|

|||||||||||||||||||||||

плоскости |

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(n, |

m) |

|

|

с коо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

рина |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

та |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

м |

|

Интегральная характеристика |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

и |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Классификация вычислительных систем на основе |

|||||||||||||||||

|

|

Фенга |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

потенциала параллельности P - |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

двух простых характеристик |

|

|

|

|

|

||||||||||

максимальная степень параллелизма |

|

|

|

|

|

|

• Число бит n в машинном слове, обрабатываемых |

|||||||||||||||||||||||

|

|

В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

параллельно при выполнении машинных |

|

|

|

|||||||

ВС P(C)=mn , это некоторый аналог |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

с |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

инструкций |

|

|

|

|

|

|

|

|

||

пиковой |

|

|

е |

ы. |

чи |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

• числу слов m, обрабатываемых одновременно |

|

|

||||||||||||||

|

|

н |

|

м |

|

|

сли |

т |

|

|

|

|

|

|

|

|

|

|||||||||||||

|

производительности ы |

|

|

|

|

|

е |

л |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

а |

че |

т |

|

мо |

ж |

|

|

|

ьн |

ы |

е |

|

данной вычислительной системой |

|

|

|

||||||||||||

|

|

|

|

|

|

к |

|

но р |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

Разрядно-последовательные |

ыре |

|

|

|

|

|

|

|

Функционирование любого компьютера |

|||||||||||||||||||||

|

|

|

|

ла |

с |

с |

|

азд |

е |

л |

и |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

пословно-последовательные |

|

|

|

|

|

|

|

|

|

а : |

|

|

|

|

|

тьможно представить как параллельную |

|

|||||||||||||

(n=m=1). В каждый момент |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

обработку n битовых слоев, на каждом |

|

|||||||||||||

времени |

такие |

компьютеры |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

из которых независимо преобразуются |

|

|||||||||||

обрабатывают |

только |

|

один |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

m бит. |

|

|

|

|

|

|

|

|

|||

|

|

|

Разрядно-параллельные пословно- |

|

|

|

|

|||||||||||||||||||||||

двоичный разряд. MINIMA (1,1) |

|

|

параллельные (n > 1, m > 1). Большая |

|

|

|

||||||||||||||||||||||||

Разрядно-параллельные |

|

|

|

|

|

|

часть существующих параллельных |

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

вычислительных систем BBN Butterfly (32, |

|

|

|

|||||||||||||||||||||

пословно-последовательные |

|

|

|

|

256) , |

ILLIAC IV (64, 64). |

|

|

|

|

|

|

|

|

||||||||||||||||

(n > 1 , m = 1). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Недостатки |

|

|

|

|

|

|

|

|

||

Последовательные |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-процессорные матрицы = векторно- |

|

|

|

||||||||

компьютеры : |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

конвейерные = многопроцессорные |

|

|

|

|||||||

IBM 701 (36,1) ; VAX 11/780 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

системами |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-не исследуется за счет чего можно |

|

|

|

||||||||||

Разрядно-последовательные пословно- |

|

|

|

|

|

|

|

|

||||||||||||||||||||||

(32,1). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

одновременно обрабатывать более одного |

|||||||||

параллельные (n = 1 , m > 1). Много |

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

слова. |

|

|

|

|

|

|

|

|

|||||||||||||||

одноразрядных процессоров, каждый |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

Достоинство - введение единой числовой |

|||||||||||||||||||||||

независимо обрабатывает данные. |

|

|

|

|

|

|

|

|

|

|

метрики для всех типов компьютеров |

|

|

|||||||||||||||||

Классификация |

осущоркаи |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ВыделениеШора |

|

б |

|

|

|

|

|

|

|

|

|

|

ов |

|

|

ны |

|

|

||||||||||

|

е |

|

|

|

з |

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

с |

|

|

|

|

п |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

т |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

в |

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

л |

|

|

|

|

|

м |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

я |

|

|

|

|

|

я |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

т |

|

|

|

|

т |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

ь |

|

|

|

|

и |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

с |

|

|

|

|

|

|

|

|

|

|

|

|||

типичных способов компоновки |

|

|

|

|

|

|

|

|

я |

сл |

|

|

д |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

ан |

х |

|

|

||||||||||||

вычислительных систем на основе фиксированного |

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

м |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ми |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

о |

||

числа базисных блоков: устройства управления, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ж |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ет |

|||||||||

арифметико-логического устройства, памяти команд и |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

памяти данных. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

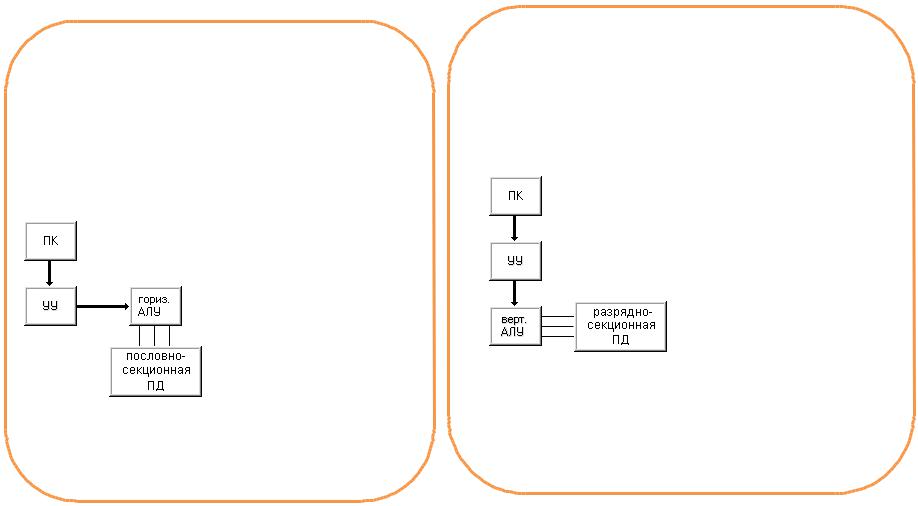

Машина I - это вычислительная |

Машина II осуществляет выборку |

|

|

|

|

|||||||||||||||||||||||

система, которая содержит |

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

устройство управления, арифметико- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

одного разряда из всех слов. Слова в памяти |

||||||||||||||||||||||||||||

логическое устройство, память |

||||||||||||||||||||||||||||

данных располагаются горизонтально. |

|

|||||||||||||||||||||||||||

команд и память данных с пословной |

|

|||||||||||||||||||||||||||

Доступ к словам идет через |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

выборкой. Считывание данных |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

последовательную обработку битовых слоев |

||||||||||||||||||||||||||||

осуществляется выборкой всех |

||||||||||||||||||||||||||||

при параллельной обработке множества |

|

|||||||||||||||||||||||||||

разрядов некоторого слова для их |

|

|||||||||||||||||||||||||||

слов. |

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|||||||||

параллельной обработки в |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TA |

R |

|

|

|

|

|

|

|

||||||

I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

N |

|

|

|

|

||||

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

арифметико-логическом Mустройстве. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

7 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

|

|

|

||

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

L |

|

|

|

|

|

|

|

|

|

|

||

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

||||

|

|

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P |

|

|

|

|

|||

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

ассоциативные компьютеры

классические последовательные Матричные системы машины конвейерные скалярные машины

векторно-конвейерные машины

Классификация Шора

Если объединить принципы построения машин I и II, то получим машину III. Эта машина имеет два арифметико- логических устройства - горизонтальное и вертикальное, и модифицированную память данных, которая обеспечивает доступ как к словам, так и к битовым слоям.

Если в машине I увеличить число пар арифметико-логическое устройство <==> память данных (иногда эту пару называют

процессорным элементом) то получим

машину IV. Единственное устройство управления выдает команду за командой сразу всем процессорным элементам. С одной стороны, отсутствие соединений между процессорными элементами делает дальнейшее наращивание их числа относительно простым, но с другой, сильно ограничивает применимость машин этого класса.

Вычислительные системы семейства |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

OMEN-60 фирмы Sanders Associates, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

построенные в прямом соответствии с |

|

|

|

|

|

Такую структуру имеет |

||||||||||||||||||||||||

концепцией ортогональной машины. |

|

|

|

|

|

|

||||||||||||||||||||||||

Ес |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вычислительная система PEPE, |

|||||||

ли па |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

объединяющая 288 процессорных |

||||||||||||

|

|

|

|

|

|

мя |

|

|

|

пре |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

сло |

|

|

|

|

|

ть |

дставля |

|

|

|

|

элементов. |

||||||||||||||||||

в, то дос |

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

ту |

п к |

да |

|

ть как ма |

т |

рицу |

|||||||||||||||||||||

в напр |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

ав |

ле |

ни |

и, " |

|

|

|

нным ос |

у |

щес |

т |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

ор |

т |

|

|

|

|

|

|

|

|

|

вля |

ет |

|||||

т |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ся |

|

радицион |

но |

|

|

|

|

|

ог |

ональном" |

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

а по |

б |

итовы |

м |

м |

у - не |

по сл |

о |

вам (с |

т |

|

|

|

|

|||||||||||||||||

|

|

|

|

сло |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

рока |

м), |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ям (сто |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

лб |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ца |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

м) |

|

|

|

|

|

|

|

Классификация Шора

Если ввести непосредственные линейные связи между соседними процессорными элементами машины IV, например в виде

матричной конфигурации, то получим схему машины V. Любой

процессорный элемент теперь может обращаться к данным как в своей памяти, так и в памяти непосредственных соседей.

Классический матричный компьютер ILLIAC IV

Заметим, что все машины с I-ой по V-ю придерживаются концепции разделения памяти данных и арифметико-логических устройств, предполагая наличие шины данных или какого-либо коммутирующего элемента между ними. Машина VI, названная

матрицей с функциональной памятью

(или памятью с встроенной логикой), представляет собой другой подход, предусматривающий распределение логики процессора по всему запоминающему устройству.

простые ассоциативные запоминающие устройства

сложные ассоциативные процессоры

|

Три уровняКлассификацияобработки данных в |

|

|

|

|

|

д |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

е |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

т |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

л |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

иза |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ц |

|

|

|

|

|

|

|

|

|

|

|

|

||

процессе выполнения программ: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

и |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

я |

Ф |

|

|

|

|

|

||||||||

• |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

уровень выполнения программы - |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

е |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

н |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

г |

|

|

|

|

|

основа классификации - явное описаниеа |

|

||||||||||||||||||||||||||||||

|

|

Хендлера |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

опираясь на счетчик команд и |

возможностей параллельной и |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

некоторые другие регистры, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

конвейерной обработки информации |

|

|

|

|||||||||||||||||||||||||||||||

устройство управления (УУ) производит |

|

|

|

|||||||||||||||||||||||||||||||

вычислительной системой |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

выборку и дешифрацию команд |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

способы связи между процессорами и |

|

|

||||||||||||||||||||||||||||||||

программы; |

|

блоками памяти не рассматриваются |

|

|

|

|||||||||||||||||||||||||||||

• уровень выполнения команд - |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

арифметико-логическое устройство |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

компьютера (АЛУ) исполняет команду, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

выданную ему устройством |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

управления; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

• уровень битовой обработки - все |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

элементарные логические схемы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

процессора (ЭЛС) разбиваются на |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

группы, необходимые для выполнения |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

операций над одним двоичным |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Тройка для описания вычислительной |

Исчезает проблема с определени |

|||||||||||||||||||||||||||||||||

разрядом. |

|

|||||||||||||||||||||||||||||||||

системы C: |

|

векторно-конвейерных машин |

|

|||||||||||||||||||||||||||||||

|

t(С) = (k×k',d×d',w×w') , где |

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

( |

I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

LL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

исло процессоров (каждый со своим УУ), работающих параллельноt( S |

|

|

C |

IV ) |

= |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

|

|

( |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

A |

R |

|

|

|

|

|

|

|

1 |

, |

|

|

|

|

|

|

|

|

|

||||||

глубина макроконвейера из отдельных процессоров |

t( C |

|

|

|

|

|

A |

N ) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

= |

(1,8 |

64,6 |

4) |

|

|

||||||||||||||||||||||

исло АЛУ в каждом процессоре, работающих параллельно |

t( P |

|

.mmp |

|

192, |

|

|

|

||||||||||||||||||||||||||

RI |

|

|

|

|

|

|

) = |

( |

|

|

|

|

|

1 |

) |

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16,1, |

|

|

|

|

|

|||||||||||||

число функциональных устройств АЛУ в цепочке |

t( |

B |

|

|

|

ME ) |

= |

( |

|

|

16) |

|

|

|

|

|||||||||||||||||||

BN B |

|

|

|

5,1,16 |

|

|

|

|

|

|

||||||||||||||||||||||||

число разрядов в слове, обрабатываемых в АЛУ параллельно |

|

utter |

|

) |

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

fl |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

число ступеней в конвейере функциональных устройств АЛУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P |

100 |

0(256 |

, |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

~ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

е |

|

|

|

|

|

|

|

|

и |

|

т |

|

|

|

|

||

|

|

|

|

|

а |

|

|

|

|||

лассификация Хокни |

|

|

я |

|

|

л |

|

|

|||

Ф ии |

|

ифи |

|

||||||||

|

|

|

|

|

|

|

|

|

и |

|

|

|

|

к |

|

|

|

|

|

|

з |

|

|

|

|

|

|

|

|

|

|

а |

|||

|

|

|

л |

|

|

|

|

|

|

ц |

|

|

|

ц |

|

а |

|

|

|

|

|

|

|

|

|

|

|

с |

|

|

|

|

|

||

|

|

л |

|

|

|

с |

|

|

|

к |

|

систематизации компьютеров, |

|

|

|

|

|

|

|

|

|

||

|

и |

|

|

|

|

|

|

|

|||

|

|

|

н |

|

|

|

|

|

|

||

попадающих в класс MIMD по |

|

|

|

н |

|

|

|

|

|

||

|

|

|

|

а |

|

|

|

|

|

||

систематике Флинна. |

машины с переключателем |

|

|

||||||||

Множественный поток команд может быть

обработан двумя способами: |

|

-одним конвейернымMMIоК |

|

устройством обработки,Dенв |

|

работающем в режимеей |

|

памят ь рас среди проц ессоров как их локаль ная |

|

разделения времени |

пределена |

ны |

|

для отдельных потоков е

-каждый поток обрабатывается своим собственным

•ВС, где возможна прямая связь каждого

устройством

процессора с каждым, реализуемая с помощью

переключателя;

•ВС, где прямая связь каждого процессора возможна

только с ближайшими соседями по сети, взаимодействие удаленных процессоров

через процессоры-посредники.

|

|

M -память распределена |

|

|

|

|||

|

S |

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

P |

|

|

среди процессоров как |

|

|

|||

|

|

|

их локальная |

|

|

|

|

|

|

|

|

память |

|

|

|

|

|

|

|

|

-память это |

|

|

|

|

P |

|

|

|

разделяемый ресурс, |

|||||

|

|

|

доступный всем |

|

X |

- |

M |

|

|

|

|

|

|

|

|

||

|

|

|

процессорам черезY |

|

|

|||

|

|

|

переключательR |

A |

|

|

|

|

|

|

|

-гибридные ВСC |

|

|

|

|

|

Машины с сетевой структурой систематизируются в соответствии с топологией сети

-звездообразная сеть (lCAP) -гиперкубы (NCube, Intel iPCS) -кластеры (Cm* , CEDAR)

|

|

|

|

|

е |

|

|

|

|

|

|

|

и |

|

т |

|

|

|

|

||

|

|

|

|

а |

|

|

|

|||

|

|

|

я |

|

|

л |

|

|

||

лассификация ДжонсонаФ ии |

|

ифи |

|

|||||||

|

|

|

|

|

|

|

|

и |

|

|

|

к |

|

|

|

|

|

|

з |

|

|

|

|

|

|

|

|

|

а |

|||

|

|

л |

|

|

|

|

|

|

ц |

|

|

ц |

|

а |

|

|

|

|

|

|

|

|

|

|

с |

|

|

|

|

|

||

|

л |

|

|

|

с |

|

|

|

к |

|

классификацию MIMD архитектур на основе структуры памяти и |

и |

|

|

|

|

|

|

|

|

|

|

нн |

|

|

|

|

|

||||

реализации механизма взаимодействия и синхронизации между |

|

|

|

а |

|

|

|

|

|

|

процессорами

По структуре оперативной памяти существующие вычислительные системы делятся на две большие группы:

системы с общей памятью, прямо адресуемой всеми

процессорами Четыре класса MIMD архитектур, уточняющихсистемы с распределенной

систематику Флинна:

памятью, каждая часть общая память - разделяемые переменные (GMSV);

•

которой доступна только

• распределенная память - разделяемые переменные одному процессору. (DMSV);

• распределенная память - передача сообщений (DMMP);

• общая память - передача сообщений (GMMP). Вычислительные системы, использующие Системыобщую с распределенной памятью и

разделяемую память для межпроцессорногосинхронизацией через разделяемые взаимодействия и синхронизации - системамипеременные,с как в BBN Butterfly, разделяемой памятью, например, CRAY Y-MPназываются(I) гибридными архитектурами

(II)

Для уточнения классификации существует возможность учитывать вид связи между процессорами: общую шину, переключатели, разнообразные сети.

кор |

|

|

|

|

|

|

|

|

|

|

|

е |

|

|

|

|

|

|

|

|

|

|

н |

|

|

|

|

|

|

|

|

|

Классификация Базу |

|

ь де |

р |

|

|

|

|

|||

с |

ис |

т |

ем |

|

|

ева |

- |

вы |

ч |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|||||

|

|

|

а |

|

|

|

ис |

литель |

||

|

|

|

|

|

|

|

|

|||

Любую параллельную вычислительную систему можно однозначно описать последовательностью решений, принятых на этапе ее проектирования, а сам процесс проектирования представить в виде дерева

Систолические деревья, введенные Кунгом для вычисления арифметических выражений могут быть описаны как OCP S либо IBM 360/91, Amdahl 470/6

OCP A

и многиеa современные RISC процессоры, разбивающие исполнение всех инструкций на несколько этапов, в данной

классификации имеют Data-flow компьютеры, в обозначение OPP S зависимости от i

особенностей реализации, могут быть описаны либо как OPPiA,

либо OPPaA.

|

|

Классификация |

а |

|

|

|

|

нал |

ог Баз |

||

|

|

|

Векторно-конвейерные |

у |

|

|

|

|

компьютеры: |

|

|

для |

классификации параллельных вычислительных |

|

|

||

|

Кришнамарфи•гранулярность - на уровне |

||||

|

предлагает использовать четыре |

|

|

|

|

1.системпень гранулярности; |

данных; |

|

|

||

характе ист ки |

|

|

|||

2.способ реализации |

• |

|

|

||

параллелизма; |

реализация параллелизма - |

||||

аппаратная; |

|

|

|||

3.топология и природа связи |

|

|

|||

• |

|

|

|||

процессоров; |

связь процессоров - простая |

||||

топология со средней |

|

||||

4. способ управления |

|

||||

связностью; |

|

|

|||

процессорами. |

|

|

|||

• способ управления - |

|

||||

Несмотря на то, что |

|

||||

синхроннй. |

|

|

|||

классификация Е. Кришнамарфи |

|

|

|||

|

|

|

|||

построена лишь на четырех |

|

|

|

||

признаках, она позволяет |

|

|

|

||

выделить и описать такие |

|

|

|

||

"нетрадиционные" |

|

|

|

||

параллельные системы, как |

|

|

|

||

систолические массивы, машины |

|

|

|

||

типа dataflow |

wavefront. |

|

|

|

|

Можно расширить |

|

|

классификацию если |

|

|

Дополнить ее размещением |

|

|

задач по процессорам, способом |

|

|

маршрутизации сообщений, |

|

|

возможностью реконфигурации, |

Гиперкубы и ассоциативные процессо |

|

аппаратной поддержки языков |

||

Определяются неоднозначно |

||

программирования |

||

|

|

|

о |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

ч |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Классификация Скилликорна |

|

|

е |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

сиф аяп |

|

|

|

|

|

|

|

|

|

|||||||

|

|

к |

|

|

р |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

е |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

л |

|

|

|

д |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

а |

|

|

|

н |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

с |

|

|

и |

|

о |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

к |

|

|

п |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

ы |

|

|

|

|

|

|||

Классификация состоит из двух уровней. На первом |

|

|

|

|

|

|

|

|

ц |

|

|

|

т |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

и |

|

|

|

ка |

р |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

ю |

Фл |

|

|

|

||||

уровне она проводится на основе восьми |

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

с |

|||||

1.тип переключателя между DP и DM; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

и |

|

|

ш |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

н |

|

|

||

характеристик: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

н |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|||

2.количество процессоров команд (IP); |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.число запоминающих устройств (модулей памяти) |

Рассмотрим компьютер |

|

|

|

|

||||||||||||||

команд (IM); |

|

|

|

|

|||||||||||||||

4.тип переключателя между IP и IM; |

Connection Machine 2 |

|

|

|

|

|

|

||||||||||||

|

его можно описать |

|

|

|

|

|

|

|

|

||||||||||

5.количество процессоров данных (DP); |

как: |

|

6.число запоминающих устройств (модулей памяти) |

||

(1, 1, 1-1, n, n, n-n, 1- |

||

данных (DM); |

||

n, nxn) |

||

7.тип переключателя между IP и DP; |

||

|

||

8.тип переключателя между DP и DP. |

|

На втором уровне классификации Д.Скилликорн просто уточняет описание, сделанное на первом уровне, добавляя возможность конвейерной обработки в

процессорах команд и данных. , Основа - абстрактная структура

состоящая из четырех компонент : ·процессор команд (IP) - интерипретатор команд

·процессор данных (DP) - преобразователь данных, в соответствии с арифметическими операциями; ·иерархия памяти (IM,DM) - запоминающее устройство

·переключатель - связь между