Тема 7 центральные устройства эвм. Основная память.

Основные вопросы

1. Основная память 1

1.1. Состав, устройство и принцип действия основной памяти 1

1.2. Размещение информации в основной памяти IBM PC 9

1.3. Расширение основной памяти IBM PC 10

1. Основная память

1.1. Состав, устройство и принцип действия основной памяти

Комплекс технических средств, реализующих функцию памяти, называется запоминающим устройством (ЗУ). ЗУ необходимы для размещения в них команд и данных. Они обеспечивают центральному процессору доступ к программам и информации.

Запоминающие устройства делятся на:

основную память (ОП),

сверхоперативную память (СОЗУ) – устаревшее название кэш и/или регистровой памяти

внешние запоминающие устройства (ВЗУ).

Основная память включает в себя два типа устройств: оперативное запоминающее устройство (ОЗУ или RAM - Random Access Memory) и постоянное запоминающее устройство (ПЗУ или ROM - Read Only Memory).

ОЗУ предназначено для хранения переменной информации. Оно допускает изменение своего содержимого в ходе выполнения процессором вычислительных операций с данными и может работать в режимах записи, чтения, хранения.

ПЗУ содержит информацию, которая не должна изменяться в ходе выполнения процессором вычислительных операций, например стандартные программы и константы. Эта информация заносится в ПЗУ перед установкой микросхемы в ЭВМ. Основными операциями, которые может выполнять ПЗУ, являются чтение и хранение.

Функциональные возможности ОЗУ шире, чем ПЗУ Но ПЗУ сохраняет информацию при отключении питания (т.е. является энергонезависимой памятью) и может иметь более высокое быстродействие, так как ограниченность функциональных возможностей ПЗУ и его специализация на чтении и хранении позволяют сократить время выполнения реализуемых им операций считывания.

В современных ЭВМ микросхемы памяти (ОП и СОЗУ) изготавливают из кремния по полупроводниковой технологии с высокой степенью интеграции элементов на кристалле (микросхемы памяти относятся к так называемым “регулярным” схемам, что позволяет сделать установку элементов памяти в кристалле (чипе) настолько плотной, что размеры элементов памяти становятся сопоставимыми с размерами отдельных атомов).

Основной составной частью микросхемы является массив элементов памяти (ЭП), объединенных в матрицу накопителя.

Каждый элемент памяти может хранить 1 бит информации и имеет свой адрес. ЗУ, позволяющие обращаться по адресу к любому ЭП в произвольном порядке, называются запоминающими устройствами с произвольным доступом.

При матричной организации памяти реализуется координатный принцип адресации ЭП, в связи с чем адрес делится на две части (две координаты) - Х и Y. На пересечении этих координат находится элемент памяти, чья информация должна быть прочитана или изменена.

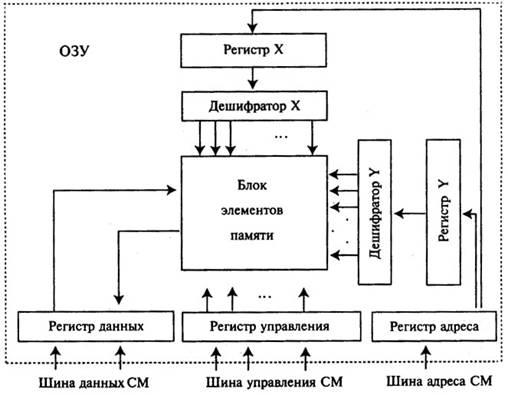

ОЗУ связано с остальным микропроцессорным комплектом ЭВМ через системную магистраль (рис.1).

Рис. 1. Структурная схема ОЗУ

По шине управления передается сигнал, определяющий, какую операцию необходимо выполнить.

По шине данных передается информация, записываемая в память или считываемая из нее.

По шине адреса передается адрес участвующих в обмене элементов памяти (поскольку данные передаются машинными словами, а один ЭП может воспринять только один бит информации, блок элементов памяти состоит из n матриц ЭП, где n - количество разрядов в машинном слове). Максимальная емкость памяти определяется количеством линий в шине адреса системной магистрали: если количество линий обозначить через m, то емкость памяти (т.е. количество элементов памяти, имеющих уникальные адреса) определяется как 2m. Так, в IBM PC XT шина адреса СМ содержит 20 линий. Поэтому максимальный объем ОП в этих машинах равен 220 = 1 Мбайт. В IBM PC AT (с микропроцессором i80286) СМ содержит 24 линии, поэтому объем ОП может быть увеличен до 16 Мбайт. Начиная с МП i80386, шина адреса содержит 32 линии. Максимальный объем ОП увеличился до 232= 4Гб.

Микросхемы памяти могут строиться на статических (SRAM) и динамических (DRAM) ЭП. В качестве статического ЭП чаще всего выступает статический триггер. В качестве динамического ЭП может использоваться электрический конденсатор, сформированный внутри кремниевого кристалла.

Статические ЭП способны сохранять свое состояние (0 или 1) неограниченно долго (при включенном питании). Динамические ЭП с течением времени записанную в них информацию теряют (например, из-за саморазряда конденсатора), поэтому они нуждаются в периодическом восстановлении записанной в них информации - в регенерации.

Микросхемы элементов памяти динамических ОЗУ отличаются от аналогичных ЭП статических ОЗУ меньшим числом компонентов в одном элементе памяти, в связи с чем имеют меньшие размеры и могут быть более плотно упакованы в кристалле. Однако из-за необходимости регенерации информации динамические ОЗУ имеют более сложные схемы управления.

Основными характеристиками ОЗУ являются объем и быстродействие.

В современных ПЭВМ ОЗУ имеет модульную структуру. Сменные модули могут иметь различное конструктивное исполнение (SIP, ZIP, SIMM, DIMM). Увеличение объема ОЗУ обычно связано с установкой дополнительных модулей, которые выпускаются в 30-контактном (30-pin) и 72-контактном исполнениях на 1,4, 8, 16, 32 и 64 Мбайта. Время доступа к модулям DRAM составляет 60 - 70 нc.

На производительность ЭВМ влияет не только время доступа, но и такие параметры (связанные с ОЗУ), как тактовая частота и разрядность шины данных системной магистрали. Если тактовая частота недостаточно высока, то ОЗУ простаивает в ожидании обращения. При тактовой частоте, превышающей возможности ОЗУ, в ожидании будет находиться системная магистраль, через которую поступил запрос в ОЗУ.

Разрядность шины данных (8, 16, 32 или 64 бита) определяет длину информационной единицы, которой можно обменяться с ОЗУ за одно обращение.

Интегральной характеристикой производительности ОЗУ с учетом частоты и разрядности является пропускная способность, которая измеряется в мегабайтах в секунду. Для ОП с временем доступа 60-70 нс и разрядностью шины данных 64 бита максимальная (теоретическая) пропускная способность при тактовой частоте СМ:

50 МГц составляет 400 Мбайт/с,

при частоте 60 МГц - 480 Мбайт/с,

при 66 МГц - 528 Мбайт/с в режиме группового обмена, реализуемом, например, при прямом доступе к памяти.

Для группового обмена характерно (еще одна характеристика ОЗУ), что при каждом обращении к памяти для считывания первого слова необходимо больше времени, чем для последующих слов.

Так, при использовании стандартной динамической памяти FPM (Fust Page Mode) DRAM на 60-70 нс каждое обращение к памяти в групповом режиме описывается формулой 7-3-3-3, т.е. для обработки первого слова необходимо 7 тактов (в течение 6 из которых СМ простаивает в ожидании), а для обработки следующих трех слов - по 3 такта, по 2 из которых СМ простаивает.

Память типа EDO (Extended Data Output)-DRAM позволяет уменьшить количество циклов ожидания (х-2-2-2, где х - количество тактов, необходимое для обработки первого слова). Память типа BEDO (Burst EDO) DRAM обеспечивает обмен по формуле х-1-1-1 для первого обращения и 1-1-1-1- для последующих. Приведенные формулы характерны для тактовых частот до 60 МГц. Синхронная динамическая память SDRAM (Synchronous DRAM) способна обмениваться блоками данных на рабочей тактовой частоте (внешняя частота процессора) без циклов ожидания:

при времени доступа 10 нс - до 100 МГц,

12 нс - до 83МГц

15 нс - до 66 МГц.

ПЗУ (энергонезависимая память)

Микросхемы ПЗУ также построены по принципу матричной структуры накопителя. Функции элементов памяти в них выполняют перемычки в виде проводников, полупроводниковых диодов или транзисторов. В такой матрице наличие перемычки может означать “1”, а ее отсутствие - “О”. Занесение формации в микросхему ПЗУ называется ее программированием, а устройство, с помощью которого заносится информация, - программатором. Программирование ПЗУ заключается в устранении (прожигании) перемычек по тем адресам, где должен храниться “О”. Обычно схемы ПЗУ допускают только одно программирование, но специальные микросхемы - репрограммируемые ПЗУ (РПЗУ) - допускают их многократное стирание и занесение новой информации. Этот вид микросхем также относится к энергонезависимым, т.е. может длительное время сохранять информацию при выключенном питании (стирание микросхемы происходит либо за счет подачи специального стирающего напряжения, либо за счет воздействия на кристалл ультрафиолетового излучения, для этого в корпусе микросхемы оставляется прозрачное окно).

Сверхоперативные ЗУ(в настоящее время это кэш-память) используются для хранения небольших объемов информации и имеют значительно меньшее время (в 2 - 10 раз) считывания/записи, чем основная память. СОЗУ (или кэш) обычно строятся на регистрах и регистровых структурах.

Регистр представляет собой электронное устройство, способное хранить занесенное в него число неограниченно долго (при включенном питании). Наибольшее распространение получили регистры на статических триггерах.

По назначению регистры делятся на регистры хранения и регистры сдвига. Информация в регистры может заноситься и считываться либо параллельно, сразу всеми разрядами, либо последовательно, через один из крайних разрядов с последующим сдвигом занесенной информации.

Сдвиг записанной в регистр информации может производиться вправо или влево. Если регистр допускает сдвиг информации в любом направлении, он называется реверсивным.

Регистры могут быть объединены в единую структуру. Возможности такой структуры определяются способом доступа и адресации регистров.

Если к любому регистру можно обратиться для записи/чтения по его адресу, такая регистровая структура образует СОЗУ с произвольным доступом.

Безадресные регистровые структуры могут образовывать два вида устройств памяти: магазинного типа и память с выборкой по содержанию (ассоциативные ЗУ).

Память магазинного типа образуется из последовательно соединенных регистров (рис. 2).

Если запись в регистровую структуру (рис.2,а) производится через один регистр, а считывание - через другой, то такая память является аналогом магазинной памяти и работает по принципу “первым вошел - первым вышел” (FIFO - first input, first output).

Если же запись и чтение осуществляются через один и тот же регистр (рис. 2,б), такое устройство называется стековой памятью, работающей по принципу “первым вошел — последним вышел” (FILO - first input, last output). При записи числа в стековую память сначала содержимое стека сдвигается в сторону последнего, К-го регистра (если стек был полностью заполнен, то число из К-го регистра теряется), а затем число заносится в вершину стека -регистр 1. Чтение осуществляется тоже через вершину стека, после того как число из вершины прочитано, стек сдвигается в сторону регистра 1.

Рис.2. Регистровая структура магазинного типа: а - типа FIFO; б - типа FILO

Стековая память получила широкое распространение. Для ее реализации в ЭВМ разработаны специальные микросхемы. Но часто работа стековой памяти эмулируется в основной памяти ЭВМ: с помощью программ операционной системы выделяется часть памяти под стек (в IBM PC для этой цели выделяется 64 Кбайта). Специальный регистр микропроцессора (указатель стека) постоянно хранит адрес ячейки ОП, выполняющей функции вершины стека. Чтение числа всегда производится из вершины стека, после чего указатель стека изменяется и указывает на очередную ячейку стековой памяти (т.е. фактически стек остается неподвижным, а перемещается вершина стека). При записи числа в стек сначала номер ячейки в указателе стека модифицируется так, чтобы он указывал на очередную свободную ячейку, после чего производится запись числа по этому адресу. Такая работа указателя стека позволяет реализовать принцип “первым вошел - последним вышел”. В стек может быть загружен в определенной последовательности ряд данных, которые впоследствии считываются из стека уже в обратном порядке, на этом свойстве построена система арифметических преобразований информации, известная под названием “логика Лукашевича”.

Память с выборкой по содержанию является безадресной. Обращение к ней осуществляется по специальной маске, которая содержит поисковый образ. Информация считывается из памяти, если часть ее соответствует поисковому образу, зафиксированному в маске. Например, если в такую память записана информация, содержащая данные о месте жительства (включая город), и необходимо найти сведения о жителях определенного города, то название этого города помещается в маску и дается команда чтение - из памяти выбираются все записи, относящиеся к заданному городу.

В микропроцессорах ассоциативные ЗУ используются в составе кэш-памяти для хранения адресной части команд и операндов исполняемой программы. При этом нет необходимости обращаться к ОП за следующей командой или требуемым операндом: достаточно поместить в маску необходимый адрес, если искомая информация имеется в СОЗУ, то она будет сразу выдана. Обращение к ОП будет необходимо лишь при отсутствии требуемой информации в СОЗУ. За счет такого использования СОЗУ сокращается число обращений к ОП, а это позволяет экономить время, так как обращение к СОЗУ требует в 2 - 10 раз меньше времени, чем обращение к ОП.

Кэш-память может быть размещена в кристалле процессора (так называемая “кэш-память I уровня”) или выполнена в виде отдельной микросхемы (внешняя кэш-память или кэш-память II уровня). Встроенная кэш-память (I уровня) в процессорах Pentium имеет объем около 16 Кбайт, время доступа - 5 - 10 нс, работает с 32-битными словами и при частотах 75-166 МГц обеспечивает пропускную способность от 300 до 667 Мбайт/с. Внешняя кэш память (II уровня) имеет объем 256 Кбайт - 1 Мбайт, время доступа - 15 нc, работает с 64-битными словами и при частоте 66 МГц обеспечивает максимальную пропускную способность 528 Мбайт/с. Конструктивно исполняется либо в виде 28-контактной микросхемы, либо в виде модуля расширения на 256 или 512 Кбайт.

Рис. 3. Возможный состав системы памяти ЭВМ

Регистровая – 64-256 слов, ( ) 1 такт

Кэш 1-го уровня – 8 Кслов, ( не более 128 Кб ) 1-2 такта

Кэш 2-го уровня – 256 Кслов, (от 128 Кбайт до 1−12 Мбайт) 3-5 тактов

Кэш 3-го уровня – 1 Мслов, (более 24 Мбайт) 6-11 тактов

Основная память – 4 Гслов, 12-55 тактов

Внешняя память – к*Тслов, от 106 слов

Буферные ЗУ:Их назначение состоит в сокращении времени передачи информации между процессором и более медленными уровнями памяти компьютера. Буферная память может устанавливаться на различных уровнях. Ранее такие буферные ЗУ в отечественной литературе называлисверхоперативными (СОЗУ), сейчас это название практически полностью вытеснил термин "кэш-память" или простокэш.

Принцип использования буферной памяти во всех случаях сводится к одному и тому же. Буфер представляет собой более быстрое (а значит, и более дорогое), но менее емкое ЗУ, чем то, для ускорения работы которого он предназначен. При этом в буфере размещается только та часть информации из более медленного ЗУ, которая используется в настоящий момент.

Если доля hобращений к памяти со стороны процессора, удовлетворяемых непосредственно буфером (кэшем) высока (0,9 и более), то среднее время для всех обращений оказывается близким ко времени обращения к кэшу, а не к более медленному ЗУ.

Пример.

Пусть двухуровневая память состоит из кэш и оперативной памяти, как показано на рис.5. И пусть, например, время обращения к кэшу tc = 1 нс (10-9 с), время tm обращения к более медленной памяти в десять раз больше – tm = 10 нс, а доля обращений, удовлетворяемых кэшем, h = 0,95.

Тогда среднее время обращения к такой двухуровневой памяти Tср составит

Tср = 1 * 0.95 + 10 * (1 – 0.95 ) = 1.45 нс,

т.е. всего на 45% больше времени обращения к кэшу. Значение h зависит от размера кэша и характера выполняемых программ и иногда называется отношением успехов или попаданий (hit ratio).

Рис.5.

К расчету среднего времени обращения(tc– время обращения к кэш-памяти, tm– время обращения к ОП,h– доля

обращения, обслуживаемых кэш-памятью,

1

–h– доля обращений, обслуживаемых

ОП)

Рис.5.

К расчету среднего времени обращения(tc– время обращения к кэш-памяти, tm– время обращения к ОП,h– доля

обращения, обслуживаемых кэш-памятью,

1

–h– доля обращений, обслуживаемых

ОП)

Размеры кэш-памяти существенно изменяются с развитием технологий. Так, если в первых ЭВМ, где была установлена кэш-память, во второй половине 1960-х годов (большие ЭВМ семейства IBM-360) ее емкость составляла всего от 8 до 16 КБайт, то уже во второй половине 1990-х годов емкость кэша рядовых персональных ЭВМ составляла 512 КБайт. Причем сама кэш-память может состоять из двух (а в серверных системах – даже трех- Itanium) уровней: первого (L1) и второго (L2), также отличающихся своей емкостью и временем обращения.

КЭШ подробно

Конструктивно кэш уровня L1 входит в состав процессора (поэтому его иногда называют внутренним). Кэш уровня L2 либо также входит в микросхему процессора, либо может быть реализован в виде отдельной памяти. Как правило, на параметры быстродействия процессора большее влияние оказывают характеристики кэш-памяти первого уровня.

Время обращения к кэш-памяти, которая обычно работает на частоте процессора, составляет от десятых долей до единиц наносекунд, т.е. не превышает длительности одного цикла процессора.

Обмен информацией между кэш-памятью и более медленными ЗУ для улучшения временных характеристик выполняется блоками, а не байтами или словами.Управляют этим обменом аппаратные средства процессора и операционная система, и вмешательство прикладной программы не требуется. Причем непосредственно командам процессора кэш-память недоступна, т.е. программа не может явно указать чтение или запись в кэш-памяти, которая является для нее, как иногда говорят, “прозрачной” (прямой перевод используемого в англоязычной литературе словаtransparent).

Кэш (cache) - это память быстрого доступа, расположенная непосредственно в процессоре (в старых ЦП в виде микросхемы). Эта характеристика не так важна, как тактовая частота, но все же будет не приятно если кэш будет маленьким. В нем храниться информация с наибольшей вероятностью запроса. Доступ к этой информации будет воспроизведен мгновенно, этим cache отличается от оперативной памяти.

Февр.2011