- •2 Разработка структурной и функциональной схем устройства

- •Разработка структурной схемы устройства

- •2.2 Разработка функциональной схемы устройства

- •3 Разработка принципиальной схемы устройства

- •3.1 Выбор элементной базы

- •3.2 Проектирование схем выделения фронтов временного интервала

- •3.3 Проектирование генератора

- •3.4 Проектирование счетного устройства

- •3.5 Проектирование блока вывода в устройство обработки

- •3.6 Проектирование блока индикации

- •3.7 Проектирование блока управления

3.5 Проектирование блока вывода в устройство обработки

Двоичный код измеренного временного интервала передается в линию связи, которая передает последовательный код. Для преобразования кода измеренного временного интервала из паралельного в последовательный используется паралельно-последовательный регистр. Запись в который осуществляется после измерения а выдача в устройство обработки с заданной скоростью (VПЕР=4800).

Для передачи 12 информационных разрядов последовательно соеденим три таких регистра.

Преобразователь паралельного кода в последовательный построим на элементах И-НЕ – КР1533ЛА3 и на D-триггерах – КР1533ТМ2.

Рисунок 15 – Паралельно-последовательный регистр

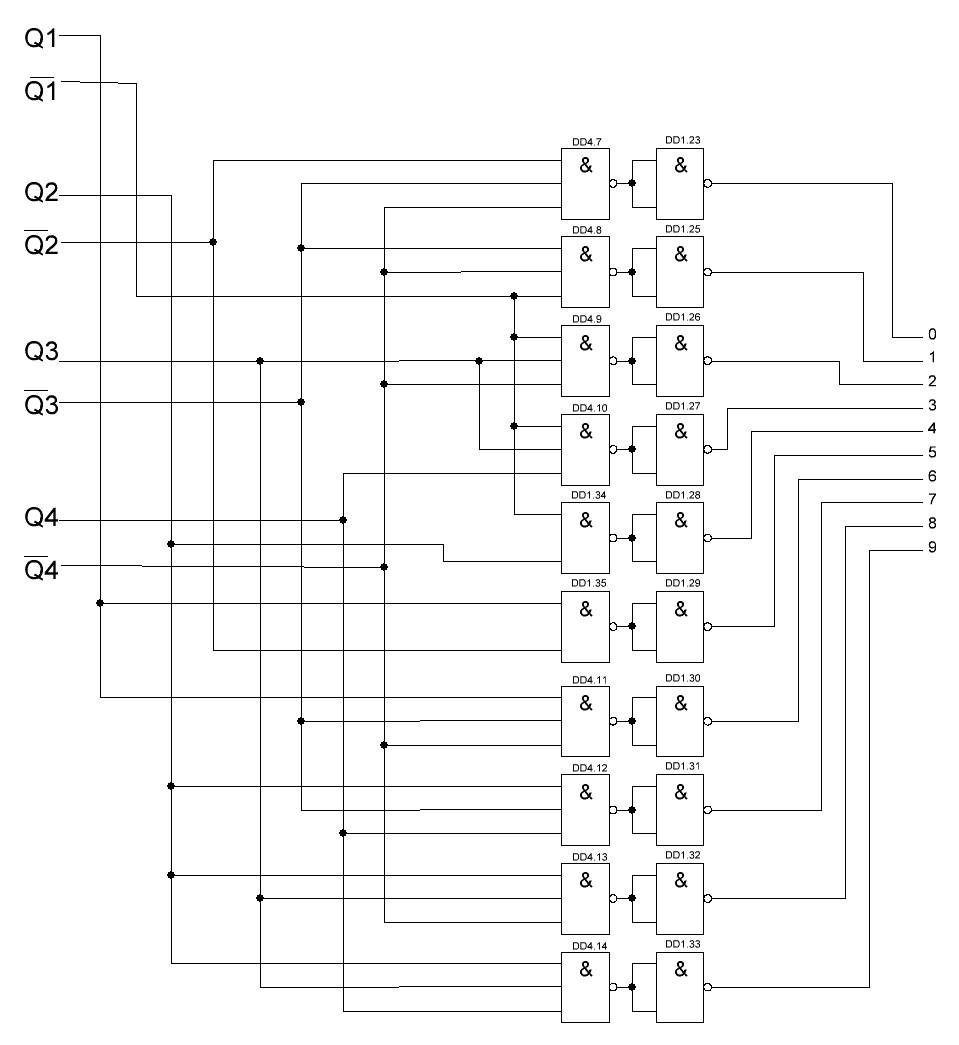

3.6 Проектирование блока индикации

Устройство отображения включает в себя двоично-десятичный преобразователь, регистр для хранения информации и десятичный индикатор.

Для реализации регистра хранения воспользуемся микросхемой КР1533ТМ2 – D-триггера.

Рисунок 16 – Схема регистра хранения

Для построения преобразователя кода составим таблицу функционирования. Код данных 2421, элемент индикации десятичный, т.е. для отображения цифры необходимо подать управляющий сигнал только на один вход.

Таблица истинности для двоично десятичного преобразователя:

|

|

х1 |

х2 |

х3 |

х4 |

D |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

2 |

0 |

0 |

1 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

3 |

0 |

0 |

1 |

1 |

3 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

4 |

0 |

1 |

0 |

0 |

4 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

|

6 |

0 |

1 |

1 |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

|

7 |

0 |

1 |

1 |

1 |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

|

8 |

1 |

0 |

0 |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

|

9 |

1 |

0 |

0 |

1 |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

|

10 |

1 |

0 |

1 |

0 |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

* |

|

11 |

1 |

0 |

1 |

1 |

5 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

12 |

1 |

1 |

0 |

0 |

6 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

13 |

1 |

1 |

0 |

1 |

7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

14 |

1 |

1 |

1 |

0 |

8 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

15 |

1 |

1 |

1 |

1 |

9 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Минимизируем функции.

|

|

00 |

01 |

11 |

10 |

|

00 |

1 |

0 |

0 |

0 |

|

01 |

0 |

* |

* |

* |

|

11 |

0 |

0 |

0 |

0 |

|

10 |

* |

* |

0 |

* |

|

|

00 |

01 |

11 |

10 |

|

00 |

0 |

1 |

0 |

0 |

|

01 |

0 |

* |

* |

* |

|

11 |

0 |

0 |

0 |

0 |

|

10 |

* |

* |

0 |

* |

|

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

0 |

1 |

|

01 |

0 |

* |

* |

* |

|

11 |

0 |

0 |

0 |

0 |

|

10 |

* |

* |

0 |

* |

|

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

1 |

0 |

|

01 |

0 |

* |

* |

* |

|

11 |

0 |

0 |

0 |

0 |

|

10 |

* |

* |

0 |

* |

|

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

0 |

0 |

|

01 |

1 |

* |

* |

* |

|

11 |

0 |

0 |

0 |

0 |

|

10 |

* |

* |

0 |

* |

|

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

0 |

0 |

|

01 |

0 |

* |

* |

* |

|

11 |

0 |

0 |

0 |

0 |

|

10 |

* |

* |

1 |

* |

|

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

0 |

0 |

|

01 |

0 |

* |

* |

* |

|

11 |

1 |

0 |

0 |

0 |

|

10 |

* |

* |

0 |

* |

|

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

0 |

0 |

|

01 |

0 |

* |

* |

* |

|

11 |

0 |

1 |

0 |

0 |

|

10 |

* |

* |

0 |

* |

|

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

0 |

0 |

|

01 |

0 |

* |

* |

* |

|

11 |

0 |

0 |

0 |

1 |

|

10 |

* |

* |

0 |

* |

|

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

0 |

0 |

|

01 |

0 |

* |

* |

* |

|

11 |

0 |

0 |

1 |

0 |

|

10 |

* |

* |

0 |

* |

Реализируем преобразователь кода в базисе Шеффера и Пирса. Используя МС КР1533ЛА3, КР1533ЛА4 – элементы И-НЕ, КР1533ЛЕ1, КР1533ЛЕ4 – элементы ИЛИ-НЕ.

Рисунок 17 – Реализация в базисе Пирса

Рисунок 18 – Реализация в базисе Шеффера

Реализация ПК на основе дешифратор-шифратор нерациональна. Так как необходимо использовать 512 входовой шифратор, или каскадировать на основе шифраторов с меньшим количеством входов, что в свою очередь уменьшит быстродействие.

Для отображения используем газорязрядный индикатор ИН8-2.

Рисунок 19 – параметры индикатора ИН8-2