- •Федеральное агентство по образованию Российской Федерации

- •Тема 12. Основы теории электронных приборов

- •Тема №2.Электрическое поле.Электрические цепи постоянного тока.

- •Тема №3. Магнитное поле.Магнитные цепи. Индуктивность и ёмкость в электрических цепях.

- •Свойства ферромагнитных материалов. Гистерезис.

- •Тема №4. Однофазные электрические цепи синусоидального тока.

- •Тема№5.Общие свойства четырёхполюсников.

- •Тема №6. Переходные процессы в электрических цепях.

- •Тема№7.Методы расчёта переходных процессов.

- •Какому знаку подчиняется сигнал на выходные цепи (вывод формулы)

- •Тема №8. Трехфазные электрические цепи.

- •Тема №9.Периодические и апериодические несинусоидальные сигналы.

- •Тема№10.Расчёт электрических цепей с помощью оператора Лапласа.Спектры.

- •Передаточная функция и ее связь с дифференциальным уравнением, импульсной и частотной характеристикой

- •Раздел 2. Электроника Тема 12. Основы теории электронных приборов

- •Параметры, характеристики выпрямительных диодов. Типы полупроводниковых диодов.

- •Параметры диодов.

- •Выпрямительные диоды

- •Усиление электрических сигналов с помощью биполярного транзистора.

- •Параметры транзистора:

- •Общая характеристика схем включения транзисторов p-n-p типа.

- •Полевые транзисторы.

- •Полевые транзисторы с изолированным затвором.

- •Полевой транзистор со встроенным каналом (мдп- транзистор).

- •Транзистор с индуцированный каналом (моп- транзистор).

- •Транзистор с затвором Шотки.

- •Силовые полупроводниковые приборы.

- •Оптоэлектроника.

- •Светодиод.

- •Тема 13. Транзисторные усилители электрических сигналов.

- •Коэффициент усиления.

- •Импульсные усилители (иу).

- •Электрические фильтры.

- •Дифференцирующие цепи.

- •Дифференцирующая rl-цепь

- •Интегрирующие цепи(фнч) (фильтр высоких частот)

- •Интегрирующая rc-цепь.

- •Интегрирующая rl-цепь

- •Активные фильтры.

- •Интегральные микросхемы

- •Тема 14. Аналоговые и цифровые элементы и устройства.

- •Логические элементы в дискретном исполнении

- •Триггеры в интегральном исполнении.

- •Тема 15. Комбинационные цифровые устройства.

- •Сумматоры

- •Демультиплексор

- •Регистры (узлы накапливающего типа)

- •Набор элементарных операций:

- •Параллельный статический регистр.

- •Расшифровка временной диаграммы.

- •Цифроаналоговые преобразователи (цап).

- •Аналого-цифровые преобразователи (ацп).

- •Запоминающие устройства (зу).

- •Классификация зу.

- •Тема 16. Источники вторичного питания. Генераторы.

- •Internet-ресурсы.

- •Http://ktf.Krk.Ru/courses/foet/(Сайт содержит информацию по разделу «Электроника»)

- •Http://www.College.Ru/enportal/physics/content/chapter4/section/paragraph8/theory.Html(Сайт содержит информацию по теме «Электрические цепи постоянного тока»)

Логические элементы в дискретном исполнении

Базисные логические функции(логические элементы) могут быть представлены как в дискретном исполнении, так и методами интегральной технологии. Базисные логические функции(логические элементы) «И», «ИЛИ» и «НЕ» могут выполняться на диодах, резисторах, биполярных полевых транзисторах. В соответствии с конструкцией построения логических элементов различают резисторно-транзисторную логику(РТЛ), диодно-транзисторную(ДТЛ), транзисторно-транзисторную логику(ТТЛ), а также логику на полевых транзисторах(«р»-канальная-рМОП, «n»-nМОП), комплементарную (КМДП) и динамическую (МОП).

Логический элемент "НЕ" (логическое отрицание).

Логический элемент "НЕ" имеет один вход и один выход. Условно обозначается в схемах:

Таблица истинности операции "НЕ" имеет вид:

|

X |

Y |

|

0 |

1 |

|

1 |

0 |

Логический элемент " НЕ" представляет собой усилительный каскад на транзисторе, включённом по схеме ОЭ и работает в ключевом режиме. На вход подаются положительные сигналы в положительной логике. Используется транзистор типаn-p-n(рис.14-12.).

Рис. 14-12. Электронная схема реализующая логический элемент "НЕ".

Допустим, что транзистор VT

закрыт отрицательным потенциалом на

базе от -Еб. Если на"Вх"

подать низкий потенциал, соответствующий

"0" ![]() ,

то VT

остаётся закрытым, а при этом Iк=0

и

,

то VT

остаётся закрытым, а при этом Iк=0

и ![]() .

Следовательно,

на выходе будет высокое напряжение

соответствующее "I".

.

Следовательно,

на выходе будет высокое напряжение

соответствующее "I".

Если на “Вх” подать высокий положительный

потенциал соответствующий "I",

тоVT

будет в состоянии насыщения и![]() .Такой

логический элемент еще называют

"инвертором".

.Такой

логический элемент еще называют

"инвертором".

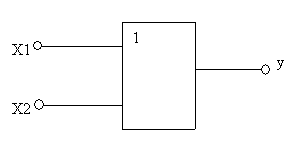

Логический элемент "И" (логическое умножение).

Обозначается![]() .

Элемент имеет как минимум два входа и

один выход. Условное обозначение

элемента “И”:

.

Элемент имеет как минимум два входа и

один выход. Условное обозначение

элемента “И”:

Таблица истинности операции «И» имеет вид:

-

X1

X2

Y

0

0

0

0

1

0

1

0

0

1

1

1

Схема двухходового элемента «И» на биполярных транзисторах показана на рис 14-13.

Рис 14-13. Электронная схема, реализующая логический элемент «И».

Из схемы (рис 14-13) видно, что транзисторы VT1 иVT2 соединены последовательно и электрический ток может протекать тогда, когда открыты оба транзистора. В том случае, когда один из транзисторов будет закрыт, то на входе напряжение будет равно «0», что соответствует таблице истинности. Этот логический элемент называется конъюктор.

Логический элемент «ИЛИ» (логическое сложение)

Обозначается

![]() .

.

Таблица истинности операции «или» имеет вид:

-

X1

X2

Y

0

0

0

0

1

1

1

0

1

1

1

1

Схема двухходового логического элемента «ИЛИ» показаны на рис 14-14.

Рис 14-14. Электронная схема, реализующая логический элемент «ИЛИ».

Схема элемента «ИЛИ» выполнена на биполярных транзисторах (технология

транзисторно-транзисторной логики).

Если на входы

![]() и

и![]() не подается

не подается

напряжение, то TV1 иTV2

заперты и на![]() (на выходе) нет напряжения, и это

соответствует тому, что на выходе

логический «0». Если на один вход или на

оба входа подается положительное

напряжение (логическая «1»), то один или

оба транзистора открываются и на выходе

появляется положительное напряжение,

отображающее «1», что соответствует

таблице истинности. Этот логический

элемент еще называют дизъюнкцией.

(на выходе) нет напряжения, и это

соответствует тому, что на выходе

логический «0». Если на один вход или на

оба входа подается положительное

напряжение (логическая «1»), то один или

оба транзистора открываются и на выходе

появляется положительное напряжение,

отображающее «1», что соответствует

таблице истинности. Этот логический

элемент еще называют дизъюнкцией.

Логический элемент «И-НЕ»(отрицание умножения, штрих Шеффера)

Условное обозначение в схемах.

Таблица истинности операции “И-НЕ” имеет вид:

|

X1 |

X2 |

Y |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Рассмотрим схему «И-НЕ» транзисторно-транзисторной логики (ТТЛ) (элемент Шеффера, рис 14-15)

Рис 14-15. Электронная схема, реализующая логический элемент «И-НЕ» (выполнена в ТТЛ).

Данная схема предназначен для работы от сигналов в виде напряжений, отрицательной полярности в отрицательной логике. (рис 14-15)

При отсутствии сигналов на входах схемы,

![]() и

и![]() заперты

положительным смещением

заперты

положительным смещением![]() ,

тока нет и на выходе

,

тока нет и на выходе![]() (то

есть «I»).Когда на входы

одновременно будут поданы

(то

есть «I»).Когда на входы

одновременно будут поданы![]() (

то есть «I») и

(

то есть «I») и![]() ,

тоV

,

тоV![]() иV

иV![]() откроются и на выходе

откроются и на выходе![]() .Если

на ВхIподать «0», а на Вх2

–«1», то

.Если

на ВхIподать «0», а на Вх2

–«1», то![]() будет заперт, а

будет заперт, а![]() открыт, тока в цепи нет и

открыт, тока в цепи нет и![]() (логическая «1»). Если на ВХ1 подать «1»,

а на ВХ2 – «0», то на выходе также

(логическая «1»). Если на ВХ1 подать «1»,

а на ВХ2 – «0», то на выходе также![]() (логическая

«1»)

(логическая

«1»)

Логический элемент «ИЛИ-НЕ»(отрицание сложения элемент Пирса).

Условное обозначение в схемах (логического элемента «ИЛИ-НЕ»)

Таблица истинности логического элемента «ИЛИ-НЕ» :

-

X1

X2

Y

0

0

1

0

1

0

1

0

0

1

1

0

Рассмотрим схему элемента «ИЛИ-НЕ» (рис 14-16) :

Рис 14-16. . Электронная схема, реализующая логический элемент «ИЛИ-НЕ».

Схема (рис 14-16) работает от сигналов в виде напряжений отрицательной полярности в отрицательной логике. Схема выполнена на транзисторе и работает как логический элемент "НЕ" с несколькими входами (не менее двух).

При отсутствии на

входах сигналов транзистор заперт

положительным смещением +Еб

на базе,

тогда Iк=0

и Uвых

= -Ек (т.е. "I").

Когда на любой из входов поступит сигнал

Ubx

= Uo

(т.е. "I"),

то транзистор отпирается и Uвых![]() 0

(т.е. "О") и т.д. Здесь чаще всего

используют МОП-транзисторы,

т.к. у них высокая степень интеграции и

повышенная помехоустойчивость.

0

(т.е. "О") и т.д. Здесь чаще всего

используют МОП-транзисторы,

т.к. у них высокая степень интеграции и

повышенная помехоустойчивость.

Основываясь на законах алгебры логики можно любой логический элемент заменить устройством, собранных только на двухходовых элементах И-НЕ.

1). Операция НЕ,

![]() ,

,![]()

Таблица истинности операции «НЕ».

-

у

0

0

1

1

1

0

2). Операция И,

![]()

Таблица истинности операции «И».

|

Х1 |

Х2 |

И1 |

НЕ(у1) |

И2 |

НЕ (у) |

|

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

1 |

3). Операция «ИЛИ»,

![]()

Таблица истинности операции «ИЛИ».

|

Х1 |

Х2 |

И1 |

И2 |

И |

И |

И3 |

У(или) |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

4). Операция сложения по модулю два (исключающее ИЛИ),

![]()

Таблица истинности операции «исключающее ИЛИ».

|

Х1 |

Х2 |

И1 |

И2 |

И1 |

И2 |

И3 |

И4 |

И3 |

И4 |

И |

НЕ(У) |

|

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1

1 2

2