- •1. Архитектура пэвм и ее подсистемы ввода-вывода. Классификация интерфейсов и периферийных устройств (пу), отличительные признаки. Архитектура, топология.

- •2. Основные принципы программирования доступа к пу. Сигналы, протоколы. Особенности адресации. Методы управления обменом. Регистровая программная модель пу.

- •3. Прерывания, таймеры, контроль достоверности передачи данных. Физический интерфейс.

- •4. Системная периферийная шина pci, история создания, основные характеристики. Архитектура и топология. Конфигурационный механизм. Автоконфигурация.

- •5. Транзакция pci, фазы транзакции. Протокол, сигналы, временные диаграммы. Арбитр шины. Контроль достоверности передачи.

- •6. Шина pci: механизмы доступа к устройствам, особенности адресации устройств, особенности механизма прерываний устройств pci

- •7. Электрический интерфейс pci. Механический интерфейс (разъемы и слоты). Карты pci

- •8. Назначение шины pci-X, предпосылки ее создания. Модификации: протокола обмена, конфигурационных регистров, электрического и физического уровней. Шина pci-X 2.0 - основные отличия от pci.

- •9. Транзакции pci-X: типы, форматы атрибутов. Режимы pci-X. Механизм обмена сообщениями. Механизм ecc. Корректирующие коды и помехоустойчивое кодирование

- •10. Конструктивное исполнение устройств agp. Назначение шины, особенности применения. Отличия от pci. Топология agp.

- •11. Протокол, сигналы и линии agp. Конвейерные транзакции agp. Два метода подачи запроса. Графическая апертура.

- •13. Архитектура pci Express. Уровни протокола, форматы пакетов, кодирование, возможности управления и настройки.

- •14. Пакеты уровня транзакций. Качество обслуживания (QoS), и виртуальные каналы. Форматы заголовков. Поле «дайджеста» (crc-код).

- •15. Пакеты канального уровня. Оборачивание tlp. Физический уровень. Кодирование 8b/10b. Коммутаторы. Физический интерфейс. Перспективы развития.

- •16. Назначение lpc, место в общей системной шине пэвм. Топология. Протокол, физический интерфейс, формат транзакции. Чип ввода-вывода Super I/o.

- •17. Протокол шины lpc, логическая и физическая структуры. Сигналы шины lpc. Протоколы dma, ecp. Режимы протокола. Фазы транзакции.

- •20. Жесткий диск типа «винчестер». Принцип магнитной записи. Законы Гаусса. Закон индукции Фарадея. Теорема о циркуляции магнитного поля. Типы магнитной записи. Классификация жестких дисков.

- •22. Кодирование двоичной информации. Проблема синхронизации. Базовые методы кодирования: fm, mfm, rll, prml.

- •24 Тракт чтения. Тракт записи. Плотность записи. Методики повышения плотности записи.

- •25 Протоколы обмена ata, режимы pio, dma и udma. Электрический интерфейс. Сигналы atа, переопределение сигналов в режиме Ultra dma. Регистры устройства ata. Протокол взаимодействия хоста и устройства.

- •27. Архитектура шины Ultra ata, пропускная способность шины, синхронизация. Интерфейс atapi. Дополнительные функции ata: smart, Security, hpa, nv Cache.

- •40. Канальный уровень sas, способы маршрутизации. Архитектура экспандера.

- •42. Дисковые массивы: технология raid, архитектура, уровни, отказоустойчивость.

- •43. Массивы raid 0, raid 1, оценка надежности.

- •45. Массивы raid 2, raid 3, raid 4. Восстановление одного диска.

- •46. Массив raid 5. Способ восстановления данных. Вероятность выхода из строя raid 5.

- •47.Массив raid6. Способ восстановления данных. Вероятность выхода из строя raid 6.

- •48. Расширенные уровни raid: 1е, 5е, 5ее, 6е. Гибридные массивы.

- •49.Накопители на магнитной ленте. Основные характеристики: технология, метод сжатия, размер буфера, интерфейс. Устройства чтения/записи на ленту. Форматы qic, Travan, slr, dat.

- •51. Prml-кодирование. Блок-диаграмма канала pr4. Блок-диаграмма системы prml. Форма сигнала и магнитные поля. Ml-детектор vs. Пороговый детектор.

- •66. Звуковая карта, типовая схема, параметры.Кодек ac’97. Интерфейс ac'97: структура кодека, протокол, сигналы.

- •80. Интерфейс Centronics. Характеристики, принцип действия, сигналы, протокол. Механизм spp. Особенности применения.

- •81. Стандарт ieee 1284-1994. Режимы полубайтного ввода, двунаправленного байтного ввода, epp, ecp. Согласование режимов ieee 1284.

- •82. Стандарт ieee 1284-1994. Физический и электрический интерфейс. Требования к передатчикам и приемникам. Принципы взаимодействия шин расширения и интерфейсов пу. Конфигурирование lpt-портов.

- •83. Интерфейс rs-232c. Характеристики, сигналы, протоколы, электрический интерфейс. Особенности применения. Программная модель, порт com. Стандарты последовательных интерфейсов.

- •84. Последовательность управляющих сигналов. Аппаратное управление потоком. Программный протокол управления потоком xon/хoff.

- •86. Физический интерфейс usb, кабели и разъемы. Кодирование nrzi. Хаб usb, структура.

- •87. Api: uhci, ohci, ehci, spb. Интерфейс usb otg. Беспроводной интерфейс wusb.

- •88. Интерфейс 1394 (FireWire). Архитектура, топология, характеристики. Уровни протокола, форматы пакетов, режимы обмена. Протокол самоконфигурирования. Программные интерфейсы.

- •89. Обмен данными, транзакции интерфейса 1394. Синхронная передача. Асинхронные транзакции (субакции). Пакеты. Изохронные передачи. Арбитраж. Физический интерфейс, разъемы и кабели. Протоколы обмена.

- •90. Интерфейс Bluetooth. Интерфейс uwb.

5. Транзакция pci, фазы транзакции. Протокол, сигналы, временные диаграммы. Арбитр шины. Контроль достоверности передачи.

5.1 Транзакция PCI, фазы транзакции

Транзакция -атомарная операция обмена данными между двумя устройствамиPCI

В рамках транзакции определены два объекта:

инициатор обмена (Initiator)

целевое устройство (Target).

В рамках одной физической шины в конкретный момент может происходить только одна транзакция.

Транзакция состоит из фазы адресациии одной или несколькихфаз передачи данных.

5.2 Протокол, сигналы, временные диаграммы

Сигналы шины PCI

AD[31:0] ([63:0]) – мультиплексированная шина адреса/данных

C/BE[3:0]# - мультиплексированная шина команд/маска разрешения байт

FRAME# - сигнал кадра (транзакции)

DEVSEL# - подтверждение выбора от целевого устройства

IRDY# - инициатор готов к обмену

TRDY# - целевое устройство готово к обмену

STOP# - досрочное прекращение транзакции

LOCK# - резервирование шины за одним устройством

REQ# - запрос на доступ к шине

GNT# - разрешение на доступ к шине

PAR– бит четности линийADи С/BE#

PERR# - ошибка четности

PME# - сигнал о начале цикла изменения энергопотребления

CLKRUN# - частота синхронизации номинальная

PRSNT[0,1]# - код потребляемой мощности

RST# - сброс

IDSEL– выбор устройства

SERR# - ошибка

REQ64# - запрос на 64-битный обмен (одновр. сFRAME#)

ACK64# - подтверждение 64-битного обмена (одновр. сDEVSEL#)

INTA#-INTD# - линии прерывания

M66EN– поддержка частоты 66 МГц

PCIXCAP– поддержка протоколаPCI-X

SMBCLK– тактовый сигналSMBus

SMBDAT– линия данныхSMBus

TCLK,TDI,TDO,TMS,TRST– сигналы интерфейсаJTAG

Протокол транзакции

До начала транзакции инициатор подаёт запрос на доступ к шине при помощи сигнала REQ#. Арбитр проверяет заявки и разрешает доступ сигналом GNT#.

Инициатор дожидается завершения текущей транзакции(снятия сигнала FRAME#) и начинает работу.

1 этап – фаза адресации

Подав сигнал FRAME# (начало транзакции), инициатор на шину адресаA/Dвыставляет 32- или 64-битный адрес, а на шину командC/BE# - код операции (команду).

Фазу адресации отслеживают все устройства на шине, включая мост. То устройство, которое определило принадлежность адреса к своим ресурсам, сообщает об этом сигналом подтверждения выбора устройстваDEVSEL#. Мост также может взять на себя роль целевого устройства, чтобы передать транзакцию на другие шины.

2 этап – фаза передачи данных

Получив сигнал DEVSEL#, инициатор готовит внутренние буферы к обмену и выставляетIRDY# по готовности. При выполнении записи в следующем такте на шину данныхA/Dпоступает первая группа данных.

Целевое устройство по готовности выставляет сигнал TRDY# и выставляет первую группу данных при выполнении чтения. Его отсутствие означает необходимость холостого такта, в течение которого инициатор прекращает передачу (или повторяет первую фазу данных).

Холостой такт может вводить и инициатор снятием сигнала IRDY#.

Маска байтов (линии C/BE#) определяет, какие из байты из группы (по шине передаются сразу 4 или 8) заполнены полезными данными. Маску формирует тот, кто выставляет данные (при записи – инициатор, при чтении – целевое устройство).

3 этап- завершение транзакции

Длина транзакции заранее неизвестна, поскольку она может быть закончена по инициативе трех агентов – инициатора, целевого устройства или арбитра.

Со стороны инициатора – снятием сигнала FRAME#:

Нормальное завершение: после передачи всех данных.

Прекращение (master-abort): инициатор не дождался сигналаDEVSEL#.

Со стороны целевого устройства – сигналом STOP#:

Повтор (retry): сигналSTOP# выставляется до сигналаTRDY# в первой фазе данных. Это запрос повторения той же транзакции.

Отключение (disconnect):STOP# выставляется в очередной фазе данных. Запрос на повтор со следующей (если был установленTRDY#) или текущей (не был установленTRDY#) фазы данных.

Отказ (target-abort):снятиеDEVSEL# вместе с установкойSTOP#.

Со стороны арбитра – снятием сигнала GNT#. Это может потребоваться, например, если инициатор не закончил транзакцию вовремя.

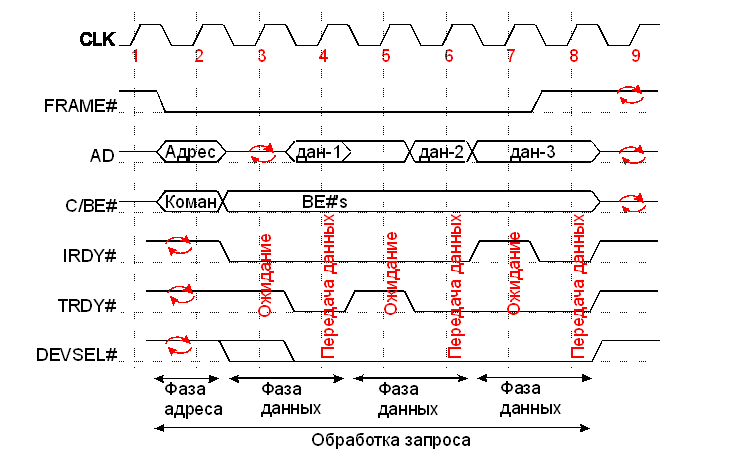

Временные диаграммы:

Чтение

Запись

5.3 Арбитр шины

В роли арбитров шины выступают мосты, обрабатывая запросы от устройств на доступ к шине и отслеживая соблюдение протокола обмена. Суть арбитража объяснена пунктом выше. Здесь представим лишь временную диаграмму

5.4 Контроль достоверности передачи

Для контроля достоверности (корректности) передаваемых данных в шине PCIпредусмотренмеханизм четности(parity). СигналPAR# – признак нечетного количества единиц на линияхAD[31:0] иC/BE#[3:0]. СигналPAR64# используется для контроля четности линийAD[63:32] иC/BE#[7:4] в случае применения 64-битной шины. Эти сигналы вырабатываются устройством, которое управляет шинойAD. Задержка сигналовPAR# иPAR64# составляет один такт (для того, чтобы устройство успело подсчитать количество пришедших бит).

В случае обнаружения нарушения четности в фазе данных приемниквырабатывает сигналPERR# (с задержкой в один такт) и выставляет бит 15 в регистре состояния. Для фазы адреса проверку четности выполняетцелевое устройство, при ошибке вырабатывается другой сигнал –SERR#, выставляется бит 14 в регистре состояния.