МноговходовыйСумматор-Вычитатель / копия / ПЗ

.docРЕФЕРАТ

Пояснительная записка 18 с., 12 рис., х источников, 2 л. графического материала

СУММАТОР, ВЫЧИТАТЕЛЬ, АНАЛОГОВЫЙ ВЫЧИСЛИТЕЛЬ, ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ, БЛОК РЕЗИСРОРОВ

Объектом выполненной работы является многовходовой сумматор-вычитатель предназначенный для математической обработки аналоговых величин.

Цель работы – ознакомление с устройством и принципом работы сумматора-вычитателя; проектирование сумматора-вычитателя.

В процессе работы проводились аналитический обзор, расчеты на структурном уровне, выбор элементов и разработка принципиальной электрической схемы, электрическое моделирование одного из узлов системы, анализ метрологических характеристик.

В результате работы был спроектирован многовходовой сумматор-вычитатель, соответствующий требованиям технического задания.

Степень внедрения – учебное проектирование.

Содержание

ВВеДеНИЕ 6

1 ВЫБОР И ОБОСНОВАНИЕ НАПРАВЛЕНИЯ ПРОЕКТИРОВАНИЯ 7

2 РАСЧЕТ НА СТРУКТУРНОМ УРОВНЕ 9

2.1 Блок вычитания 9

2.2 Блок суммирования 10

2.3 Блок управления 11

3 ВЫБОР И РАСЧЕТ ЭЛЕМЕНТОВ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ 12

3.1 Блок вычитания 12

3.2 Блок суммирования 13

3.3 Регистр 13

3.4 Дешифратор 13

3.5 Электронные ключи 14

4 ЭЛЕКТРИЧЕСКОЕ МОДЕЛИРОВАНИЕ 15

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ 18

ВВеДеНИЕ

Суммирующие устройства предназначены для моделирования зависимостей вида

![]() .

.

В тех случаях, когда в качестве переменных данного выражения выступают значения напряжения (xi = Ui, y = U), для построения суммирующих и вычитающих устройств могут быть использованы пассивные и активные электрические суммирующие цепи. Пассивные цепи строятся исключительно на резисторах, активные же содержат операционные усилители, расширяющие функциональность и повышающие точность устройств [1].

Несмотря на широчайшее распространение цифровой техники, вопрос разработки и совершенствования аналоговых систем вычисления и преобразования величин остается актуальным. Аналоговые вычислители находят применение в системах автоматического управления технологическими процессами.

Точность и стабильность аналоговых вычислительных систем уступают аналогичным характеристикам цифровых компонентов, но для решения широкого спектра технических и научных задач они приемлемы.

Существенным преимуществом аналоговых вычислителей является способность работать непосредственно со значениями физической величины (например, напряжения или тока) без необходимости применения дополнительных аналогово-цифровых и цифро-аналоговых преобразователей.

1 ВЫБОР И ОБОСНОВАНИЕ НАПРАВЛЕНИЯ ПРОЕКТИРОВАНИЯ

В результате аналитического обзора литературы, а также поиска информации в сети Интернет были выделены устройства-аналоги и устройство-прототип.

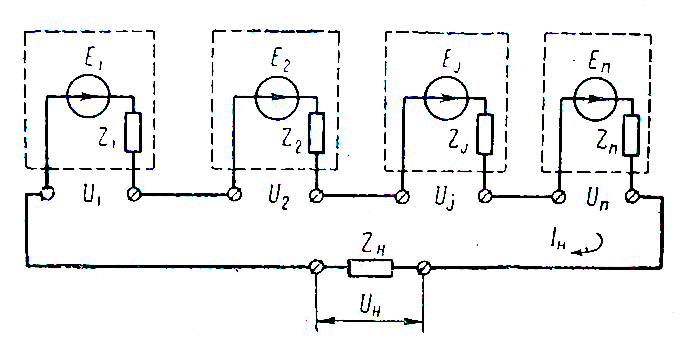

Простейшим видом аналоговых суммирующих устройств являются пассивные суммирующие цепи (рисунок 1.1)

Рисунок 1.1 – Пассивная суммирующая последовательная цепь

Подобная схема обладает множеством недостатков. Например, невозможность усиления сигнала, низкая точность, сложность реализации операции вычитания [1].

Путем введения в схему операционного усилителя можно получить активное суммирующее устройство, обладающее существенно лучшими характеристиками, чем предыдущий аналог. Схема простейшего сумматора на операционном усилителе представлена на рисунке 1.2 [1].

Рисунок 2.2 – Сумматор на базе ОУ

В качестве прототипа была выбрана схема вычитания большого числа сигналов (рисунок 2.3). При инвертировании одного из каналов схема также позволяет осуществлять операцию сложения [2].

Рисунок 2.3 – Устройство-прототип

2 РАСЧЕТ НА СТРУКТУРНОМ УРОВНЕ

Функциональная схема многовходового сумматора-вычитателя приведена на рисунке 2.1.

Рисунок 2.1 – Функциональная схема

Можно выделить следующие основные блоки:

- блок вычитания на базе резисторов и ОУ;

- блок суммирования на базе резисторов и ОУ;

- блок управления на основе электронных ключей.

Рассмотрим каждый блок более подробно.

2.1 Блок вычитания

Схема, представленная на рисунке 2.2, позволяет понять принцип действия блока. С математической точки зрения блок реализует следующее выражение [2]:

![]() ,

(2.1)

,

(2.1)

где ai – коэффициент усиления для соответствующего напряжения.

Рисунок 2.2 – Блок вычитания

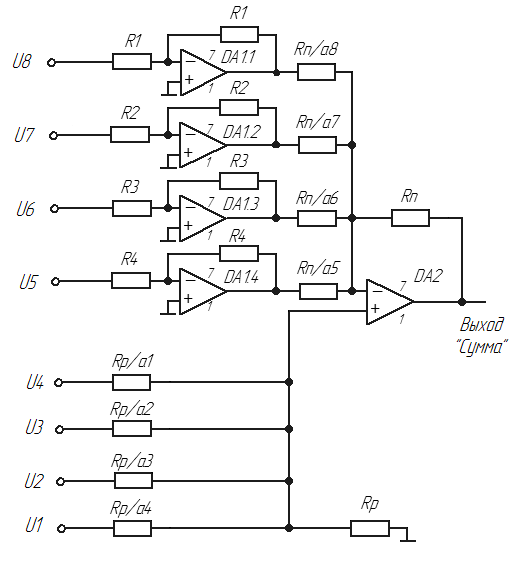

2.2 Блок суммирования

Электрическая схема блока суммирования представлена на рисунке 2.3. Наличие инверторов на входах U5-U8 преобразует выражение (2.1) к виду (2.2), что и позволяет реализовать функцию суммирования. Выражение для суммы [2]:

,

(2.2)

,

(2.2)

где ai – коэффициент усиления для соответствующего напряжения.

Рисунок 2.3 – Блок суммирования

2.3 Блок управления

Блок управления позволяет по сигналу от внешней ЭВМ производить подключение-отключение выходного сигнала к нагрузке. Блок управления состоит из буферного регистра, дешифратора, позволяющего по значению цифрового кода осуществить выбор управляющего канала, и электронных ключей на выходах «Сумма» и «Разность».

3 ВЫБОР И РАСЧЕТ ЭЛЕМЕНТОВ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ

3.1 Блок вычитания

Требования к блоку:

- входные напряжения первого канала 50 мВ, 0.1 В, 0.4 В, 0.5 В;

- входные напряжения второго канала 70 мВ, 0.9 В, 0.2 В, 0.4 В;

- коэффициент усиления 10;

- выходное напряжение, равное разности напряжений входных каналов.

Блок вычитания состоит из резисторов и операционного усилителя. В качестве операционного усилителя используется микросхема К140УД2, имеющая высокое входное напряжение и обеспечивающая функционирование схемы в полосе частот входного сигнала 20 кГц [3]. С математической точки зрения функциональность блока можно описать выражением (2.1). Электрическая схема блока вычитания приведена на рисунке 3.1.

Рисунок 3.1 – Блок вычитания

3.2 Блок суммирования

Требования к блоку:

- входные напряжения первого канала 50 мВ, 0.1 В, 0.4 В, 0.5 В;

- входные напряжения второго канала 70 мВ, 0.9 В, 0.2 В, 0.4 В;

- коэффициент усиления 10;

- выходное напряжение, равное сумме напряжений входных каналов.

Блок сложения отличается от блока вычитания только наличием инвертирующих усилителей для напряжений одного из каналов.

3.3 Регистр

Требования к регистру:

- совместимость с уровнями ТТЛ;

- возможность хранения двух разрядов кода.

Используется микросхема КР531ИР19, удовлетворяющая поставленным требованиям. Запись кода осуществляется синхронно по фронту тактового импульса [3].

Схема включения микросхемы представлена на рисунке 3.2.

Рисунок 3.2 – Регистр

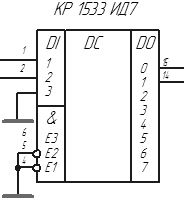

3.4 Дешифратор

Требования к дешифратору:

- совместимость с уровнями ТТЛ;

- возможность декодирования двух битов информации.

Используется микросхема КР1533ИД7, удовлетворяющая поставленным требованиям. Для включения дешифратора необходимо E1&E2&E3=1. Адресный код подается на входы DI, а один из входов E используют в качестве входа электрического сигнала. При этом на два других входа подают логические уровни, при которых выполняется равенство E1&E2&E3=1. Например, если выбрать в качестве входа E3, то на остальные E-входы следует подать логический 0 [3].

Схема включения микросхемы представлена на рисунке 3.3.

Рисунок 3.3 – Дешифратор

3.5 Электронные ключи

Требования к электронным ключам:

- совместимость с уровнями ТТЛ;

- поддержка напряжений до 30 В.

Используется микросхема К101КТ1, удовлетворяющая поставленным требованиям[3]. Вход 2 – сигнал, 3 – управляющий; 8 – питание; 5 – общий.

Схема включения микросхемы представлена на рисунке 3.4.

Рисунок 3.4 – Электронный ключ

4 ЭЛЕКТРИЧЕСКОЕ МОДЕЛИРОВАНИЕ

Проведем моделирование однофазного мостового выпрямителя и сглаживающего фильтра.

Используем для моделирования среду Micro-CAP 7 [4]. Схема блока вычитания приведена на рисунке 4.1.

Рисунок 4.1 – Схема для моделирования

Результат моделирования приведен на рисунке 4.2:

V(3) – напряжение на выходе вычитателя.

Рисунок 4.2 – Результат моделирования

Сравним полученные результаты с теоретическими расчетами. Воспользуемся формулой (2.1). Подставим значения входных напряжений с учетом коэффициентов усиления:

(0.7 + 9 + 2 + 4) – (0.5 + 1 + 4 + 5) = 5.2 (В).

Результат моделирования подтверждает правильность теоретических расчетов.

5 АНАЛИЗ МЕТРОЛОГИЧЕСКИХ ХАРАКТЕРИСТИК

Согласно требованиям технического задания устройство имеет два входных канала. Напряжения первого канала: 50 мВ, 0.1 В, 0.4 В, 0.5 В. Напряжения второго канала: 70 мВ, 0.9 В, 0.2 В, 0.4 В.

Коэффициент усиления 10 обеспечивается отношением сопротивлений резисторов 10 к / 1 к (см. схему электрическую принципиальную).

Используемый операционный усилитель поддерживает полосу частот входного сигнала 20 кГц.

Входные сопротивления схемы превышают 10 кОм, что обеспечивается характеристиками используемого операционного усилителя.

Автоматическое включение-отключение выходного сигнала к нагрузке со стороны внешней ЭВМ обеспечивается использованием буферного регистра, дешифратора и электронных ключей.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

-

Смолов В. Б. Аналоговые вычислительные машины. Учебник для студентов втузов. М., «Высшая школа», 1972.

-

Титце У., Шенк К. Полупроводниковая схемотехника. -М.: Мир, 1982.

-

Интегральные микросхемы: Справочник/ Б.В. Тарабрин, Л.Ф. Лунин, Ю.Н. Смирнов и др.; Под ред. Б.В. Тарабрина. – М.: Радио и связь, 1984.-528 с.

-

Разевиг В.Д. Система схемотехнического моделирования Micro-CAP V - М.: ТОО «СОЛОН», 1997. – 273 с.