- •Итоговый научно-технический отчет

- •Нир 304-5г

- •Реферат

- •Содержание

- •Обозначения и сокращения

- •Введение

- •Разработка алгоритмов и макета комплекса визуально-инерциальной навигации

- •Сравнительный анализ алгоритмов одновременной локализации и построения карты припомощи телекамеры

- •Модель центральной перспективной проекции

- •Описание модели

- •Переход от системы координат камеры к системе координат изображения

- •Однородные координаты

- •Внутренние и внешние параметры калибровки. Уравнение перспективной проекции

- •Структура из движения –StructureFromMotion

- •Обратное представление глубины

- •Проблема масштаба

- •Алгоритмы выделения устойчивых признаков

- •Детектор углов Харриса

- •Окрестность с субпиксельной точностью

- •GoodFeaturesToTrack

- •Выбор аппаратной платформы комплекса визуальной навигации

- •Разработка оптимальных алгоритмов одновременной локализации и построения карты при помощи телекамеры (V-slam) с учетом данных инерциальной навигации

- •Макет модуля визуальной навигации

- •Описание экспериментов и результаты

- •Коридор, движение близкое к прямолинейному.

- •Стенд мобильных роботов, различные траектории

- •Внутренний двор

- •Точность определения пройденного расстояния

- •Точность определения курсового угла

- •Разработка стерео-телевизионного модуля высокого разрешения

- •Литературный обзор по тематике создания телевизионных камер высокого разрешения

- •Структурная схема блока стереоизмерений

- •Описание работы структурной схемы устройства

- •Разработка принципиальной схемы блока стереоизмерений

- •Конструктив блока стереоизмерений, объективы, элементная база коммуникационного устройства

- •Описание конструктивного решения налобного козырька

- •Выбор элементной базы

- •Цифровые телевизионные матрицы

- •Микросхема семейства cyclone III фирмы Altera(сша)

- •Микросхемы синхронной динамической памяти sdram mt48lc4m32b2

- •Топология печатной платы

- •Интеллектуальное программируемое ядро вычисления диспарантности

- •Симуляционное моделирование работы программируемого ядра

- •Симуляционное моделирование алгоритмов направленного движения

- •Макетная печатная плата

- •Интерфейсное программное обеспечение

- •Интерфейсное программное обеспечение низкого уровня

- •Интерфейсное программное обеспечение высокого уровня

- •Анализ возможности реализации разработанных алгоритмов в системах охраны объектов, системах технического зрения для слепых и слабовидящих, беспилотных транспортных систем

- •Описание экспериментов и результаты

- •Заключение

- •Список использованных источников

- •Приложение а. Выписка из протокола заседания нтс

- •Приложение б. Список публикаций

- •Приложение в. Результаты, подлежащие регистрации

Выбор элементной базы

Цифровые телевизионные матрицы

Базовым элементом системы являются КМОП цифровые телевизионные матрицы OIV5610 фирмыOmnivision(США), реализующие оцифровку и передачу цветного телевизионного изображения разрешением до 5 Мпикс (Рисунок 18).

Рисунок 18 Цифровая телевизионная матрица OIV5610 фирмы Omnivision

Основные технические характеристики цифровой телевизионной матрицы OIV5610:

Прибор включает 2592 х 1944 телевизионную цветную матрицу, 10 битный аналогово – цифровой преобразователь продуцирующший на полном разрешении до 4 кадров в секунду

Основные технические особенности цифровой телевизионной матрицы OIV5610:

самокалибровка уровня черного;

режимы кадровой съемки и съемки непрерывного видео;

программируемые режимы экспозициии и автоэкспозиции;

управление коэффициентом усиления и автоматический контроль усиления;

программируемый режим и авторежим баланса белого;

программируемый оконный и масштабируемый режим;

управляемая кадровая частота съемки;

внутренняя или внешняя кадровая синхронизация;

последовательная шина управления;

режим пониженного энергопотребления.

Микросхема семейства cyclone III фирмы Altera(сша)

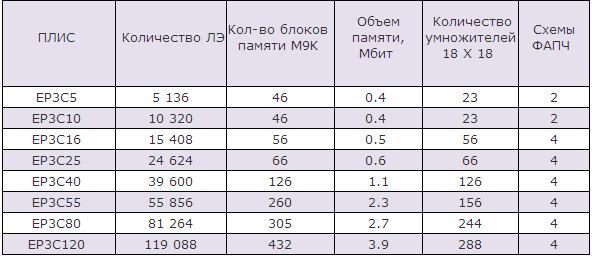

Новое семейство сочетает высокую функциональность, низкое энергопотребление и низкую стоимость. Применение современного технологического процесса 65 нм и программного обеспечения Quartus II, позволяет снизить энергопотребление более чем на 50% по сравнению с семейством Cyclone II. Основные ресурсы семейства Cyclone III представлены в таблицах 1 и 2.

Таблица 1 - Основные ресурсы Cyclone III

Таблица 2 - Корпуса и количество линий ввода/вывода Cyclone III

Объем ресурсов (до 120K ЛЭ, до 4Мбит встроенной памяти, до 288 встроенных умножителей, до 535 линий ввода-вывода) - говорит о высокой функциональности семейства. Архитектура Cyclone III поддерживает встраиваемый программный процессор NIOS II, производительностью свыше 160 DMIPS. ПЛИС семейства Cyclone III отличаются большим разнообразием доступных корпусов – 8 видов (TQFP-144, PQFP-240, FBGA-256, UBGA-256, FBGA-324, FBGA-484, UBGA-484, FBGA-780), имеют 3 градации скорости, 3 градации температурного диапазона, будут выпускаться как в бессвинцовом, так и в свинцовом исполнении.

Микросхемы синхронной динамической памяти sdram mt48lc4m32b2

программируемая длина пачки 1,2,4,8, full page$

автопредзарядка;

режим самоподзарядки;

цикл подзаряда 64ms$

совместимость с LVTTL/

программируемая задержка сигнала CAS 1,2,3 такта

В качестве базового интерфейса, был выбран высокоскоростной интерфейс USB2.0. в качестве базовой микросхемы реализующий данный интерфейс, была выбрана микросхема CY7C68013А фирмы Cypress.

Основные характеристики:

приемопередатчик USB 2.0

аппаратный контроллер SIE (Serial Interface Engine)

память FIFO (4Kб, 8/16-битная внешняя шина)

усовершенствованное ядро 8051 (48МГц)

возможность подключения внешней памяти

USART

3 таймера

IIC

программируемый периферийный интерфейс GPIF

Отличительные черты нового семейства EZ_USB FX2LP по сравнению с EZ-USB FX2:

малое энергопотребление: до 85 мА во всех режимах;

большая емкость внутреннего ОЗУ: 16кБ;

наличие функции генерации кода коррекции ошибок ECC в соответствии со спецификацией SmartMedia;

два дополнительных входа I/O для 68015A;

автоматическая генерация пакетов нулевой длительности при изохронных передачах в режиме Hi-speed.

Блок SIEреализует протокол USB аппаратно. Он выделяет данные из пакетов и помещает их в FIFO-буферы четырех конечных точек. Внешнее микропроцессорное устройство может осуществлять обмен данными с микросхемой как с обычной памятью FIFO.

Программируемый периферийный интерфейс GPIFпозволяет задать формы сигналов квитирования, сопровождающих данные. С его помощью могут быть реализованы различные параллельные интерфейсы: ATA, UTOPIA, EPP, PCMCIA и др.

Усовершенствованное ядро 8051(команда выполняется за 4 такта) используется для инициализации режимов работы контроллера SIE и программируемого периферийного интерфейса GPIF. Ядро 8051 работает под управлением программы, размещенной во внутренней оперативной памяти. Загрузка программы может осуществляться из внешней EEPROM через интерфейс IIC или из персонального компьютера через USB.

Во время непосредственного выполнения обмена данными между шиной USB и внешним микропроцессорным устройством внутреннее ядро 8051 может не использоваться.