- •Министерство образования и науки российской федерации федеральное агентство по образованию

- •Архитектура эвм

- •Часть 2, 3

- •Глава 5. Уровни организации эвм.

- •5.1. Машинный уровень организации

- •5.1.1. Форматы команд.

- •5.1.2. Адресация данных.

- •6.2.1.1. Прямые способы адресации.

- •6.2.1.2. Непрямые способы адресации:

- •3. Автоинкрементная, автодекрементная (индексная) адресация.

- •5.1.3. Адресация команд.

- •5.1.4. Типы машинных команд.

- •5.1.5. Команды обработки данных.

- •5.2. Микропрограммный уровень организации эвм.

- •5.2.1. Принцип микропрограммного управления.

- •5.2.2. Описание функциональных микропрограмм.

- •5.2.3 Набор микроопераций и микроэлементов.

- •1°. Шина.

- •2°. Регистры.

- •3°. Счетчики.

- •4°. Сумматоры.

- •5°. Преобразователи кодов.

- •6°. Вычисление значений логических условий.

- •7°. Комбинированные операционные элементы.

- •5.2.4. Структурное построение и функционирование микропрограммных устройств управления.

- •5.3. Системный уровень организации

- •Глава 6. Организация памяти вс.

- •6.1. Виды запоминающих устройств. Иерархия памяти.

- •6.2. Организация оперативной памяти.

- •Глава 7. Виды и архитектура процессоров.

- •7.1. Матричный процессор.

- •7.2. Процессор с конвейеризацией команд и процессор с конвейеризацией операций.

- •7.3. Суперскалярный процессор.

- •7.4. Коммуникационный процессор

- •7.5. Архитектуры cisc и risc.

- •Глава 8. Организация связей в эвм.

- •Глава 9. Основные классы современных параллельных компьютеров.

- •9.1. Симметричные мультипроцессорные системы (smp) (Symmetric Multi-Processing)

- •9.2. Массивно-параллельные системы (мрр) (Massively Parallel Processing)

- •9.3. Системы с неоднородным доступом к памяти (numa) (non uniform memory access)

- •9.4. Параллельно-векторные системы (pvp)

- •9.5. Кластерные системы

- •Глава 10. Межпроцессорные сети связи в эвм mpp типа (Interconnect Network)

- •Глава 11. Эффективная организация дисковых накопителей при организации параллельного и независимого доступа

- •11.1. Общие вопросы организации.

- •11.2. Время обслуживания.

- •11.3. Затраты и целесообразность.

- •11.4. Технология i2o в raid-контроллерах.

- •Глава 12. Параллельные и распределенные системы Введение.

- •Недостатки мультипроцессоров

- •Pc необходимо объединять в сети, поскольку возникает

- •12.1. Операционные системы мультипроцессорных эвм

- •12.1.1 Процессы и нити

- •12.1.2. Взаимодействие процессов

- •12.1.3 Планирование процессоров

- •12.2. Коммуникации в распределенных системах

- •Локальные сети.

- •Клиент-сервер

- •Удаленный вызов процедур

- •Обмен сообщениями между прикладными процессами send, receive (адресат/отправитель, [тэг], адрес памяти, длина)

- •12.3. Синхронизация в распределенных системах

- •12.3.1. Синхронизация времени

- •Логические часы.

- •Физические часы.

- •12.3.2 Выбор координатора

- •Алгоритм "задиры"

- •Круговой алгоритм.

- •12.3.3 Взаимное исключение Централизованный алгоритм

- •Алгоритм с круговым маркером

- •Алгоритм древовидный маркерный (Raymond)

- •Децентрализованный алгоритм на основе временных меток.

- •Алгоритм широковещательный маркерный (Suzuki-Kasami).

- •12.3.4. Координация процессов

- •12.4. Распределенные файловые системы

- •12.4.1 Архитектура распределенных файловых систем

- •Интерфейс файлового сервера

- •5.1.2 Интерфейс сервера директорий

- •Различают две формы прозрачности именования

- •Семантика разделения файлов

- •12.4.2 Реализация распределенных файловых систем

- •Использование файлов

- •5.2.2 Структура системы

- •Кэширование

- •Когерентность кэшей.

- •Размножение

- •12.4.3. Пример: Sun Microsystems Network File System (nfs)

- •Архитектура nfs.

- •Протоколы nfs.

- •Реализация nfs

- •Список литературы

- •Оглавление:

Министерство образования и науки российской федерации федеральное агентство по образованию

ПЕНЗЕНСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

Архитектура эвм

Учебное пособие

Часть 2, 3

ПЕНЗА 2007

УДК 517.5

Продолжение краткого курса лекций по первому из трех разделов дисциплины «Архитектура ЭВМ и системное программное обеспечение».

Методическое пособие подготовлено на кафедре «Высшая и прикладная математика» и предназначены для студентов специальности «Прикладная математика», а также студентов других специальностей, изучающих архитектуру вычислительных машин с точки зрения возможности параллельных вычислений.

Составитель Ю.Ф. Захарова

Рецензент -

Глава 5. Уровни организации эвм.

Основой функционирования любой ЭВМ является ее способность выполнять заданные действия. Аппаратные средства любой ЭВМ способны выполнять только ограниченный набор сравнительно простых команд. Эти примитивные команды примитивные команды составляют так называемый машинный язык машины. Говоря о сложности аппаратуры компьютера, машинные команды целесообразно делать как можно проще, но примитивность большинства машинных команд делают их использование неудобным и трудным. Вследствие чего разработчики вводят другой набор команд более удобный для человеческого общения (языки более высокого уровня).

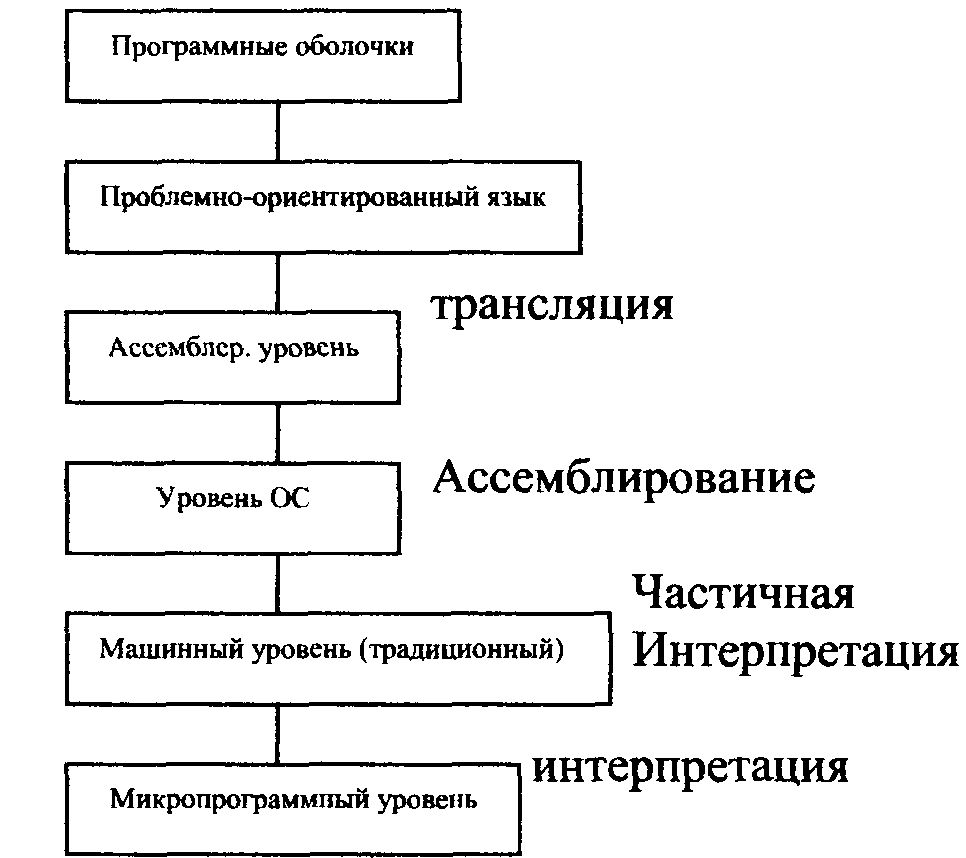

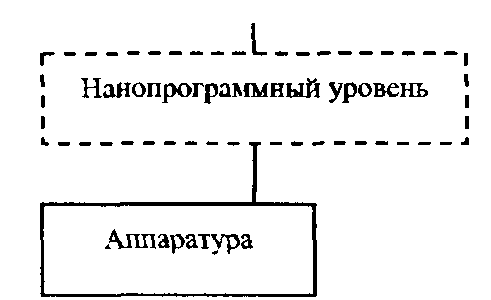

Рисунок 7 показывает, что между языками программирования и существующей виртуальной машиной существует тесная связь, но в общем случае она является нелинейной. Пользователь, который работает на каком-то уровне в принципе Может и не знать процессы, происходящие на других уровнях организации, но для составления эффективных программ, необходимо знание более низких языков программирования. Большинство современных ЭВМ включают 6-7 уровней виртуализации. Нижние уровни, начиная с машинного более консервативны к изменениям.

Рис. 7

Многие коммерческие ЭВМ принципиально могут не иметь уровня нанопрограммирования, но и даже микропрограммирования (по крайней мере, на уровне пользователя). В современных ЭВМ машинные команды, как правило, интерпретируются с помощью микропрограмм. Уровень ОС обычно является смешанным уровнем, т.к. большинство супервизорных команд являются командами машинного уровня. В состав уровня ОС дополнительно включаются команды, которые фактически являются некоторыми типовыми программами машинного уровня (команды ввода-вывода, переключения между программами). Во многих ЭВМ были варианты, когда отдельные программы ОС непосредственно интерпретируются микропрограммами. В современных ВМ прослеживается тенденция все боле тесной связи уровня ОС с микропрограммным уровнем. Можно также найти массу команд уровня ОС, реализованных, на уровне ассемблирования. Простые пользователи, как правило, ограничиваются уровнем изучения начиная с машинного. Нижние уровни необходимы для разработчиков.

5.1. Машинный уровень организации

5.1.1. Форматы команд.

Любая команда ЭВМ представляет собой некоторую упорядоченною последовательность битов, которая определяет:

1. Операцию, инициируемую этой командой.

2. Адреса операндов участвующих в этой операции.

Поэтому в большинстве ЭВМ команда имеет операционно-адресную систему.

![]()

В операционной части с точки зрения машинного представления записывается код операции. А в адресной части задается код адресов операндов. Он содержит информацию не только об адресах операндов и результата операции, но и об адресе следующей команды.

Под форматом команды понимается состав, назначение и расположение отдельных полей команды.

Развитие структуры происходит лишь вследствие уменьшения поля адреса (SISC процессоры). С появлением RISC процессоров произошел возврат к расширенной адресности системы команд (о процессорах SISC и RISC типа см. также параграф 8.5.). Говоря о базовом уровне, речь идет о SISC процессорах. Первоначально система команд имела следующий формат:

![]() ,

где СчАК - счетчик адреса команд. * -

операция (х) содержимое адреса х.

,

где СчАК - счетчик адреса команд. * -

операция (х) содержимое адреса х.

В каждой команде задается адрес следующей команды (это самый универсальный вариант), но длина такой команды велика. При такой системе команд их можно располагать в любом порядке, но обычно стараются расположить последовательно. Такой порядок называется естественным, но при естественном расположении необходимость в поле А4 отпадает. Следовательно, формат приобрел вид:

![]()

А3 := (Al)*(A2) СчАК := (СчАК)+1

Даже переход к такому формату слабо уменьшает длину команды. Большинство вычислений имеет рекуррентную схему вычислений, следовательно, систему команд можно сделать двух адресной.

( Al)

:= (Al)*(A2) СчАК := (СчАК)+1

Al)

:= (Al)*(A2) СчАК := (СчАК)+1

Такая схема вычислений является основной для современных ЭВМ.

Но развитие шло и в направление развития процессора и его внутренней памяти, это привело к тому, что в процессорах появились специальные регистры, которые всегда используются в вычислениях.

АСС := (ACC)*Y

Е сли

использовать аккумуляторный принцип,

то для системы команд достаточно

использовать один адрес.

сли

использовать аккумуляторный принцип,

то для системы команд достаточно

использовать один адрес.

Основная масса команд SISC процессора является одно и двух адресная. В некоторых случаях команды можно не адресовать, если команда задает операцию над фиксированными адресами (например, действие над аккумуляторами), в формате таких команд адресное поле отсутствует. Команда называется безадресной или нульадресной. Качественный сравнительный анализ показывает:

1. Короткие команды предпочтительнее длинных, так как занимают меньше памяти. Любая память ЭВМ характеризуется скоростью передачи (пропускной способностью). Если физическое быстродействие фиксировано, то количество выбираемых из памяти команд, обратно пропорционально длине команды. А значит скорость работы процессора для коротких команд больше, чем для более длинных. Короткие команды увеличивают производительность процессора. Для большинства современных ЭВМ процессор работает быстрее памяти, следовательно, чтобы обеспечить высокую производительность, нужно увеличить количество команд извлекаемых из памяти за один цикл обращения.

2. Форматы команд должны обеспечивать

достаточное пространство для задания

всех операций (если система компьютера

включает в себя N операций

![]() -округление в большую сторону).

-округление в большую сторону).

3. Длина команды должна быть кратна длине базовой структурной информационной единице (т.е. либо команда должна занимать целое число байт или слов, или в одном слове должно находится целое число команд). Если в одном слове не целое число команд, то либо память недоиспользуется, либо усложняются процедуры выбора команд. Кроме того, длина команды должна выбираться с учетом длины кодов символов обрабатываемых данных.

4. Длина адресного поля команды очень

тесно связана с организацией памяти

компьютера, а также с размером адресного

пространства памяти, которую можно

непосредственно адресовать в памяти

компьютера. Если память включает в себя

М адресных элементов, тогда минимальная

длина адресного поля:

![]() .

Если исходить от фиксированной длины

адресного поля, то емкость памяти будет

зависеть от того, какова минимально

адресуемая единица информации.

.

Если исходить от фиксированной длины

адресного поля, то емкость памяти будет

зависеть от того, какова минимально

адресуемая единица информации.