- •Лабораторная работа №16

- •1. Монтаж и исследование озу на ис к155ру2.

- •2. Монтаж и исследование озу на ис кр541ру2. Введение.

- •Задание по вопросу 1.

- •1. 2. Написать таблицу соединений для схемы рис.10. Напомним рекомендации по

- •1.8. Сравнить записанную в озу и считанную из озу информацию.

- •1.9. Найти неисправность, внесенную в схему преподавателем.

- •1.16. Считать из озу записанную информацию.

- •1.17. Сравнить записанную в озу и считанную из озу информацию.

- •1.18. Найти неисправность, внесенную в схему преподавателем.

- •Перейдем к практической части.

- •1.26. Определить время считывания tсч с максимальной точностью, обеспечиваемой осциллографом.

- •1.27. Выключить блок питания. Демонтировать схему. Задание по вопросу 2.

- •Литература.

Лабораторная работа №16

TEMA: Исследование работы оперативного ЗУ

на ИС К155РУ2 или на ИС КР541РУ2.

ВОПРОСЫ: Введение.

1. Монтаж и исследование озу на ис к155ру2.

2. Монтаж и исследование озу на ис кр541ру2. Введение.

Запоминающие устройства (ниже ЗУ) ЭВМ предназначены для записи, хранения и выдачи различной информации, представленной цифровым кодом. К такой информации относятся исходные данные для решения задач, промежуточные и окончательные результаты вычислений, константы и табличные данные, используемые в вычислительном процессе и, конечно же, сама программа работы ЭВМ.

Запоминающие устройства принято классифицировать по назначению (внутренние и внешние), по характеру поиска информации (адресные и безадресные, или ассоциативные), по способу доступа (произвольный, последовательный, циклический), по способу хранения информации (статические динамические ЗУ).

Внутренние ЗУ предназначены для возможно быстрой обработки информации. Под обработкой информации понимается ее запись и считывание либо только считывание. Внутренние ЗУ в зависимости от выполняемых функций делятся на оперативные (ОЗУ), сверхоперативные (СОЗУ) и постоянны (ПЗУ).

Внешние ЗУ предназначены для хранения больших объемов информации. Примерами таких ЗУ являются накопители на магнитных дисках (НМД), накопители на магнитных лентах (НМЛ) и т.п. Быстродействие внешних ЗУ на несколько порядков меньше, чем у внутренних ЗУ.

По характеру поиска информации ЗУ делятся на адресные и безадресные или ассоциативные. Адресные ЗУ состоят из ячеек памяти, в которых хранится записанная информация. Каждой ячейке присваивается свой номер ил адрес. Поиск информации в адресных ЗУ осуществляется по адресам ячеек памяти. Поиск информации в безадресных или, как еще их называют, ассоциативных ЗУ выполняется не по адресам, а по некоторым признакам искомой информации. Пример характерной задачи таких ЗУ: осуществляет поиск и считывание информации из таких ячеек памяти, в которых значение разряд (ai) равно "1", a (aj) равно "0".

По способу доступа к информации запоминающие устройства делятся на ЗУ с произвольным, последовательным и циклическим доступом. В ЗУ с произвольным доступом или, как их еще называют, ЗУ с произвольной выборкой (ЗУПВ) информация записывается или считывается непосредственно по любому адресу. В ЗУ с последовательным доступом, например, в накопителе на магнитной ленте (НМЛ), требуемый участок записи или считывания находится путем последовательной перемотки ленты. В ЗУ с циклическим доступом, например, в накопителе на магнитном диске, информация из нужной ячейки считывается только в определенные моменты времени, разделенные, циклическим интервалом работы ЗУ. Запоминающие устройства с произвольной выборкой (ЗУПВ) являются наиболее быстродействующими, так как в них обращение к нужной ячейке памяти не зависит от ее адреса, а определяется лишь быстродействием коммутационных схем управления.

По способу хранения информации, запоминающие устройства делятся на статические и динамические ЗУ. В статических ЗУ цифровой код остается неподвижным относительно носителя информации в течение всего времена хранения. В таких ЗУ в качестве носителя информации обычно используются триггеры. В динамических ЗУ цифровые коды находятся в непрерывном движении относительно носителя информации.

В данной лабораторной работе мы должны исследовать работу запоминающих устройств на базе ИС К155РУ2 и КР541РУ2. В соответствии с рассмотренной выше классификацией эти ЗУ являются внутренними, точнее, оперативными, адресными, с произвольной выборкой, статистическими. На рис.1 представлена логическая структура таких ЗУ; на рис.2-логическая структура ячейки памяти ИС К155РУ2.

Микросхема К155РУ2 является оперативным ЗУ со схемами управления и полной дешифрацией адреса. Общий объем ее памяти 16-ти и 4-х-разрядных слов. Микроструктура данной ИС в соответствии с рис.2 имеет встроенный стробируемый дешифратор (ДС)4-х-разрядного двоичного кода адреса, выбирающий одну из 16-ти 4-х-разрядных линеек. При наличии высокого уровня (лог."1") на входе стробирования (V) не выбирается ни одна линейка памяти. Работа ИС описывается следующей таблицей.

V |

W |

D |

Режим работы |

C |

1 |

1 |

0 |

хранение |

1 |

0 |

1 |

0 |

считывание |

инверсный код выбранного числа |

0 |

0 |

1 |

запись 1 |

0 |

0 |

0 |

0 |

запись 0 |

1 |

1 1 |

0 0 |

1 0 |

запрет обращения |

0 |

1 |

Рис.3 Режим работы ИСК155ПУ2

Кроме дешифратора (DC) микросхема включает матрицу (М) из 64 элементов памяти, четыре усилителя записи и четыре усилителя считывания. Вход разрешения выборки (V) несет функцию запрета при подаче на него напряжения высокого уровня (лог."1"). В этом случае нельзя произвести ни запись в ячейку, ни считывание из нее. Запись информации осуществляется прямым кодом параллельно по четырем информационным вводам D1-D4. При этом на входы разрешения выборки (V) и разрешения записи (W) должен быть подан низкий уровень напряжения (лог. "0"), а на адресных входах А0-А3 выставлен прямой код номера линейки, в которую выполняется запись. Считывание информации из линейки N осуществляется при подаче на адресные входы А0-А3 прямого кода, соответствующего номеру N, а также при подаче на вход выборки (V) напряжения низкого уровня (лог."0") и на вход разрешения записи (W) напряжения высокого уровня (лог."1"). Записанная информация считывается параллельно по четырем выходам Q1-Q4 в коде, инверсном записанному. Выходные каскады усилителей считывания выполнены по схеме с открытым коллектором, что дает возможность объединять, в монтажное ИЛИ информационные входы различных ИС.

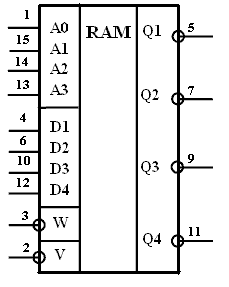

Микросхема К155РУ2 имеет следующее условное графическое изображение

и назначение выводов:

Рис.4. Условное графическое обозначение ИС К155РУ2 и назначение ее выводов.

Можно отметить, что многие перечисленные выше особенности функционирования

ИС К155РУ2 отражены в ее графическом обозначении. В частности, из графического обозначения (наличие "кружочков") следует, что сигналы разрешения выборки (V) и разрешения записи (W) подается низким уровнем напряжения (лог. "0"); выходная информация представляется в инверсном коде. Рассмотрим ячейку памяти на ИС КР541РУ2. Данная микросхема является оперативным ЗУ со схемами управления и полной дешифрацией адреса. Объем ее памяти -1024 4-разрядных слов. На рис. 5 представлена логическая структура ИС КР541РУ2, которая включает дешифратор адреса строк DCS, дешифратор адреса столбца DCК, устройство управления CV, матрицу запоминающих элементов, разбитую на 1024 секции по четыре запоминающих элемента в каждой, а также разрядные формирователи и предусилители BD.

Выходы ИС КР541РУ2 могут находиться в трех состояниях. Два состояния - активные; они соответствуют лог."0" или лог. "1". Третье состояние - состояние высокого выходного импеданса (сопротивления). Выходы микросхемы переходят в активное состояние только в режиме считывания. В остальных режимах (записи и хранения) они находятся в третьем состоянии.

В режиме считывания на вход записи (WE) подается высокий уровень напряжения (лог. "1") , а на вход выборки (CS) - низкий уровень напряжения (лог."0").

В режиме записи на вход записи (WE) и на вход выборки (CS) подается низкий уровень напряжения (лог."0").

Особенность: в режиме записи выводы D1-D4 работают как информационные входы; в режиме считывания выводы D1-D4 работают как информационные выходы, т.е. входы и выходы рассматриваемой ИС мультиплексированы.

Обобщая сказанное, можно составить таблицу, описывающую работу ИС КР541РУ2 (см.рис.6).

CS |

WE |

Режим работы |

Состояние выходов D |

1 |

Х |

хранение |

высокий выходной импеданс |

0 |

1 |

считывание |

активное |

0 |

0 |

запись |

|

Рис.6. Режимы работы ИС КР541РУ2.

Примечание символ «х» обозначает безразличное состояние (лог. «0» или лог. «1»)

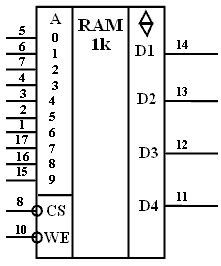

На рис.7. представлено условное графическое обозначение и назначение выводов ИСКР541РУ2.

Рис.7. Условное графическое обозначение ИС КР541РУ2 и назначение ее выводов.

Отметим,

что многие

перечисленные

выше особенности функционирования ИС

КР541РУ2 отражены в

ее

графическом обозначении. В частности,

из графического обозначения (наличие

"кружочков") следует, что сигналы

выборки (CS)и

записи (WE)

подаются низким уровнем напряжения

(лог."0"); выходная информация не

инвертируется. Наличие значка " "

говорит о том, что выводы ИС могут

находиться в

трех

состояниях.

Отметим,

что многие

перечисленные

выше особенности функционирования ИС

КР541РУ2 отражены в

ее

графическом обозначении. В частности,

из графического обозначения (наличие

"кружочков") следует, что сигналы

выборки (CS)и

записи (WE)

подаются низким уровнем напряжения

(лог."0"); выходная информация не

инвертируется. Наличие значка " "

говорит о том, что выводы ИС могут

находиться в

трех

состояниях.

Кратко рассмотрим соотношения работы ИС КР541РУ2.

Обычно при записи в ОЗУ сначала выставляется адрес и информация, затем с некоторой задержкой подаются сигналы разрешения записи (WE) и выборки (CS). Для ИС КР541РУ2 адрес записи, сама информация, а также сигналы разрешения записи (WЕ) и разрешения выборки (CS) могут подаваться одновременно.

При считывании информации из ОЗУ на ИС КР541РУ2 адрес считывания и сигнал разрешения выборки СS могут подаваться одновременно.

Длительность сигналов WE и CS должна быть не менее 60 нс.

Цикл записи (считывания), определяемый как время от момента начала первого обращения к памяти с целью записи (считывания) и до момента начала второго обращения, должен быть не менее 140 нс.

Кратко рассмотрим организацию матрицы элементов памяти ИС ОЗУ.

Основной частью оперативной памяти ( в том числе и на ИС КР541РУ2, см.рис.5) является матрица запоминание элементов. Как правило, каждый элемент названной матрицы биполярного исполнения для ОЗУ статического типа представляется такой электрической схемой:

Рис.8. Электрическая схема биполярного элемента памяти ОЗУ статического типа.

Элемент

памяти построен на базе триггера на

двух многоэмиттерных транзисторах.

Выборка элемента производится с помощью

двух адресных шин, одна из которых

является выходом дешифратора строк

DCS,

другая - выходом дешифратора столбца

DCK.

Эти шины соединены с эмиттерными

выводами обоих

транзисторов.

Третий эмиттерный вывод служит для

считывания и записи информации в элемент

памяти. В элементе памяти один из

транзисторов находиться в проводящем

состоянии, а другой - в закрытом. Если

элемент не выбран, то хотя вы на одной

адресной шине, и, следовательно, хотя

бы

на

одном эмиттере транзистора VT1

и хотя бы на одном эмиттере транзистора

VT2,

будет напряжение низкого (L)

уровня. Выборка элемента происходит

путем подачи напряжения высокого

(Н) уровня на обе адресные шины. При этом

через считывающий эмиттер открытого

транзистора будет протекать больший

ток,

чем через считывающий эмиттер

закрытого транзистора. Этот ток

усиливается в одном из двух усилителей

считывания, стоящих на выходе информационной

шины D

либо D. Считывание не приводит к потере

информации, так как состояние элемента

не изменяется под действием напряжения

высокого (Н) уровня, которое появляется

на адресных шинах.

Элемент

памяти построен на базе триггера на

двух многоэмиттерных транзисторах.

Выборка элемента производится с помощью

двух адресных шин, одна из которых

является выходом дешифратора строк

DCS,

другая - выходом дешифратора столбца

DCK.

Эти шины соединены с эмиттерными

выводами обоих

транзисторов.

Третий эмиттерный вывод служит для

считывания и записи информации в элемент

памяти. В элементе памяти один из

транзисторов находиться в проводящем

состоянии, а другой - в закрытом. Если

элемент не выбран, то хотя вы на одной

адресной шине, и, следовательно, хотя

бы

на

одном эмиттере транзистора VT1

и хотя бы на одном эмиттере транзистора

VT2,

будет напряжение низкого (L)

уровня. Выборка элемента происходит

путем подачи напряжения высокого

(Н) уровня на обе адресные шины. При этом

через считывающий эмиттер открытого

транзистора будет протекать больший

ток,

чем через считывающий эмиттер

закрытого транзистора. Этот ток

усиливается в одном из двух усилителей

считывания, стоящих на выходе информационной

шины D

либо D. Считывание не приводит к потере

информации, так как состояние элемента

не изменяется под действием напряжения

высокого (Н) уровня, которое появляется

на адресных шинах.

Считывающие эмиттеры служат для перевода элемента в новое состояние. На эмиттер транзистора, который в новом состоянии должен быть проводящим, подается низкое напряжение (L), а на эмиттер транзистора, который должен запереться, подается высокое напряжение (Н-уровень). Этот транзистор запирается, когда на адресные шины подается напряжение Н-уровня. Другой транзистор будет открываться, так как на его базу через коллекторный резистор подается напряжение Н-уровня.

Перейдем к практической части работы.