- •Практическая работа №1 «Архитектура пк и назначение ее основных блоков.»

- •Определение пк. О чем говорит слово персональный?

- •Классификация средств пк (Hardware, Software)

- •Фон Неймановская архитектура эвм, принципы фон Неймана,

- •Назначение cpu и npu, состав и назначение составных узлов cpu (алу, уу, регисторов) ?

- •Назначение оперативной памяти (Схема взаимодействия озу, внешней памяти, устройств ввода и вывода) ?

- •Назначение «пзу», характеристика модулей пзу: (bios, post, setup, bnjk) ?

- •Определение конфигурации пк : (Проходила практическая работа), (скрин работы, свойства пк) ?

- •Понятие открытой архитектуры и ее признаки ?

- •Практическая работа №2 «Устройство системной (материнской) платы»

- •4.Назначение cmos памяти?

- •5.Назначение чипсета, схема материнской платы с чипсетом(северный мост и южный мост)

- •6.Единицы измерения компьютерной информации.

- •7.Понятие интерфейса и его компоненты. Системная шина и шины расширения. Их назначение?

- •Персональные компьютеры

- •Промышленные компьютеры

- •8.Шина расширения (рисунок,таблица)

- •9.Порты ввода-вывода.

- •Привести таблицу с техническими характеристиками портов ввода вывода для каждого из них указов его конструкцию

- •12.Какие разьемы на материнской плате служат для подсоединение кнопок и индикатора передней платы.

- •1.В чем заключается назначение пзу

- •3.Назначения модулей входящей в состав пзу ?

- •4.Привести строения меню bios Setup и и назначение ее компанентов и их опций ?

- •Интерфейс bios (cmos) Setup Utility

- •Основные разделы bios Setup с колоночным главным меню (синий фон)

- •Основные разделы bios Setup с горизонтальным главным меню (серый фон)

- •5. Привести таблицы со звуковыми сигналами программы post пзу различных производителей ?

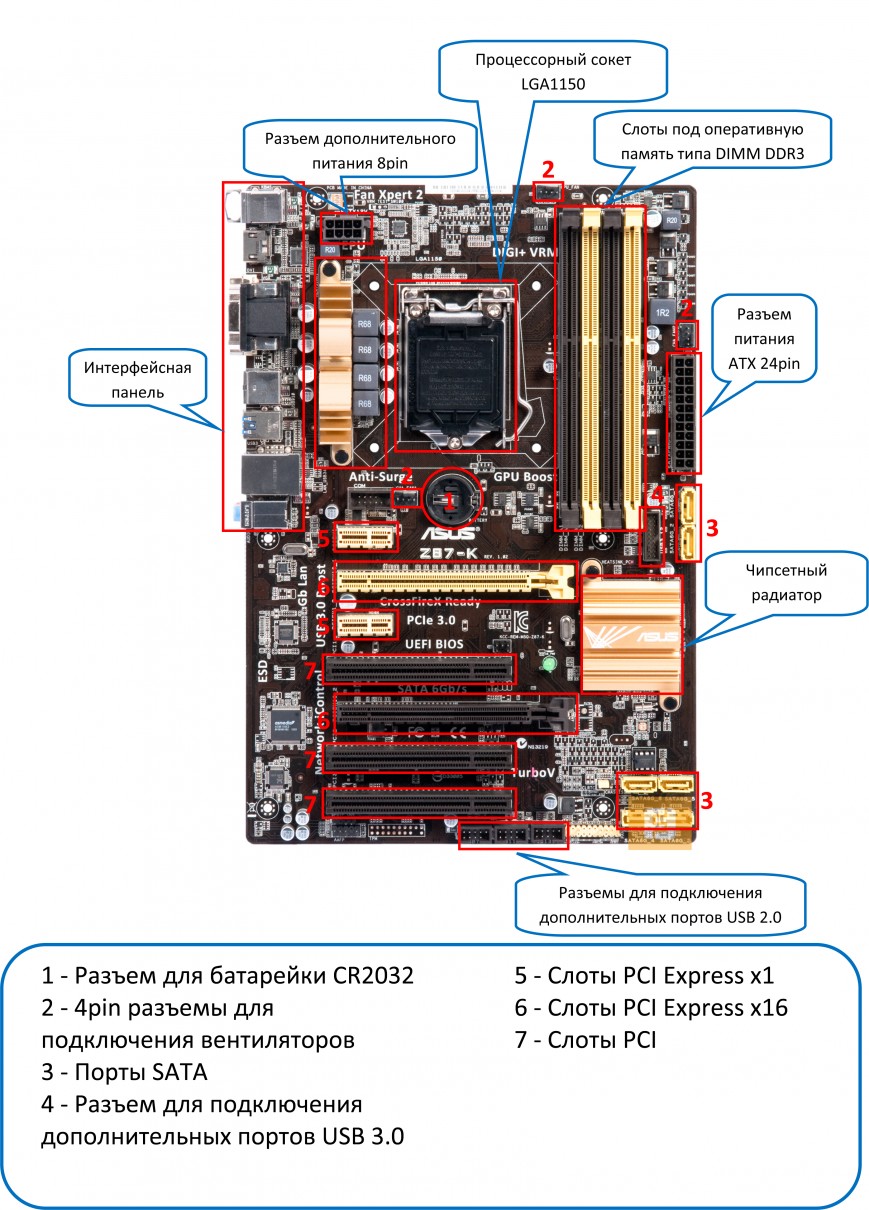

Практическая работа №2 «Устройство системной (материнской) платы»

Привести схему устройство материнской платы с указанием размещенных на ней элементов (мануал материнской планы)

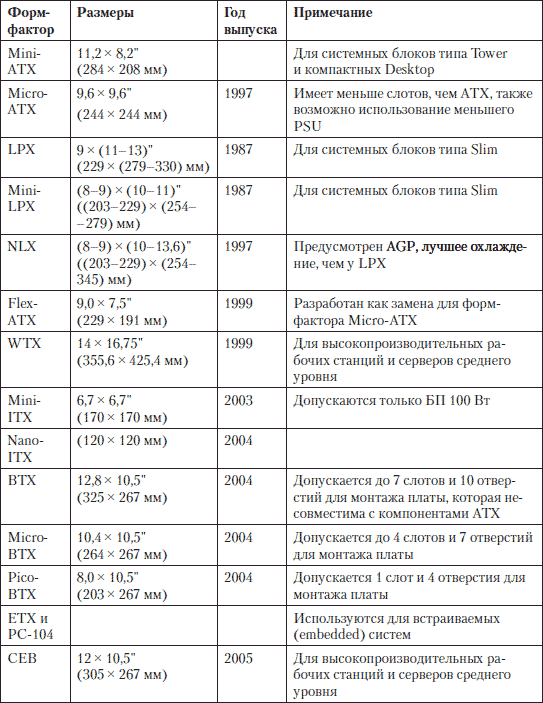

Привести таблицу с форм факторами материнской планы

Форм-фактор (от англ. form factor) — стандарт, задающий габаритные размеры технического изделия, а также описывающий дополнительные совокупности его технических параметров, например форму, типы дополнительных элементов размещаемых в/на устройстве, их положение и ориентацию.

Конструкция модулей оперативной памяти (таблица, рисунок, краткая хар-ка модуля:SIMM, DIMM, DIMM DDR1,DDR2,DDR3,DDR4)

SIMM отличаются скоростью работы. Обычно в ПК на процессорах 486 применялись устройства на 70 нс, хотя для процессоров типа 486DX4-100, 486DX4-120, 486DX4-133, Pentium, рекомендуется использовать SIMM как минимум на 60 нс.

Назначение контактов модуля |

||

№ |

Название |

Описание |

1 |

Vcc |

Напряжение питания +5 В |

2 |

CAS# |

Строб адреса столбца |

3 |

DQ0 |

Линия данных 0 |

4 |

A0 |

Адресная линия 0 |

5 |

A1 |

Адресная линия 1 |

6 |

DQ1 |

Линия данных 1 |

7 |

A2 |

Адресная линия 2 |

8 |

A3 |

Адресная линия 3 |

9 |

GND |

Общий |

10 |

DQ2 |

Линия данных 2 |

11 |

A4 |

Адресная линия 4 |

12 |

A5 |

Адресная линия 5 |

13 |

DQ3 |

Линия данных 3 |

14 |

A6 |

Адресная линия 6 |

15 |

A7 |

Адресная линия 7 |

16 |

DQ4 |

Линия данных 4 |

17 |

A8 |

Адресная линия 8 |

18 |

A9 |

Адресная линия 9 |

19 |

A10 |

Адресная линия 10 |

20 |

DQ5 |

Линия данных 5 |

21 |

WE# |

Запись данных |

22 |

GND |

Общий |

23 |

DQ6 |

Линия данных 6 |

24 |

A11 |

Адресная линия 11 |

25 |

DQ7 |

Линия данных 7 |

26 |

QP |

Линия данных 9 (контроль четности, выход) |

27 |

RAS# |

Строб адреса строки |

28 |

CASP# |

Строб адреса столбца четности |

29 |

DP |

Линия данных 9 (контроль четности, вход) |

30 |

Vcc |

Напряжение питания +5 В |

Небуферизованный модуль DIMM может содержать микросхемы памяти типа FPM DRAM, EDO DRAM, BEDO DRAM, SDRAM. Модули могут иметь 64 бит или 72 бит (контроль четности), а также 72 бит и 80 бит для ECC. Конструкция модулей предусматривает автоматическое их распознавание компьютером. Для этого используются специальные ключи - пазы в контактной линейке. Левый - буферизованный или небуферизованный, правый - напряжение питания - 5 В или 3,3 В.

|

|

|

|

|

Контакт |

Обозначение |

Контакт |

Обозначение |

|

1 |

Общий |

85 |

Общий |

|

2 |

Бит данных 0 |

86 |

Бит данных 32 |

|

3 |

Бит данных 1 |

87 |

Бит данных 33 |

|

4 |

Бит данных 2 |

88 |

Бит данных 34 |

|

5 |

Бит данных 3 |

89 |

Бит данных 35 |

|

6 |

+3,3 В |

90 |

+3,3 В |

|

7 |

Бит данных 4 |

91 |

Бит данных 36 |

|

8 |

Бит данных 5 |

92 |

Бит данных 37 |

|

9 |

Бит данных 6 |

93 |

Бит данных 38 |

|

10 |

Бит данных 7 |

94 |

Бит данных 39 |

|

11 |

Бит данных 8 |

95 |

Бит данных 40 |

|

12 |

Общий |

96 |

Общий |

|

13 |

Бит данных 9 |

97 |

Бит данных 41 |

|

14 |

Бит данных 10 |

98 |

Бит данных 42 |

|

15 |

Бит данных 11 |

99 |

Бит данных 43 |

|

16 |

Бит данных 12 |

100 |

Бит данных 44 |

|

17 |

Бит данных 13 |

101 |

Бит данных 45 |

|

18 |

+3,3 В |

102 |

+3,3 В |

|

19 |

Бит данных 14 |

103 |

Бит данных 46 |

|

20 |

Бит данных 15 |

104 |

Бит данных 47 |

|

21 |

Разряд четности 1 |

105 |

Не соединен |

|

22 |

Разряд четности 2 |

106 |

Не соединен |

|

23 |

Общий |

107 |

Общий |

|

24 |

Не соединен |

108 |

Не соединен |

|

25 |

Не соединен |

109 |

Не соединен |

|

26 |

+3,3 В |

ПО |

+3,3 В |

|

Контакт |

Обозначение |

Контакт |

Обозначение |

|

27 |

Write Enable |

111 |

Column Address Strobe |

|

28 |

I/O Mask 0 |

112 |

Byte Mask 4 |

|

29 |

I/O Mask 1 |

113 |

Byte Mask 5 |

|

30 |

SO |

114 |

SI |

|

31 |

Зарезервирован |

115 |

Row Address Strobe |

|

32 |

Общий |

116 |

Общий |

|

33 |

Разряд адреса 0 |

117 |

Разряд адреса 1 |

|

34 |

Разряд адреса 2 |

118 |

Разряд адреса 3 |

|

35 |

Разряд адреса 4 |

119 |

Разряд адреса 5 |

|

36 |

Разряд адреса 6 |

120 |

Разряд адреса 7 |

|

37 |

Разряд адреса 8 |

121 |

Разряд адреса 9 |

|

38 |

Разряд адреса 10 |

122 |

Bank Address 0 |

|

39 |

Bank Address 1 |

123 |

Разряд адреса 11 |

|

40 |

+3,3 В |

124 |

+3,3 В |

|

41 |

+3,3 В |

125 |

Clock 1 |

|

42 |

Clock 0 |

126 |

Разряд адреса 12 |

|

43 |

Общий |

127 |

Общий |

|

44 |

Зарезервирован |

128 |

Clock Enable 0 |

|

45 |

S2 |

129 |

S3 |

|

46 |

Byte Mask 2 |

130 |

Byte Mask 6 |

|

47 |

Byte Mask 3 |

131 |

Byte Mask 7 |

|

48 |

Зарезервирован |

132 |

Разряд адреса 13 |

|

49 |

+3,3 В |

133 |

+3,3 В |

|

50 |

Не соединен |

134 |

He соединен |

|

51 |

Не соединен |

135 |

He соединен |

|

52 |

Не соединен |

136 |

He соединен |

|

53 |

Не соединен |

137 |

He соединен |

|

54 |

Общий |

138 |

Общий |

|

55 |

Бит данных 16 |

139 |

Бит данных 48 |

|

56 |

Бит данных 1 7 |

140 |

Бит данных 49 |

|

57 |

Бит данных 18 |

141 |

Бит данных 50 |

|

58 |

Бит данных 19 |

142 |

Бит данных 51 |

|

59 |

+3,3 В |

143 |

+3,3 В |

|

60 |

Бит данных 20 |

144 |

Бит данных 52 |

|

61 |

Не соединен |

145 |

Не соединен |

|

62 |

Voltage Reference |

146 |

Voltage Reference |

|

63 |

Clock Enable 1 |

147 |

Не соединен |

|

Контакт |

Обозначение |

Контакт |

Обозначение |

|

64 |

Общий |

148 |

Общий |

|

65 |

Бит данных 21 |

149 |

Бит данных 53 |

|

66 |

Бит данных 22 |

150 |

Бит данных 54 |

|

67 |

Бит данных 23 |

151 |

Бит данных 55 |

|

68 |

Общий |

152 |

Общий |

|

69 |

Бит данных 24 |

153 |

Бит данных 56 |

|

70 |

Бит данных 25 |

154 |

Бит данных 57 |

|

71 |

Бит данных 26 |

155 |

Бит данных 58 |

|

72 |

Бит данных 27 |

156 |

Бит данных 59 |

|

73 |

+3,3 В |

157 |

+3,3 В |

|

74 |

Бит данных 28 |

158 |

Бит данных 60 |

|

75 |

Бит данных 29 |

159 |

Бит данных 61 |

|

76 |

Бит данных 30 |

160 |

Бит данных 62 |

|

77 |

Бит данных 31 |

161 |

Бит данных 63 |

|

78 |

Общий |

162 |

Общий |

|

79 |

Clock 2 |

163 |

Clock 3 |

|

80 |

Не соединен |

164 |

Не соединен |

|

81 |

Не соединен |

165 |

Serial PD Address 0 |

|

82 |

Serial Data I/O |

166 |

Serial PD Address 1 |

|

83 |

Serial Clock Input |

167 |

Serial PD Address 2 |

|

84 |

+3,3 В |

168 |

+3,3 В |

|

|

|

|

|

|

Так называли тип памяти SDRAM (Synchronous DRAM). Начиная с 1996 года большинство чипсетов Intel стали поддерживать этот вид модулей памяти, сделав его очень популярным вплоть до 2001 года. Большинство компьютеров с процессорами Pentium и Celeron использовали именно этот вид памяти. Дальше пошла эра DDR, и память почти перестали называть симы или димы. Теперь в ходу название DDR (DDR2, DDR3) модуль или планка.

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

DDR (Double Data Rate) стал развитием SDRAM. Этот вид модулей памяти впервые появился на рынке в 2001 году. Основное отличие между DDR и SDRAM заключается в том, что вместо удвоения тактовой частоты для ускорения работы, эти модули передают данные дважды за один такт.

Pin # |

Description |

Pin # |

Description |

1 |

VREF |

121 |

VSS |

2 |

VSS |

122 |

DQ4 |

3 |

DQ0 |

123 |

DQ5 |

4 |

DQ1 |

124 |

VSS |

5 |

VSS |

125 |

DM0 |

6 |

/DQS0 |

126 |

NC |

7 |

DQS0 |

127 |

VSS |

8 |

VSS |

128 |

DQ6 |

9 |

DQ2 |

129 |

DQ7 |

10 |

DQ3 |

130 |

VSS |

11 |

VSS |

131 |

DQ12 |

12 |

DQ8 |

132 |

DQ13 |

13 |

DQ9 |

133 |

VSS |

14 |

VSS |

134 |

DM1 |

15 |

/DQS1 |

135 |

NC |

16 |

DQS1 |

136 |

VSS |

17 |

VSS |

137 |

CK1 |

18 |

NC |

138 |

/CK1 |

19 |

NC |

139 |

VSS |

20 |

VSS |

140 |

DQ14 |

21 |

DQ10 |

141 |

DQ15 |

22 |

DQ11 |

142 |

VSS |

23 |

VSS |

143 |

DQ20 |

24 |

DQ16 |

144 |

DQ21 |

25 |

DQ17 |

145 |

VSS |

26 |

VSS |

146 |

DM2 |

27 |

/DQS2 |

147 |

NC |

28 |

DQS2 |

148 |

VSS |

29 |

VSS |

149 |

DQ22 |

30 |

DQ18 |

150 |

DQ23 |

31 |

DQ19 |

151 |

VSS |

32 |

VSS |

152 |

DQ28 |

33 |

DQ24 |

153 |

DQ29 |

34 |

DQ25 |

154 |

VSS |

35 |

VSS |

155 |

DM3 |

36 |

/DQS3 |

156 |

NC |

37 |

DQS3 |

157 |

VSS |

38 |

VSS |

158 |

DQ30 |

39 |

DQ26 |

159 |

DQ31 |

40 |

DQ27 |

160 |

VSS |

41 |

VSS |

161 |

NC |

42 |

NC |

162 |

NC |

43 |

NC |

163 |

VSS |

44 |

VSS |

164 |

NC |

45 |

NC |

165 |

NC |

46 |

NC |

166 |

VSS |

47 |

VSS |

167 |

NC |

48 |

NC |

168 |

NC |

49 |

NC |

169 |

VSS |

50 |

VSS |

170 |

VDDQ |

51 |

VDDQ |

171 |

CKE1 |

52 |

CKE0 |

172 |

VDD |

53 |

VDD |

173 |

NC |

54 |

NC |

174 |

NC |

55 |

NC |

175 |

VDDQ |

56 |

VDDQ |

176 |

A12 |

57 |

A11 |

177 |

A9 |

58 |

A7 |

178 |

VDD |

59 |

VDD |

179 |

A8 |

60 |

A5 |

180 |

A6 |

61 |

A4 |

181 |

VDDQ |

62 |

VDDQ |

182 |

A3 |

63 |

A2 |

183 |

A1 |

64 |

VDD |

184 |

VDD |

KEY |

|||

65 |

VSS |

185 |

CK0 |

66 |

VSS |

186 |

/CK0 |

67 |

VDD |

187 |

VDD |

68 |

NC |

188 |

A0 |

69 |

VDD |

189 |

VDD |

70 |

A10/AP |

190 |

BA1 |

71 |

BA0 |

191 |

VDDQ |

72 |

VDDQ |

192 |

/RAS |

73 |

/WE |

193 |

/CS0 |

74 |

/CAS |

194 |

VDDQ |

75 |

VDDQ |

195 |

ODT0 |

76 |

/CS1 |

196 |

A13 |

77 |

ODT1 |

197 |

VDD |

78 |

VDDQ |

198 |

VSS |

79 |

VSS |

199 |

DQ36 |

80 |

DQ32 |

200 |

DQ37 |

81 |

DQ33 |

201 |

VSS |

82 |

VSS |

202 |

DM4 |

83 |

/DQS4 |

203 |

NC |

84 |

DQS4 |

204 |

VSS |

85 |

VSS |

205 |

DQ38 |

86 |

DQ34 |

206 |

DQ39 |

87 |

DQ35 |

207 |

VSS |

88 |

VSS |

208 |

DQ44 |

89 |

DQ40 |

209 |

DQ45 |

90 |

DQ41 |

210 |

VSS |

91 |

VSS |

211 |

DM5 |

92 |

/DQS5 |

212 |

NC |

93 |

DQS5 |

213 |

VSS |

94 |

VSS |

214 |

DQ46 |

95 |

DQ42 |

215 |

DQ47 |

96 |

DQ43 |

216 |

VSS |

97 |

VSS |

217 |

DQ52 |

98 |

DQ48 |

218 |

DQ53 |

99 |

DQ49 |

219 |

VSS |

100 |

VSS |

220 |

CK2 |

101 |

SA2 |

221 |

/CK2 |

102 |

NC |

222 |

VSS |

103 |

VSS |

223 |

DM6 |

104 |

/DQS6 |

224 |

NC |

105 |

DQS6 |

225 |

VSS |

106 |

VSS |

226 |

DQ54 |

107 |

DQ50 |

227 |

DQ55 |

108 |

DQ51 |

228 |

VSS |

109 |

VSS |

229 |

DQ60 |

110 |

DQ56 |

230 |

DQ61 |

111 |

DQ57 |

231 |

VSS |

112 |

VSS |

232 |

DM7 |

113 |

/DQS7 |

233 |

NC |

114 |

DQS7 |

234 |

VSS |

115 |

VSS |

235 |

DQ62 |

116 |

DQ58 |

236 |

DQ63 |

117 |

DQ59 |

237 |

VSS |

118 |

VSS |

238 |

VDDSPD |

119 |

SDA |

239 |

SA0 |

120 |

SCL |

240 |

SA1 |

DDR2 (Double Data Rate 2) – более новый вариант DDR, который теоретически должен быть в два раза более быстрым. Впервые память DDR2 появилась в 2003 году, а чипсеты, поддерживающие ее – в середине 2004. Основное отличие DDR2 от DDR – способность работать на значительно большей тактовой частоте, благодаря усовершенствованиям в конструкции. По внешнему виду отличается от DDR числом контактов: оно увеличилось со 184 (у DDR) до 240 (у DDR2).

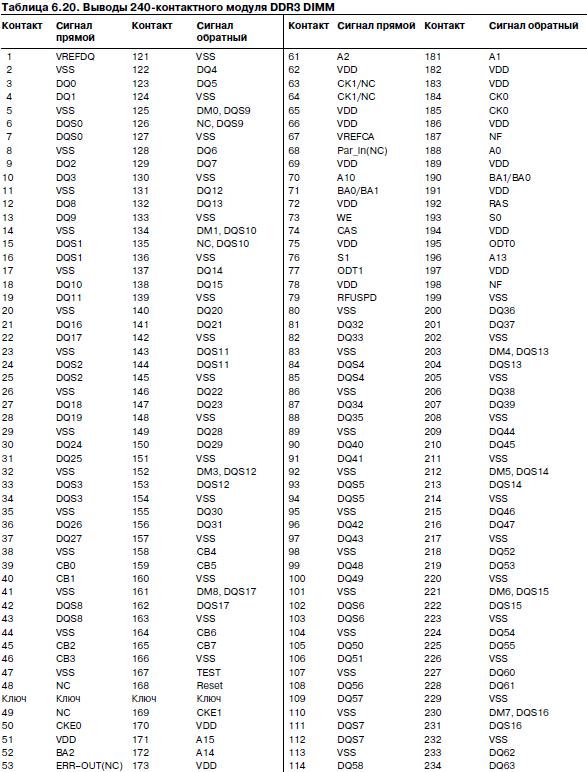

Как и модули памяти DDR2, они выпускаются в виде 240-контактной печатной платы (по 120 контактов с каждой стороны модуля), однако не являются электрически совместимыми с последними, и по этой причине имеют иное расположение «ключа».