- •Бийский технологический институт (филиал)

- •Цифровые измерительные устройства Учебно-методическое пособие

- •Содержание

- •1 Задание на курсовое проектирование

- •2 Типовые блоки цифровых приборов

- •2.1 Микропроцессорный блок на базе микропроцессора кр580вм80

- •2.2 Микропроцессорный блок на базе микроконтроллера at89c51

- •2.3 Блок памяти

- •2.3.1 Основные параметры запоминающих устройств

- •2.3.2 Классификация запоминающих устройств

- •2.4 Блок индикации

- •2.4.1 Индикация на светодиодах

- •2.4.2 Индикация на семисегментных индикаторах

- •2.4.3 Индикация на матричных светодиодных индикаторах

- •2.4.4 Индикация на жидкокристаллических дисплеях

- •2.5 Блок ввода информации

- •2.6 Блок связи прибора с пк

- •2.6.1 Связь по параллельному интерфейсу

- •2.6.2 Связь по последовательному интерфейсу

- •2.7 Блок преобразования сигналов

- •2.7.1 Преобразование амплитуды сигнала

- •2.7.2 Аналогово-цифровое и цифро-аналоговое преобразование

- •2.8 Блок автоматического выбора предела измерений

- •2.9 Аналоговая часть измерительного прибора

- •2.9.1 Аналоговые компараторы

- •2.9.2 Дифференцирующие цепи

- •2.9.3 Интегрирующие цепи

- •3 Некоторые типовые ситуации при построении узлов и блоков циу

- •3.1 Подключение памяти и внешних устройств к микропроцессору (микроконтроллеру). Распределение адресного пространства микроконтроллера.

- •3.2 Типы выходных каскадов логических элементов

- •3.3 Режимы неиспользуемых входов

- •3.4 Выбор серии микросхем

- •4 Методы построения цифровых измерительных приборов

- •4.1 Метод дискретного счета (время-импульсный метод)

- •4.1.1 Измерение временных интервалов

- •4.1.2 Измерение сдвига фаз

- •4.1.3 Измерение напряжения

- •4.1.4 Измерение параметров электрических цепей

- •4.2 Частотно-импульсный метод

- •4.2.1 Измерение напряжения

- •4.3 Кодово-импульсный метод

- •4.4 Метод двойного интегрирования

- •4.5 Метод электронно-счетного частотомера

- •5 Основные требования, предъявляемые к выполнению курсового проекта

- •5.1 Требования к текстовой части курсового проекта

- •5.1.1 Структура и содержание пояснительной записки

- •5.1.2 Правила оформления пояснительной записки

- •5.2 Требования к оформлению графической части курсового проекта

- •5.2.1 Позиционное обозначение элементов в схемах

- •5.2.2 Обозначение цепей в электрических схемах

- •5.2.3 Примеры условно-графических обозначений в схемах

- •5.2.3.1 Условно-графические обозначения элементов цифровой техники

- •5.2.3.2 Условно-графические обозначения элементов аналоговой техники

- •5.2.3.3 Условно-графические обозначения интегральных оптоэлектронных элементов индикации

- •5.2.3.4 Условно-графические обозначения резисторов

- •5.2.3.5 Условно-графические обозначения конденсаторов

- •5.2.3.6 Условно-графические обозначения катушек индуктивности, дросселей и трансформаторов

- •5.2.3.7 Условно-графические обозначения полупроводниковых приборов

- •5.2.3.8 Условно-графические обозначения коммутационных устройств и контактных соединений

- •5.2.3.9 Условно-графические обозначения электрических связей, проводов, кабелей

- •5.2.3.10 Условно-графическое обозначение заземления

- •6. Варианты заданий

- •7. Список использованных источников

5.2.3.1 Условно-графические обозначения элементов цифровой техники

Элемент схемы – изделия или части изделия, реализующие функцию или системы функций алгебры логики, например, микросхема интегральная, микросборка, набор элементов, их части и совокупности. К элементам цифровой техники условно относят элементы, не выполняющие функции алгебры логики, но применяемые в логических цепях, например, генератор, усилитель, конденсатор и т.д.

УГО элемента имеет форму прямоугольника, к которому подводят линии выводов. УГО элемента может содержать три поля: основное и два дополнительных. Дополнительные поля располагают слева и справа от основного поля. Допускается дополнительные поля разделять на зоны, которые отделяют горизонтальной чертой.

В первой строке основного поля УГО помещают обозначение функции, выполняемой элементом. В дополнительных полях помещают информацию о функциональных назначениях выводов (указатели, метки) (рисунок 5.7).

|

Рисунок 5.6 – Заполнение основных и дополнительных полей |

Выводы элементов делят на входы, выходы, двунаправленные выводы и выводы, не несущие логической информации. Входы элемента изображают с левой стороны УГО, выходы – с правой стороны. Двунаправленные выводы и выводы, не несущие логической информации, помещают с правой или левой стороны прямоугольника. Допускается другая ориентация УГО, при которой входы располагают сверху, выходы снизу.

Размеры УГО определяются:

по высоте:

количеством линий выводов;

количеством интервалов;

количеством строк информации в основном и дополнительных полях;

размером шрифта;

по ширине:

наличием дополнительных полей;

количеством знаков, помещаемых в одной строке внутри УГО (с учетом пробелов);

размером шрифта.

Расстояние между линиями выводов должно быть не менее и кратным величине C. Расстояние между горизонтальной стороной УГО, границей зоны и линией вывода должно быть не менее и кратным величине C/2. Размеры УГО по высоте должны быть кратными постоянной величине C/2. При разделении групп линий выводов интервалом величина его должна быть не менее 2C и кратной величине C.

В зависимости от способа выполнения схемы C должно быть не менее: 5 мм – при выполнении вручную; интервала между строками – при выполнении автоматизированным способом.

Ширина дополнительного поля должна быть не менее: 5 мм – при выполнении вручную; ширины одного символа печатающего устройства – при выполнении автоматизированным способом. При увеличении количества символов в строке ширина дополнительного поля должна быть соответственно увеличена. При выполнении схем автоматизированным способом применяют шрифты, имеющиеся в печатающих устройствах, и надписи выполняют прописными буквами.

Обозначения УГО должны соответствовать приведенным на рисунке 5.8.

|

а – основное поле; б – основное поле с дополнительными полями, количество зон не ограничено; в – входы элемента; г – выходы элемента; д – изображение группы элементов (совмещено); е – изображение группы элементов (не совмещено) Рисунок 5.7 – Примеры УГО цифровых элементов |

Обозначения основных функций элементов цифровых элементов приведены в таблице 5.3.

Таблица 5.3 – Обозначения основных функций элементов цифровой техники

Наименование основной функции |

Обозначение |

Наименование производной функции |

Обозначение |

Вычислитель |

CP |

Секция вычислителя |

CPS |

Вычислительное устройство (центральный процессор) |

CPU |

||

Процессор |

P |

Секция процессора |

PS |

Память |

M |

Устройство запоминающее |

|

оперативное с произвольным доступом |

RAM |

||

оперативное с последовательным доступом |

SAM |

||

запоминающее |

STM |

||

ассоциативное |

CAM |

||

Матрица логическая программируемая |

PLM |

||

Устройство запоминающее постоянное с возможностью программирования |

ROM |

||

однократного |

PROM |

||

многократного |

RPROM |

||

Управление |

CO |

|

|

Перенос |

CR |

|

|

Прерывание |

INR |

|

|

Передача |

TF |

|

|

Прием |

RC |

|

|

Ввод-вывод |

IO |

Ввод-вывод |

|

последовательный |

IOS |

||

параллельный |

IOP |

||

Арифметика |

A |

Суммирование |

SM или Σ |

Умножение |

MPL |

||

Деление |

DIV |

||

Вычитание |

SUB |

||

Умножение по основанию n (здесь и далее n – целое натуральное число, большее или равное 1) |

MPLn |

||

Деление по основанию n |

DIVn |

||

Логика |

L |

Логический порог: |

≥n или >=n |

мажоритарность (n из m) |

≥n |

||

логическое ИЛИ (1 из m) |

≥1 |

||

логическое И (m из m) |

& или И |

||

повторитель (m=1), где m – число входов логического элемента n и только n |

1

=n |

||

n=1 – исключающее ИЛИ |

=1 |

||

Элемент монтажной логики |

|

Монтажное ИЛИ Монтажное И |

1 или 1 & или & |

Регистр |

RG |

Регистр со сдвигом: |

|

слева направо или сверху вниз |

RG← или RG< |

||

справо налево или снизу вверх |

RG→ или RG |

||

с реверсивным |

RG←← или RG<> |

||

Счетчик |

CT |

Счетчик: |

|

по основанию n |

CTn |

||

двоичный |

CT2 |

||

десятичный |

CT10 |

||

Дешифратор |

DC |

|

|

Шифратор |

CD |

|

|

Преобразователь (буквы X, Y можно заменять обозначениями информации на входах и выходах) |

X/Y |

Вместо X, Y можно использовать следующие значения: |

|

двоичной код |

B |

||

десятичный код |

DC |

||

код Грея |

G |

||

аналоговая |

∩ или ^ или A |

||

цифровая |

D |

||

напряжение |

U |

||

ток |

I |

||

n-сегментный |

nS |

||

Сравнение |

= = |

– |

|

Свертка по модулю n |

Mn |

Свертка по модулю 2 |

M2 |

Мультиплексор |

MUX |

– |

|

Демультиплексор |

DMX |

– |

|

Мультиплексор-селектор |

MS |

– |

|

Селектор |

SL |

– |

|

Генератор |

G |

Генератор |

|

серии прямоугольных импульсов |

Gn |

||

с непрерывной последовательностью импульсов |

GN |

||

одиночного импульса (одновибратор) |

|

||

линейно изменяющихся сигналов |

Gj |

||

синусоидального сигнала |

GSIN |

||

Пороговых элемент (триггер Шмитта) |

|

– |

|

Дискриминатор |

|

– |

|

Триггер |

T |

Триггер двухступенчатый |

TT |

Задержка |

|

|

|

Формирователь |

F |

Формирователь уровня логического состояния n |

FLn |

логического нуля |

FL0 |

||

логической единицы |

FL1 |

||

Усилитель |

|

Усилитель с повышенной нагрузочной способностью |

|

Ключ |

SW |

– |

|

Модулятор |

MD |

– |

|

Демодулятор |

DM |

– |

|

Нелогический элемент |

* |

Стабилизатор |

*ST |

Стабилизатор |

|

||

напряжения |

*STU |

||

тока |

*STI |

||

Наборы нелогических элементов |

|

||

резисторов |

*R |

||

конденсаторов |

*C |

||

индуктивностей |

*L |

||

диодов |

*D |

||

диодов с указанием полярности |

*D→ или *D> *D← или *D< |

||

транзисторов |

*T |

||

трансформаторов |

*TR |

||

индикаторов |

*H |

||

предохранителей |

*FU |

||

комбинированных |

*DR |

Вывод элемента должен иметь условное обозначение, которое выполняется в виде указателей и меток. Размер указателя должен быть не более 3 мм (при выполнении вручную). Указатели проставляются на линии контура УГО или на линии связи около линии контура УГО со стороны линии вывода (таблица 5.4).

Таблица 5.4 – Обозначение указателя выводов

Наименование |

Обозначение |

Прямой вывод |

|

Инверсный вывод |

|

Вывод не несущей логической информации |

|

Группы выводов элементов подразделяются на логические равнозначные, т.е. взаимозаменяемые без изменения функции элемента и логически неравнозначные. Логически равнозначные выводы разрешается объединять в группу и присваивать ей метку, обозначающую взаимосвязь между выводами внутри группы и (или) функциональное назначение всей группы.

Для обозначения двунаправленного вывода применяют метку “↔” или “<>”.

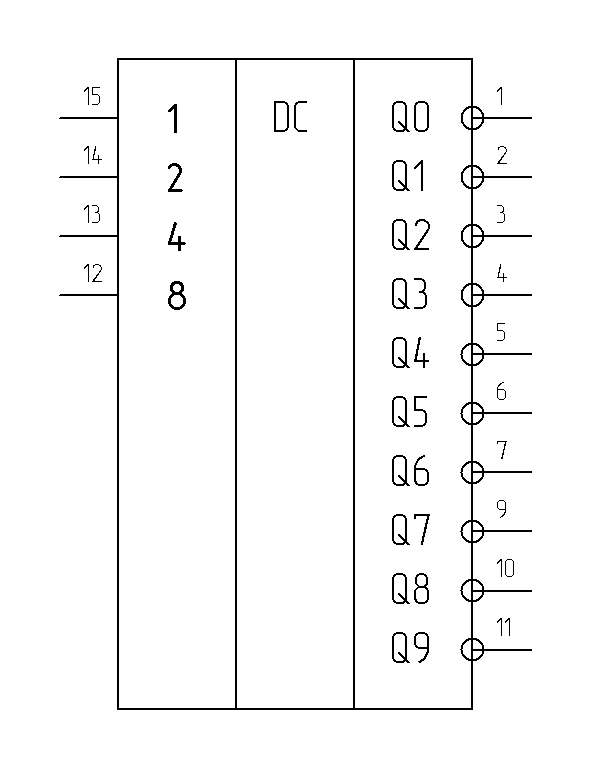

На рисунке 5.8 приведено условно-графическое обозначение микросхемы К555ИД10.

|

Рисунок 5.8 – Условно-графическое обозначение микросхемы К555ИД10 |

или

или

или

G1

или

G1 или TH

или TH или

DIC

или

DIC или

DL

или

DL или >

или >