- •Бийский технологический институт (филиал)

- •Цифровые измерительные устройства Учебно-методическое пособие

- •Содержание

- •1 Задание на курсовое проектирование

- •2 Типовые блоки цифровых приборов

- •2.1 Микропроцессорный блок на базе микропроцессора кр580вм80

- •2.2 Микропроцессорный блок на базе микроконтроллера at89c51

- •2.3 Блок памяти

- •2.3.1 Основные параметры запоминающих устройств

- •2.3.2 Классификация запоминающих устройств

- •2.4 Блок индикации

- •2.4.1 Индикация на светодиодах

- •2.4.2 Индикация на семисегментных индикаторах

- •2.4.3 Индикация на матричных светодиодных индикаторах

- •2.4.4 Индикация на жидкокристаллических дисплеях

- •2.5 Блок ввода информации

- •2.6 Блок связи прибора с пк

- •2.6.1 Связь по параллельному интерфейсу

- •2.6.2 Связь по последовательному интерфейсу

- •2.7 Блок преобразования сигналов

- •2.7.1 Преобразование амплитуды сигнала

- •2.7.2 Аналогово-цифровое и цифро-аналоговое преобразование

- •2.8 Блок автоматического выбора предела измерений

- •2.9 Аналоговая часть измерительного прибора

- •2.9.1 Аналоговые компараторы

- •2.9.2 Дифференцирующие цепи

- •2.9.3 Интегрирующие цепи

- •3 Некоторые типовые ситуации при построении узлов и блоков циу

- •3.1 Подключение памяти и внешних устройств к микропроцессору (микроконтроллеру). Распределение адресного пространства микроконтроллера.

- •3.2 Типы выходных каскадов логических элементов

- •3.3 Режимы неиспользуемых входов

- •3.4 Выбор серии микросхем

- •4 Методы построения цифровых измерительных приборов

- •4.1 Метод дискретного счета (время-импульсный метод)

- •4.1.1 Измерение временных интервалов

- •4.1.2 Измерение сдвига фаз

- •4.1.3 Измерение напряжения

- •4.1.4 Измерение параметров электрических цепей

- •4.2 Частотно-импульсный метод

- •4.2.1 Измерение напряжения

- •4.3 Кодово-импульсный метод

- •4.4 Метод двойного интегрирования

- •4.5 Метод электронно-счетного частотомера

- •5 Основные требования, предъявляемые к выполнению курсового проекта

- •5.1 Требования к текстовой части курсового проекта

- •5.1.1 Структура и содержание пояснительной записки

- •5.1.2 Правила оформления пояснительной записки

- •5.2 Требования к оформлению графической части курсового проекта

- •5.2.1 Позиционное обозначение элементов в схемах

- •5.2.2 Обозначение цепей в электрических схемах

- •5.2.3 Примеры условно-графических обозначений в схемах

- •5.2.3.1 Условно-графические обозначения элементов цифровой техники

- •5.2.3.2 Условно-графические обозначения элементов аналоговой техники

- •5.2.3.3 Условно-графические обозначения интегральных оптоэлектронных элементов индикации

- •5.2.3.4 Условно-графические обозначения резисторов

- •5.2.3.5 Условно-графические обозначения конденсаторов

- •5.2.3.6 Условно-графические обозначения катушек индуктивности, дросселей и трансформаторов

- •5.2.3.7 Условно-графические обозначения полупроводниковых приборов

- •5.2.3.8 Условно-графические обозначения коммутационных устройств и контактных соединений

- •5.2.3.9 Условно-графические обозначения электрических связей, проводов, кабелей

- •5.2.3.10 Условно-графическое обозначение заземления

- •6. Варианты заданий

- •7. Список использованных источников

3.2 Типы выходных каскадов логических элементов

Цифровые элементы могут иметь выходы следующих типов: логические, с открытым коллектором, с третьи состоянием, с открытым эмиттером. Наличие четырех типов входов объясняется различными условиями работы элементов в логических цепях, в магистрально-модульных микропроцессорных системах.

Логический выход формирует два уровня выходного напряжения (U0 и U1). Выходное сопротивление логического выхода стремятся сделать малым, способным развивать большие токи для перезаряда емкостных нагрузок и, следовательно, для получения высокого быстродействия элемента. Такой тип выхода имеют большинство логических элементов, используемых в комбинационных цепях.

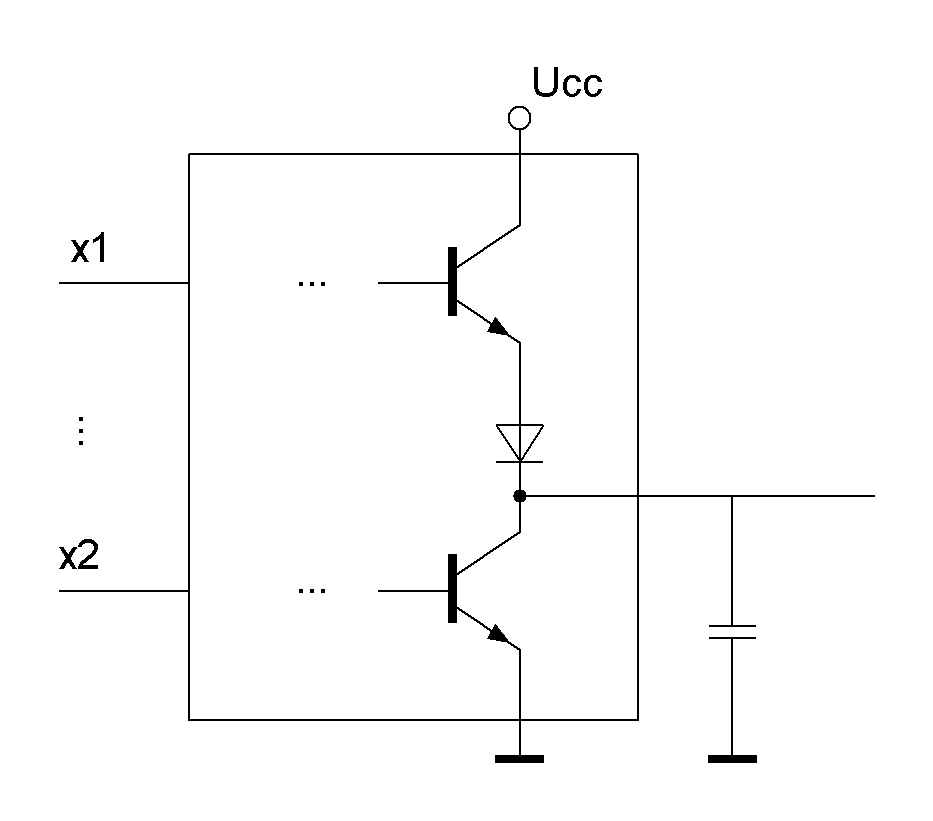

Схемы логических элементов ТТЛ(Ш) и КМОП подобны двухтактным каскадам – в них оба фронта выходного напряжения формируются с участим активных транзисторов, работающих противофазно, что обеспечивает малые выходные сопротивления при любом направлении переключения выхода (рисунок 3.4).

|

Рисунок 3.4 – Схема выходной цепи цифрового элемента |

Особенностью таких выходов состоит в том, что их нельзя соединять параллельно. Во-первых, это создаст логическую неопределенность, т. к. в точке соединения выхода, формирующего логическую единицу, и выхода, формирующего логический нуль, не будет нормального результата. Во-вторых, при соединении выходов, находящихся в различных логических состояниях, возникло бы их «противоборство». Вследствие малых величин выходных сопротивлений уравнительных ток при этом может достигать достаточно большой величины, что может вывести из строя электрические элементы выходной цепи.

Элементы с тремя состояниями выхода (типа TC) кроме логических состояний 0 и 1 имеют состояние «отключено», в котором ток выходной цепи пренебрежимо мал. В это состояние (третье) элемент переводиться специальным управляющим сигналом, обеспечивающим запретное состояние обоим транзисторам выходного каскада. Сигнал управления элементом, типа TC обычно обозначается как OE (Output Enable). При наличии разрешения (OE=1) элемент работает как обычно, выполняя свою логическую операцию, а при его отсутствии (OE=0) переходит в состояние «отключено»

Выходы типа TC можно соединять параллельно при условии, что в любой момент времени активным может быть только один из них. В этом случае отключенные выходы не мешают активному формировать сигналы в точке соединения выходов.

Элементы с открытым коллектором имеют выходную цепь, заканчивающуюся одиночным транзистором, коллектор которого не соединен с какими-либо цепями внутри микросхемы (рисунок 3.5).

|

Рисунок 3.5 – Схема выходной цепи цифрового элемента с открытым коллектором |

Несколько выходов типа открытый коллектор можно соединять параллельно, подключая их к общей для всех выходов цепочке Ucc-R (рисунок 6). При этом можно получить режим поочередной работы на общую линию, как и для элементов типа TC, если активным будет лишь один элемент, а выходы всех остальных окажутся запертыми.

|

Рисунок 3.6 – Реализация монтажной логики выходной цепи цифрового элемента с открытым коллектором |

При работе с элементами типа открытый коллектор проектировщик должен задать сопротивление резистора R, которое не является стандартным, а определяется для конкретных условий. Анализ статических режимов задает ограничения величины сопротивления R снизу и сверху. Значение сопротивления резистора R выбирается в этом диапазоне с учетом быстродействия схемы и потребляемой ею мощностью. Пример расчета сопротивления R приведен в литературе [!!].

Выход с открытым эмиттером характерен для элементов эмиттерно-связанной логики. Для работы на магистраль такие элементы не используются.