- •Бийский технологический институт (филиал)

- •Цифровые измерительные устройства

- •Содержание

- •Различия между аналоговыми и цифровыми средствами измерений

- •Цифровые средства измерения напряжения

- •Измерение постоянного напряжения

- •Метод пространственного кодирования

- •Метод с промежуточным преобразованием напряжения во временной интервал (время-импульсный методы)

- •Метод двойного интегрирования

- •Метод с промежуточным преобразованием напряжения в частоту

- •Метод с промежуточным преобразованием напряжения в фазу

- •Кодово-импульсный метод (метод поразрядного кодирования)

- •Комбинированный метод преобразования

- •Автоматизация измерений

- •Автоматизация выбора предела (авп) измерений

- •Автоматическая коррекция погрешностей

- •Измерение переменного напряжения

- •Измерение частоты электромагнитных колебаний

- •Методы определения действительного значения частоты электромагнитных колебаний

- •Измерение параметров линейных элементов электрических цепей

- •Метод электронного счета

- •Цифровая обработка сигналов (dsp)

- •Типовые области применения dsp процессоров

- •Семейство 561хх. Основные характеристики

- •24 Разрядные dsp фирмы motorola

- •Обзор архитектуры и шинной организации dsp 560xx

- •Общая характеристика

- •Арифметико-логическое устройство данных

- •X0, x1, y0, y1 - буферные регистры; ак. Лу – аккумулятор логического устройства; ус – устройство сдвига; а, в – аккумуляторы процессора; шдх - шина данных х; усо – устройство сдвига-ограничения

- •Устройство генерации адресов (agu) и режимы адресации.

- •Блок регистров адреса r0-r7

- •Блок регистров смещения n0-n7

- •Блок регистров модификации м0-м7

- •Алу адресов

- •Линейный модификатор

- •Модульный модификатор

- •Модификатор реверсивного переноса

- •Программный контроллер

- •Структура программного контроллера

- •Регистр операционного режима (omr)

- •Таймер dsp56002

- •Программная модель таймерного модуля

- •Регистр таймера/счётчика tcr

- •Регистр статуса/управления tcsr

- •Литература

Структура программного контроллера

Программный контроллер состоит из трех аппаратных блоков:

- контроллера декодирования программ (PDC);

- генератора адресов программ (PAG);

- контроллера прерываний (PIC).

Контроллер декодирования программ включает в себя программную логику для декодирования команд, генератор адреса регистра, механизм выполнения циклов, механизм выполнения повторений, генератор кодов условий, механизм выполнения прерываний, регистр-защелку инструкций и его копию.

Генератор адресов программ содержит все регистры программного контроллера и системный стек. Циклы, являющиеся основной конструкцией алгоритмов цифровой обработки сигналов, поддерживаются аппаратно. С точки зрения программиста достаточно указать количество повторений цикла и его границы. После чего выполнить соответствующую команду начала цикла. На аппаратном уровне в регистр LC загружается количество повторений цикла, в регистр LA адрес последней команды цикла, а в регистре статуса автоматически устанавливается флаг инициализации цикла. После этого цикл автоматически повторяется LC раз. Механизм повторений позволяет ускорить процессы пересылки большого объема информации путем автоматического, аппаратного повторения LC раз одной и той же команды. При этом экономится время на считывание и декодирование команды. Из-за особенностей механизма повторений в процессе его реализации отключается механизм прерываний.

Контроллер прерываний принимает все запросы прерываний, осуществляет арбитраж в каждом цикле и генерирует адрес вектора прерывания. Прерывания могут вызывать четыре внешних и шестнадцать внутренних источников прерываний.

Используется структура гибкого приоритета прерываний. Каждое прерывание получает свой уровень приоритета (IPL), от 0 до 3. Уровни 1 и 2 могут маскироваться. При арбитраже к исполнению выбирается прерывание с максимальным уровнем приоритета. В таблице 5.1 указаны источники прерываний и их уровни приоритета.

Таблица 5.1 - Источники прерываний и их уровни приоритета

Стартовый адрес |

IPL |

Источник |

P:$0000/P:$E000 |

3 |

Аппаратный внешний сброс |

P:$0002 |

3 |

Ошибка стека |

P:$0004 |

3 |

Трассировка |

P:$0006 |

3 |

Программное прерывание SWI |

P:$0008 |

0-2 |

Внешнее прерывание IRQA |

P:$000A |

0-2 |

Внешнее прерывание IRQB |

P:$000C |

0-2 |

Приемник данных SSI |

P:$000E |

0-2 |

Приемник данных в состоянии исключения SSI |

P:$0010 |

0-2 |

Передатчик данных SSI |

P:$0012 |

0-2 |

Передатчик данных в состоянии исключения SSI |

P:$0014

|

0-2 |

Приемник данных SCI |

P:$0016 |

0-2 |

Приемник данных в состоянии исключения SCI |

P:$0018 |

0-2 |

Передатчик данных SCI |

P:$001A |

0-2 |

Простой линии SCI |

P:$001C |

0-2 |

Таймер SCI |

P:$001E |

3 |

NMI, зарезервировано для разработок |

P:$0020 |

0-2 |

Приемник данных Host |

P:$0022 |

0-2 |

Передатчик данных Host |

P:$0024 |

0-2 |

Команда Host |

P:$0026 |

0-2 |

Доступно для команд Host |

P:$0028 |

0-2 |

Доступно для команд Host |

P:$002A |

0-2 |

Доступно для команд Host |

P:$002C |

0-2 |

Доступно для команд Host |

P:$002E |

0-2 |

Доступно для команд Host |

P:$0030 |

0-2 |

Доступно для команд Host |

P:$0032 |

0-2 |

Доступно для команд Host |

P:$0034 |

0-2 |

Доступно для команд Host |

P:$0036 |

0-2 |

Доступно для команд Host |

P:$0038 |

0-2 |

Доступно для команд Host |

P:$003A |

0-2 |

Доступно для команд Host |

P:$003C |

0-2 |

Доступно для команд Host |

P:$003E |

0-2 |

Неправильная инструкция |

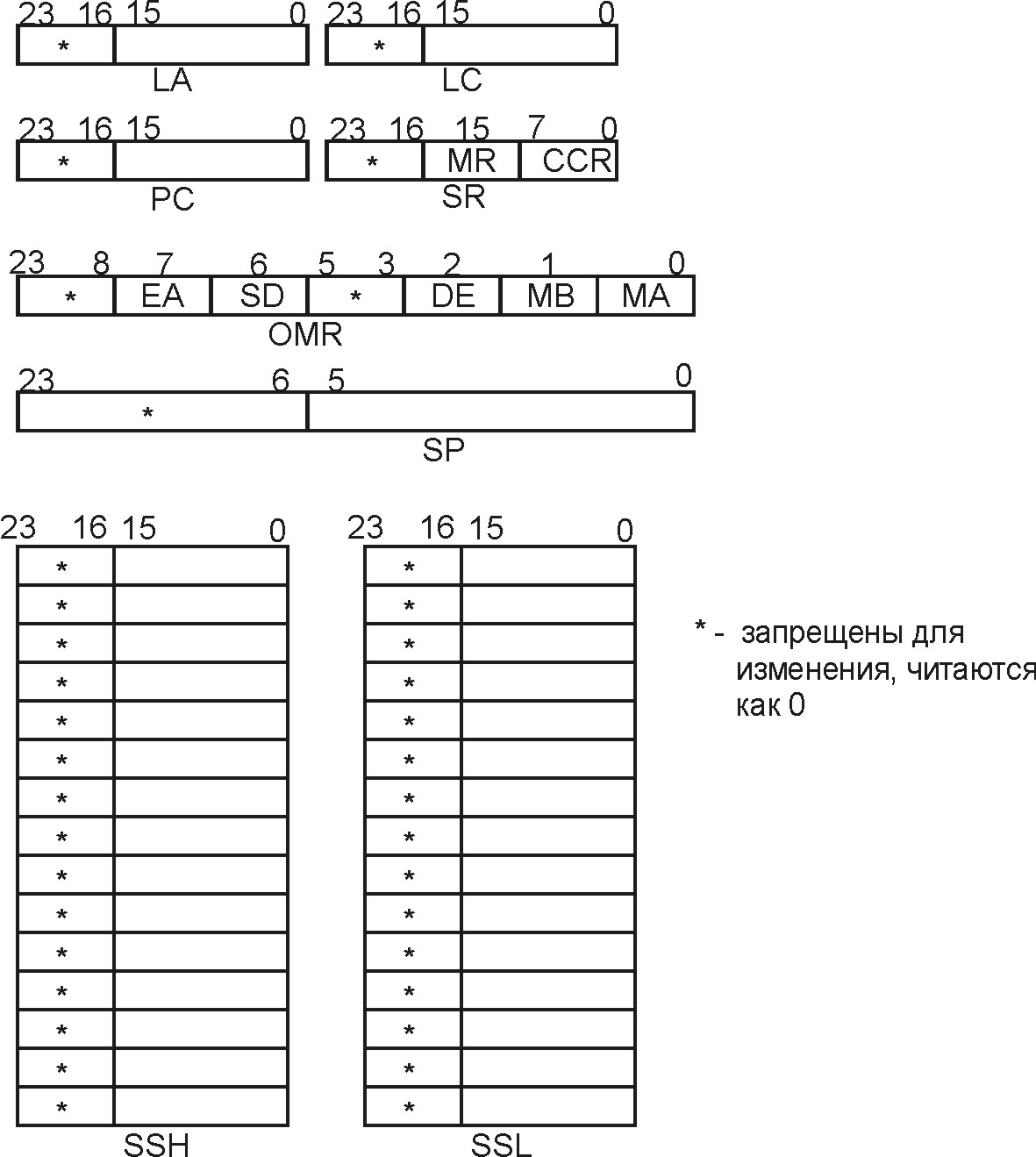

При наступлении прерывания процессор делает переход по указанному адресу для каждого прерывания. Если по этому адресу стоит однословная команда, то она выполняется, и прерывание автоматически завершается. Если команда двухсловная, то процессор входит в режим длинного прерывания и в этом случае в стек дополнительно к адресу возврата сохраняется регистр статуса. Программная модель программного контроллера показана на рисунке 5.8.

Рисунок 5.8 – Программная модель программного контроллера

Стек состоит из пятнадцати парных ячеек, т.к. в стек обычно сохраняется адрес и регистр статуса. Ввиду того, что стек ограничен по размерам, необходимо тщательно отслеживать, чтобы не произошло переполнение стека.

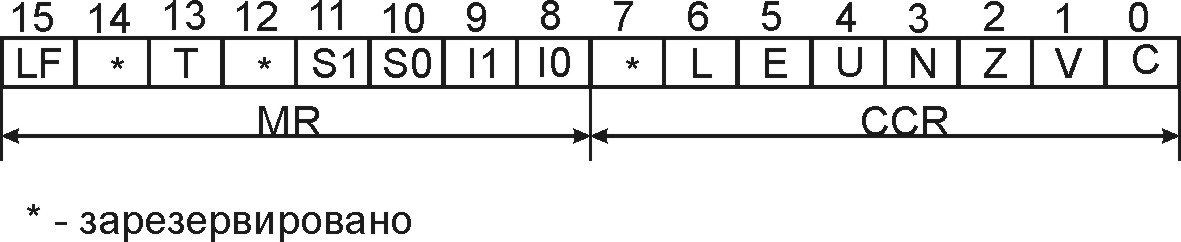

SP - указатель стека. Ввиду ограниченного объема стека (всего 30 ячеек памяти) значащими являются только 6 младших бит (0-5). SR- регистр статуса, состоит из двух частей (рисунок 5.9): регистра режима MR и регистра кодов условий CCR.

Рисунок 5.9 – Структура регистра статуса

Регистр кодов условий CCR определяет текущее состояние процессора для пользователя. После сброса все его биты равны 0.

Бит 0 – С, флаг переноса.

Бит 1 – V, флаг переполнения. Устанавливается при переполнении 56-разрядного результата.

Бит 2 – Z, флаг 0.

Бит 3 – N, флаг минуса, если результат отрицательный, то флаг равен 1.

Бит 4 – U, флаг денормализации, устанавливается в 1, если 2 старших бита равны.

Бит 5 – E, флаг расширения, обращается в 0, если 8 битов старшей части аккумулятора все равны 0 или 1.

Бит 6 – L, флаг ограничения, устанавливается при выполнении сдвига ограничения в АЛУ данных.

S1 – S0, данные биты определяют режим масштабирования для устройства сдвига ограничения данных АЛУ и позиции округления для MAC.

Бит 13 – Т, бит трассировки, если бит равен 1, то после выполнения каждой команды процессор останавливается и ждет разрешения на выполнение следующей команды от внутрисхемного эмулятора.

Бит 15 – флаг LF, бит становится равным 1 при выполнении цикла, после завершения цикла сам сбрасывается в 0.