- •Бийский технологический институт (филиал)

- •Цифровые измерительные устройства

- •Содержание

- •Различия между аналоговыми и цифровыми средствами измерений

- •Цифровые средства измерения напряжения

- •Измерение постоянного напряжения

- •Метод пространственного кодирования

- •Метод с промежуточным преобразованием напряжения во временной интервал (время-импульсный методы)

- •Метод двойного интегрирования

- •Метод с промежуточным преобразованием напряжения в частоту

- •Метод с промежуточным преобразованием напряжения в фазу

- •Кодово-импульсный метод (метод поразрядного кодирования)

- •Комбинированный метод преобразования

- •Автоматизация измерений

- •Автоматизация выбора предела (авп) измерений

- •Автоматическая коррекция погрешностей

- •Измерение переменного напряжения

- •Измерение частоты электромагнитных колебаний

- •Методы определения действительного значения частоты электромагнитных колебаний

- •Измерение параметров линейных элементов электрических цепей

- •Метод электронного счета

- •Цифровая обработка сигналов (dsp)

- •Типовые области применения dsp процессоров

- •Семейство 561хх. Основные характеристики

- •24 Разрядные dsp фирмы motorola

- •Обзор архитектуры и шинной организации dsp 560xx

- •Общая характеристика

- •Арифметико-логическое устройство данных

- •X0, x1, y0, y1 - буферные регистры; ак. Лу – аккумулятор логического устройства; ус – устройство сдвига; а, в – аккумуляторы процессора; шдх - шина данных х; усо – устройство сдвига-ограничения

- •Устройство генерации адресов (agu) и режимы адресации.

- •Блок регистров адреса r0-r7

- •Блок регистров смещения n0-n7

- •Блок регистров модификации м0-м7

- •Алу адресов

- •Линейный модификатор

- •Модульный модификатор

- •Модификатор реверсивного переноса

- •Программный контроллер

- •Структура программного контроллера

- •Регистр операционного режима (omr)

- •Таймер dsp56002

- •Программная модель таймерного модуля

- •Регистр таймера/счётчика tcr

- •Регистр статуса/управления tcsr

- •Литература

Устройство генерации адресов (agu) и режимы адресации.

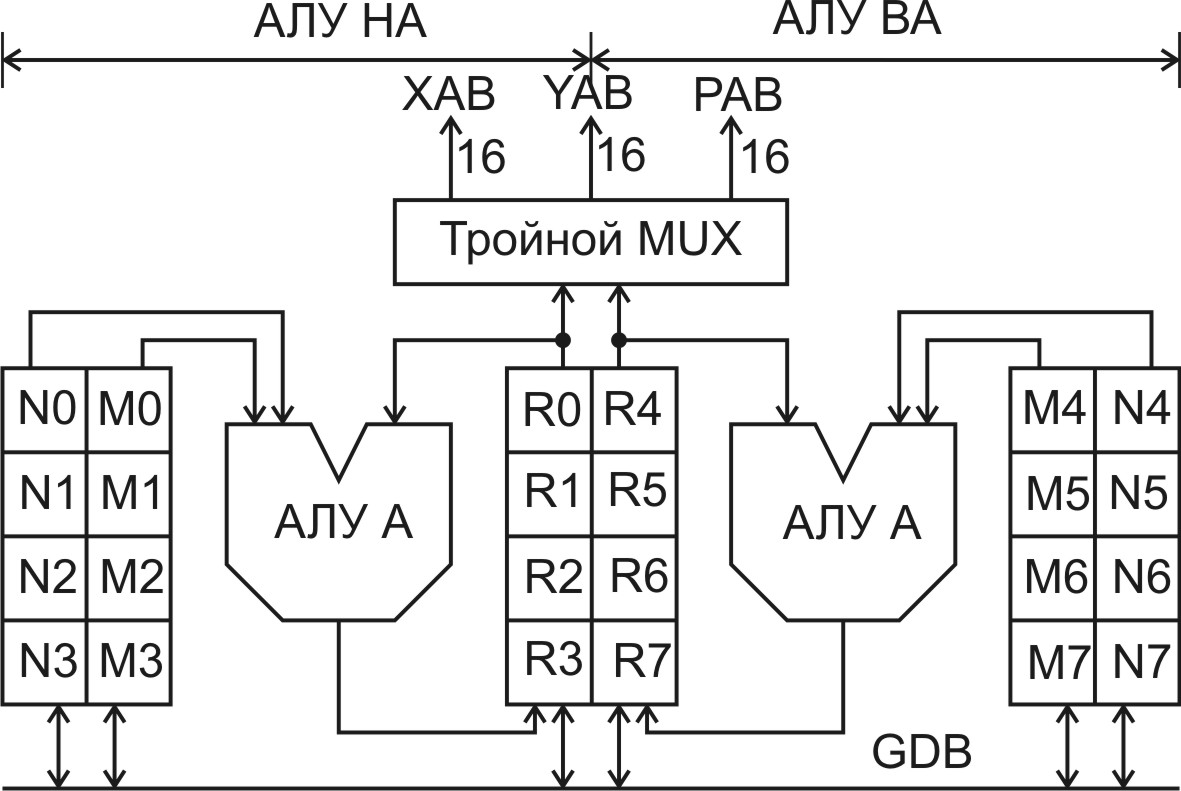

На рисунке 5.7. показаны структура AGU.

Все регистры AGU являются 24 разрядными, в которых 16 младших разрядов являются значащими. Старшие 8 бит всегда равны 0 и при записи не модифицируются.

АЛУ А – АЛУ адреса; АЛУ ВА – АЛУ верхних адресов; АЛУ НА – АЛУ нижних адресов

Рисунок 5.7 – Структура AGU

Блок регистров адреса r0-r7

Блок данных регистров состоит из двух подблоков регистров адреса, каждый из которых содержит четыре 16-ти битных регистра, которые содержат адреса для обращения к памяти. Каждый регистр может быть записан или прочитан через глобальную шину данных. Каждый адресный регистр может использоваться как вход АЛУ адресов для модификации регистров. Если параллельно осуществляется пересылка данных из памяти Х и из памяти У, то адресные регистры разделяются на два блока R0 – R3 и R4 – R7 соответственно.

Блок регистров смещения n0-n7

Данные регистры жестко привязаны к регистрам R в соответствии с номерами и так же разбиваются на два подблока. Регистры хранят смещение, которое используется для модификации адреса. Любой из регистров смещения может быть записан или прочитан через глобальную шину данных.

Блок регистров модификации м0-м7

Каждый из двух подблоков регистров модификации содержит четыре 16-ти битных регистра, которые определяют тип адресной арифметики для вычисления модификации регистров адреса R. Имеется так же жесткая привязка к регистрам R по номерам. Каждый из регистров М может быть прочитан или записан через глобальную шину данных. После сброса процессора все регистры модификации хранят число FFFF, что определяет линейный режим модификации адреса.

Алу адресов

Два идентичных АЛУ адресов рассчитывают 16-ти битный полный адрес, который может быть инкрементирован, декрементирован или выполнены сложные вычисления с использованием регистра смещения в соответствии с выбранным режимом адресации. DSP данного семейства обеспечивает 3 различных типа адресации:

прямую регистровую

косвенную регистровую

специальную регистровую.

При косвенной адресации возможны следующие модификации:

без модификации - адрес операнда содержится в регистре адреса Rn и не изменяется после выполнения команды;

постинкремент - адрес операнда содержится в регистре адреса Rn и после выполнения команды инкрементируется;

постдекремент - адрес операнда содержится в регистре адреса Rn и после выполнения команды декрементируется;

постинкремент со смещением Nn; после использования содержимое регистра R суммируется с содержимым регистра N и сохраняется в регистре R. Содержимое регистра N при этом не изменяется; Rn=Rn+Nn ;

постдекремент со смещением Nn; Rn= Rn - Nn ;

индексный со смещением Nn – адрес операнда находится как сумма регистров R и N; содержимое регистров R и N не изменяется;

предекремент; адрес, хранящийся в R, декрементируется до начала выполнения команды и сохраняется в нем же;

специальные типы модификации адреса АЛУ, которые позволяют существенно упростить создание структур данных в памяти для очередей, линий задержки, циклических буферов, стеков.