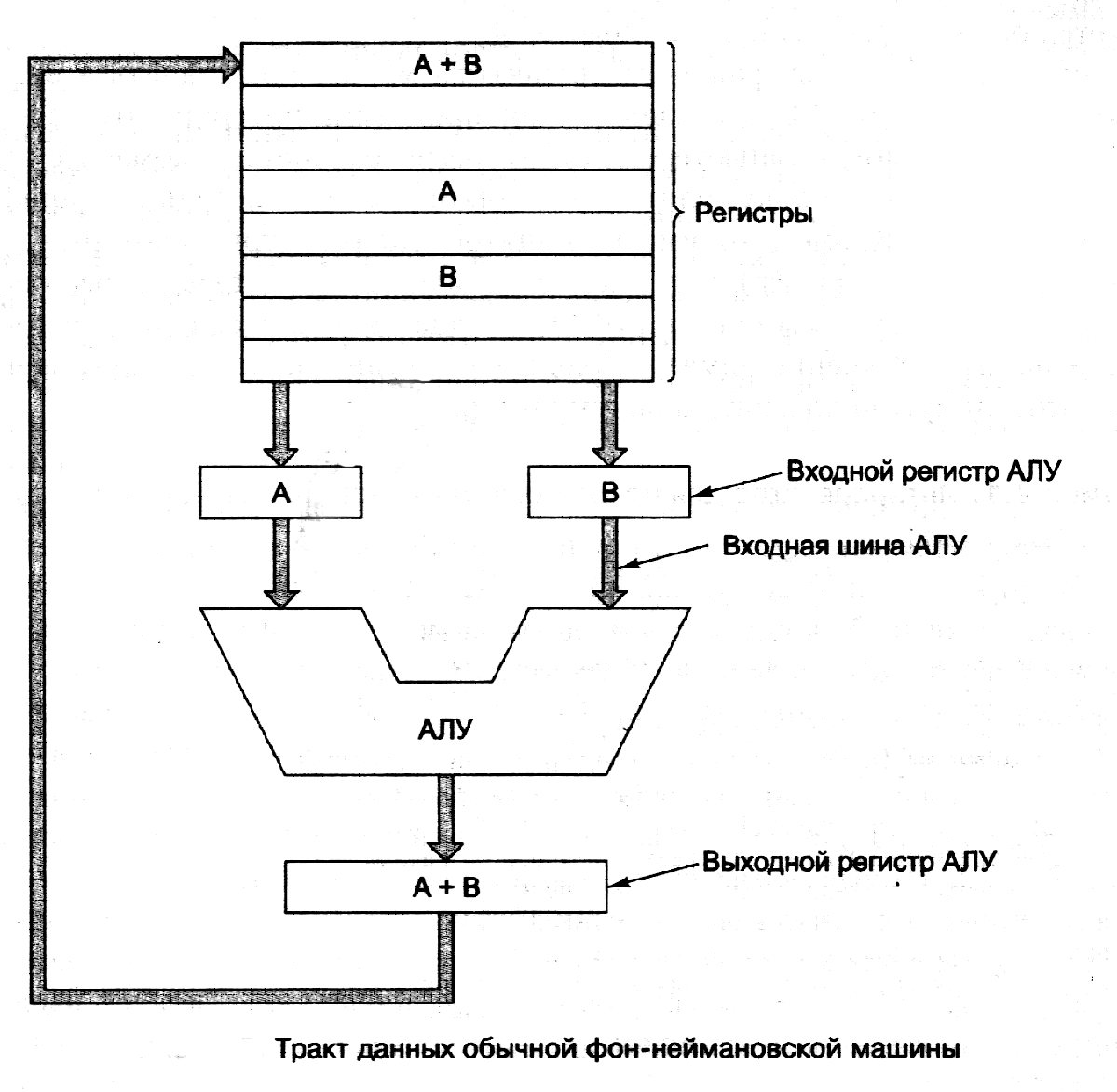

9.3 Регістрова пам’ять

Регістрова пам’ять (надоператйвна пам'ять) – це набір програмно-доступних регістрів, які знаходяться в регістровій пам'яті процесора (Рис. 9.4). В сучасних процесорах регістровий файл займає одне з центральних місць. Він використовується для локального збереження операндів, адрес команд та даних, індексів, а також дозволяє організовувати ефективний обмін даними між операційними пристроями процесора та основною пам'яттю. Вибір ефективної організації регістрового файла є одним із підходів, що дозволяє підвищити продуктивність комп'ютера. Як правило, організація регістрового файла належить до технічних характеристик комп'ютера.

Рис. 9.4

9.4. Оперативна пам'ять

Оперативна пам'ять (ОП) є одним з основних пристроїв будь-якої обчислювальної машини. Вона значною мірою обумовлює ефективність і швидкодію всієї системи. Параметри ОП такі, як об’єм, швидкодія, вважаються одними з найважніших характеристик комп’ютера.

Основна оперативна пам'ять ( рос. ОЗУ) або RAM (Random Access Memory) є пам’яттю з прямим доступом, тобто з безпосередньою адресацією будь-якої комірки (ячейки) пам'яті.

Блок елементів пам'яті вдає з себе двомірну матрицю (строчки та стовпці), на перетинах яких розташовані елементи пам'яті одного розряду зберігаємих кодів. Решта розрядів набирається паралельним підключенням аналогічних матриць.

х – стовпці, у – строчки

Двійковий адрес комірки складається з коду х і коду у. Це конструктивно набагато економніше, аби ми робили адресацію одним лінійним кодом. Наприклад, в матриці на 256 комірок при лінійній адресації знаходилося б 256 ліній вибірки, а при двомірній – 16 х 16, тобто тільки 32 лінії.

Блок-схема управління оперативною пам'яттю дана на Рис.9.5.

Рис 9.5

РА – регістр адреси

Рх, Ру – регістри адресів (координати х та у відповідно)

Дx, Дy – дешифратори адресів (стовпців і строк відповідно)

РД – регістр даних (запис і читання)

РУ – регістр управління, який виробляє сигнали для взаємодії всіх пристроїв

На Рис. 9.5 показана структура однорозрядної комірки пам’яті, що має одну лінію введення-виведення. Для того, щоб одержати багаторозрядну систему, треба застосувати n таких структур, як це показано на Рис. 9.6 для n=4.

Рис. 9.6

Таким чином, загальна ємність мікросхеми пам’яті дорівнює добутку глибини адресного простору на кількість матриць, або ліній введення-виведення. В нашому прикладі:

1 Мбайт * 4 = 4 Мбайта

Оперативна пам’ять енергозалежна, вона може працювати тільки при наявності напруги живлення. При вимиканні напруги інформація зникає. Але зате вона швидкодіюча. Швидкість звертання до неї (время доступа) в сотні тисяч раз менша ніж до пам'яті на магнітних дисках (6-7 нсек і 7-20 мсек відповідно)

Оперативна пам'ять буває двох типів в залежності від її фізичної реалізації: статична (SRAM) і динамічна (DRAM).Статична будується на тригерах, а динамічна використовує принцип зберігання електричного заряду на конденсаторах.

В динамічних запам’ятовуючих пристроях ‒ ЗП (DRAM) дані зберігаються у вигляді зарядів ємностей і основою елемента пам’яті (ЕП) є просто конденсатор невеликої ємності. Такий ЕП значно простіше тригерного, який містить 6 транзисторів, що дозволяє розмістити на кристалі набагато більше ЕП (в 4 ... 5 разів) і забезпечує динамічним ЗП максимальну ємність. У той же час конденсатор неминуче втрачає з часом свій заряд, і зберігання даних вимагає їх періодичної регенерації (через кілька мілісекунд). На Рис.9.7 дана спрощена схема однієї комірки DRAM.

Рис. 9.7 ЛЗС – лінія запису- читання, ЛВ – лінія вибірки

Коли транзистор ввімкнутий, на конденсатор С подається сигнал U запису або стирання одного біту інформації. Це певний рівень напруги (наприклад, 1 вольт – „1”, 0 вольт – „0”). При вимиканні транзистора ідеальний конденсатор міг би зберігати цей сигнал необмежений час. Але реальний конденсатор завжди має опір витіку (сопротивление утечки) R і поступово втрачає свій заряд. Тому інформацію в пам’яті типу DRAM необхідно періодично регенерувати (приблизно кожні 2 мсек). Це знижує швидкодію такої пам'яті.

Незважаючи на це саме пам'ять DRAM є найбільш розповсюдженою оперативною пам’яттю, бо вона набагато дешевше ніж SRAM.

Основні характеристики пам'яті:

- ємність

- швидкодія

- розрядність

- пропускна спроможність, або швидкість передачі даних

-та інші: частота шини, структурна організація, конструктивні відмінності, ціна, умови експлуатації.

Ємність оперативної пам'яті вимірюється в мегабайтах. Для комп’ютерів широкого призначення він сягає 256 Мбайт– 4 Гбайт і більше.

Швидкодія ОП вимірюється в наносекундах (1нс = 10-9 сек). Вона складається з часу позиціонування адреси за координатами х та у (час доступу) і часу вибору даних. Ці терміни приблизно однакові і для сучасних ОП складають 4-10 нсек.

Треба зауважити, що швидкодія оперативної пам'яті зазвичай набагато нижче ніж швидкодія процесора, внутрішня пам'ять якого побудована на тригерних регістрах. Тому розробники пам'яті застосовують різні структурні рішення (паралелізм вибірки, сторінкова організація тощо) для підвищення швидкодії.

Велике значення для продуктивності тандему процесор-пам'ять має пропускна спроможність шин обміну даними між процесором і пам’яттю. Вона залежить від фізичної частоти передачі даних по шинах, а також розрядності шин – 8, 16, 32, 64...

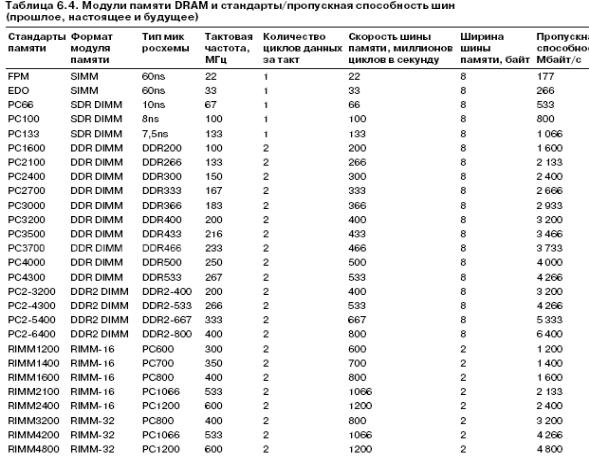

В поточний час (2008 – 2010 р.) найбільш розповсюдженою пам’яттю динамічного типу є SDRAM (синхронна DRAM) та RDRAM (RAMBUS DRAM). SDRAM має час доступу 6-9 нсек, частоту шини даних 66, 133, 150 Мгц, пропускну спроможність 256-1000 Мбайт/с. RDRAM має час доступу 4 нсек, частоту шини до 800 мгц, пропускну спроможність до 6 Гбайт/с. Але велику вартість – біля 1000 доларів за 128 Мбайт.

Всі параметри оперативної пам'яті з часом дуже швидко змінюються в кращу сторону, в тому числі і вартість. Сьогодні прийнятна ринкова ціна становить десь 15-20 доларів за 64 Мбайта, 30 за 128 Мбайт.

В пам’яті комп’ютерів з різних причин, наприклад, через сплески напруги джерел живлення, можуть бути збої інформації. Вважається, що в надійних система в інформаційних кодах можуть бути зіпсовані тільки поодинокі розряди. В такому випадку є можливість боротьби з помилками (виявляти чи, навіть, виправляти) за рахунок використання в кожній комірці пам’яті спеціалізованих додаткових розрядів – кодів Хеммінга. Найбільш часто використовується один додатковий розряд – розряд парності, який фіксує парність одиниць в інформаційному слові і таким чином виявляє поодинокі помилки. Збільшуючи число контрольних розрядів можна не тільки виявити, але і виправляти поодинокі помилки. Для цього розроблена спеціальна теорія і алгоритми.

Конструктивно оперативна пам’ять виконана у вигляді невеликих друкованих плат з декількома мікросхемами пам’яті на платі. В старих моделях ( 5 років тому) такі модулі були двох типів. SIMM (Single Inline Memory Module) – з одностороннім розташуванням виводів, та DIMM (Dual Inline Memory Module) – з двохстороннім розташуванням виводів. Модулі SIMM мають об’єм пам’яті до 128 Мбайт, 72 контакти і швидкість передачі даних за один цикл 32 біта. Модулі DIMM мають об’єм пам’яті до 256 Мбайт, 168 контактів і швидкість передачі даних – 64 біт за цикл. В багатьох комп’ютерах передбачено встановлення до чотирьох модулів пам’яті, тобто загальних об’єм може сягати 0,5 – 1 Гбайт.

Сучасні персональні

комп’ютери комплектуються різноманітними

видами оперативної пам’яті, але на

даний час дуже широко використовується

тільки три види оперативної пам’яті:

DDR SDRAM, DDR2

SDRAM, DDR3

SDRAM, а наступні вже

застарілі: SIMM, SDRAM

(DIMM), RD RAM,

Сучасні персональні

комп’ютери комплектуються різноманітними

видами оперативної пам’яті, але на

даний час дуже широко використовується

тільки три види оперативної пам’яті:

DDR SDRAM, DDR2

SDRAM, DDR3

SDRAM, а наступні вже

застарілі: SIMM, SDRAM

(DIMM), RD RAM,

9.5. КЕШ- пам'ять

Процесори завжди працювали швидше ніж пам'ять. Удосконалення процесорів іде в основному шляхом підвищення їх швидкодії, в той час, коли удосконалення пам’яті зазвичай направлено перш за все на збільшення її об’єму. На практиці така невідповідність в швидкості приводить до того, що при безпосередній взаємодії швидкого процесора з повільною пам’яттю, процесор при кожному звертанні до пам’яті простоює, в результаті чого знижується загальна ефективність комп’ютера.

Кеш-пам'ять запам'ятовує копії інформації, що передається між пристроями (перш за все між процесором і основною пам'яттю). Вона має невелику ємність в порівнянні з основною пам'яттю і більш високу швидкодію (реалізується на тригерних елементах пам'яті).

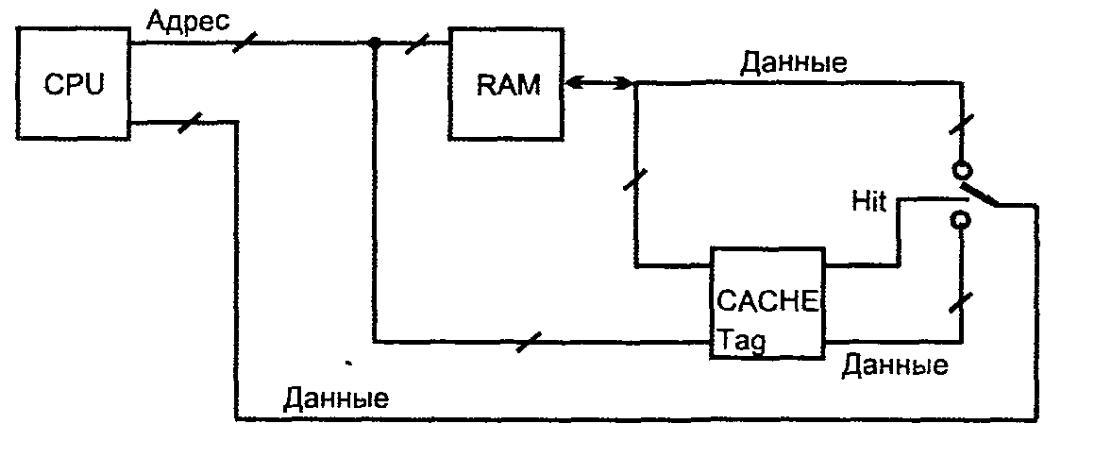

Рис. 9.7. Схема «кешировання»

При читанні даних спочатку виконується звернення до кеш-пам'яті (Рис. 9.8). Якщо в кеш є копія даних адресованої комірки основної пам'яті, то кеш виробляє сигнал Hit (попадання) і видає дані на загальну шину даних. В іншому випадку сигнал Hit не виробляється і виконується читання з основної пам'яті і одночасний запис зчитаних даних в кеш.

Для уникнення цього недоліку використовується проміжна високошвидкісна пам'ять, як буфер між процесором і оперативною пам’яттю. Ця пам'ять відносно невеликого об’єму називається кеш-пам’яттю ( cache ). Вона побудована на тригерах (SRAM) і має час доступу не більш 2 нсек. Об’єм кеш-пам'яті порівняно невеликий – в межах 512 КВ, але в останніх моделях – 1ГВ і більше.

Ідея кеш-пам’яті проста: в цю пам’ять заздалегідь записуються дані, які будуть використані в поточному циклі роботи процесора. Якщо цих даних достатньо, то можна досягти синхронної роботи процесора і пам’яті.

Ефективність кешування обумовлюється тим, що більшість прикладних програм мають циклічний характер і багаторазово використовують одні й ті ж дані. Тому після першого використання даних з відносно повільною основної пам'яті повторні звернення вимагають менше часу. До того ж при використанні процесором кеш-пам'яті основна пам'ять звільняється, і можуть виконуватися регенерація даних в динамічній ОП або використання пам'яті іншими пристроями.

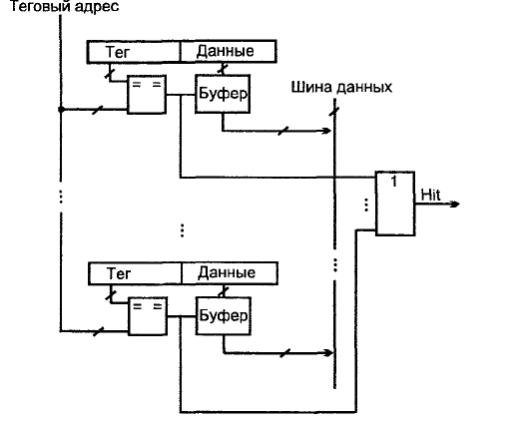

Об'єм кеш-пам'яті багато менше ємності основної пам'яті і будь-яка одиниця інформації, що поміщається в кеш, повинна супроводжуватися додатковими даними (тегом), що визначає, копією якої комірки основної пам'яті є ця одиниця інформації.

Рис. 9.8. Асоциативна кеш-пам’ять

В асоціативній кеш-пам'яті, структура якої показана на Рис. 9.8, кожна комірка зберігає дані, а крі того в полі "тег" - повний фізичну адресу інформації, копія якої записана. За будь-яких обмінах фізична адреса запитуваної інформації порівнюється з полями "тег" всіх комірок і при збігу їх в будь-якій комірці встановлюється сигнал Hit.

При читанні і значенні сигналу Hit = 1 дані видаються на шину даних, якщо ж збігів немає (Hit = 0), то при читанні з основної пам'яті дані разом з адресою поміщаються у вільну комірку кеш-пам'яті.

Ефективність кеш-пам’яті відображається коефіцієнтом збігу, чи успішності, який дорівнює відношенню вдалих звернень до кеш-пам’яті до загального числа звернень до пам’яті.

В перших спробах використання кеш-пам’яті в ній збереглися як дані, так і програми. Але в поточному часі існує тенденція використання розподіленої кеш-пам’яті, коли для даних і команд існують різні кеш-пам’яті. Розподілена кеш-пам’ять дозволяє здійснювати паралельний доступ до команд і операндів, що необхідно при організації конвеєрних архітектур в процесорах.

Щоб мінімізувати час доступу до інформації, в сучасних персональних комп’ютерах передбачено декілька рівнів кеш-пам’яті: перший(L1), другий (L2) та іноді третій (L3). Кеш L1 розташована прямо в корпусі процесора, кеш L2 і L3 розташована на системній платі поблизу від процесора.

Треба зауважити, що кеш-пам’ять використовується не обов’язково тільки при обслуговування процесора. Вона часто використовується також при обміні даними з другими швидкодіючими пристроями, наприклад, з вінчестерами.