- •Многоуровневая компьютерная организация Общая классификация систем обработки данных

- •Многоуровневая компьютерная организация

- •Историческое развитие архитектуры эвм

- •Периферийные процессоры и шины

- •Многопрограммный режим работы

- •Введение в процессор нескольких специальных алу

- •Архитектура «Эльбрус»

- •Широкий спектр компьютеров

- •Архитектура процессоров Микропрограммный способ выполнения команд

- •Порядок функционирования устройства

- •Cisc и risc архитектуры

- •Cisc-процессора.

- •Risc-процессора

- •Сравнение архитектур

- •Скалярные и векторные процессоры

- •Конвейеры

- •Конфликты

- •Динамическое исполнение команд

- •Спекулятивное исполнение

- •Предикация

- •Опережающее чтение

- •Буфер прогнозирования условных переходов

- •Многоконвейерная архитектура

- •Суперскалярная архитектура

- •Vliw процессоры

- •Epic архитектура

- •Архитектура x86, x86-64, ia-32 и ia-64

- •Основы многопоточной архитектуры

- •Сравнение параллельной и конвейерной организации вычислительных систем

- •Многоядерные или многопроцессорные системы

- •Кластерная архитектура

- •Организация оперативной памяти Основные характеристики систем памяти

- •Основная память

- •Динамическая память

- •Асинхронная память

- •Синхронный режим

- •Динамические озу для видеоадаптеров

- •Многопортовые озу

- •Управление вводом/выводом. Файловая система Внешние запоминающие устройства.

- •Повышение отказоустойчивости

- •Код Хэмминга (дополнительно)

- •Биты паритета (дополнительно)

- •Шины и системы ввода/вывода

- •Подключение памяти и систем ввода/вывода к цп через отдельные шины

- •Совместно используемые линии данных и адреса

- •Подключение системы ввода/вывода к шине на общих правах с цп и памятью

Сравнение параллельной и конвейерной организации вычислительных систем

Параллелизм и конвейеризация имеют одну цель – повышение производительности вычислительной системы. Оба подхода предполагают достижения этой цели за счет избыточности аппаратуры вычислительной системы. Организация вычислительного процесса в этих подходах сильно различается:

Параметр |

Параллелизм |

Конвейеризация |

Базовая структура |

Независимые исполнители подзадач на отдельных блоках аппаратуры |

Разбитие функции на подфункции |

Производительность |

N результатов каждые T секунд |

Результат каждые T/N секунд |

Основной период синхронизации |

Время выполнения одной функции |

Выполнение одной ступени или подфункции |

Типичная архитектура |

SIMD, MIMD |

SISD, MISD |

Предпочтительная структура задачи |

Матричные задачи с длинами векторов, равными числу процессоров. Процессы, подлежащие разбиению на независимые части |

Одномерные векторы с произвольной длиной, классические задачи |

Типичная организация памяти |

Многократно повторяемые независимые участки |

Одна многократно расслоенная память |

Особенности управления |

Осуществляется программистом |

Осуществляется аппаратурой |

Ограничения |

Стоимость, структура задач |

Элементная база, скорость доступа к памяти |

Надежность |

Легкодостижима за счет горячего резерва |

Обходится дорого за счет не модульной организации |

Многоядерные или многопроцессорные системы

Компиляция операционных систем из исходных кодов

Сборка из уже откомпилированного кода

Архитектуры:

Симметрично многопроцессорная

Массовая параллельная

Гибридная

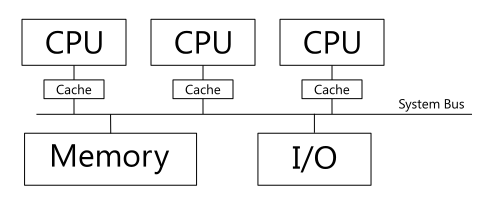

SMP-архитектура

Symmetric Multiprocessing

Главная особенность такой архитектуры – наличие общей физической памяти, разделяемой всеми процессорами.

По сути, это 1 компьютер с несколькими равноправными процессорами, все остальное представлено в одном экземпляре (память, периферия, и так далее). Слово «симметричная» означает, что каждый процессор может делать то же, что и любой другой. Это выражается следующим образом:

Доступ к памяти

Может выполнять любую операцию ввода-вывода

Процессор может прерывать другие процессоры и устройства, может прерываться сам

В SMP системах все идет через общую шину.

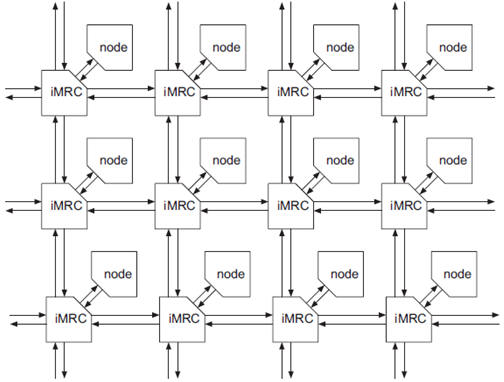

MPP-архитектура

В основе этой архитектуры лежит транспьютер. Это мощный универсальный процессор, особенностью которого является наличие четырех линков, каждый из которых состоит из трех частей, которые служат для передачи данных в противоположном направлении. Все процессоры могут обмениваться данными. После передачи одного байта транспьютер ожидает подтверждения. Большая прикладная программа разбивается на процессы между узлами.

MRC – маршрутизатор, представляющий собой набор портов. Порты MRC могут связываться между собой, могут связываться с маршрутизаторами, а также к ним может подключаться процессор. Node – процессорные узлы трех типов:

Вычислительные

Сервисные (Unix)

Узлы ввода-вывода (могут подключаться к общим ресурсам, дискам или сетям)

Пример: Intel Paragon выполнен на архитектуре i8600, IBM RS/6000SP