- •Многоуровневая компьютерная организация Общая классификация систем обработки данных

- •Многоуровневая компьютерная организация

- •Историческое развитие архитектуры эвм

- •Периферийные процессоры и шины

- •Многопрограммный режим работы

- •Введение в процессор нескольких специальных алу

- •Архитектура «Эльбрус»

- •Широкий спектр компьютеров

- •Архитектура процессоров Микропрограммный способ выполнения команд

- •Порядок функционирования устройства

- •Cisc и risc архитектуры

- •Cisc-процессора.

- •Risc-процессора

- •Сравнение архитектур

- •Скалярные и векторные процессоры

- •Конвейеры

- •Конфликты

- •Динамическое исполнение команд

- •Спекулятивное исполнение

- •Предикация

- •Опережающее чтение

- •Буфер прогнозирования условных переходов

- •Многоконвейерная архитектура

- •Суперскалярная архитектура

- •Vliw процессоры

- •Epic архитектура

- •Архитектура x86, x86-64, ia-32 и ia-64

- •Основы многопоточной архитектуры

- •Сравнение параллельной и конвейерной организации вычислительных систем

- •Многоядерные или многопроцессорные системы

- •Кластерная архитектура

- •Организация оперативной памяти Основные характеристики систем памяти

- •Основная память

- •Динамическая память

- •Асинхронная память

- •Синхронный режим

- •Динамические озу для видеоадаптеров

- •Многопортовые озу

- •Управление вводом/выводом. Файловая система Внешние запоминающие устройства.

- •Повышение отказоустойчивости

- •Код Хэмминга (дополнительно)

- •Биты паритета (дополнительно)

- •Шины и системы ввода/вывода

- •Подключение памяти и систем ввода/вывода к цп через отдельные шины

- •Совместно используемые линии данных и адреса

- •Подключение системы ввода/вывода к шине на общих правах с цп и памятью

Томский государственный университет систем управления и радиоэлектроники

Конспект по предмету

Архитектура вычислительных систем

Составил:

Черноусов Иван, гр. 430-2

Материалы предоставили:

Соловьев Виктор, гр 439-1

Рыжкова Анастасия, гр. 430-1

Егерь Марина, гр. 430-2

Анищенко Анастасия, гр. 430-1

Извозчикова Алина, гр. 430-2

Никонова Полина, гр. 430-2

Томск, 2014

Rev 4/16.06.14

Оглавление

Многоуровневая компьютерная организация 4

Общая классификация систем обработки данных 4

Многоуровневая компьютерная организация 5

Историческое развитие архитектуры ЭВМ 6

Общее адресное пространство ЭВМ 7

Концепция модульности 8

Модульная архитектура 8

Пути повышения быстродействия или мощности ЭВМ 9

Параллельные сумматоры 9

Периферийные процессоры и шины 9

Многопрограммный режим работы 9

Введение в процессор нескольких специальных АЛУ 10

Архитектура «Эльбрус» 10

Широкий спектр компьютеров 10

Архитектура процессоров 12

Микропрограммный способ выполнения команд 12

Порядок функционирования устройства 12

CISC и RISC архитектуры 13

CISC-процессора. 13

RISC-процессора 13

Сравнение архитектур 14

Скалярные и векторные процессоры 14

Конвейеры 14

Конфликты 15

Динамическое исполнение команд 16

Спекулятивное исполнение 16

Предикация 17

Опережающее чтение 17

Буфер прогнозирования условных переходов 17

Многоконвейерная архитектура 17

Суперскалярная архитектура 18

VLIW процессоры 18

EPIC архитектура 19

Архитектура x86, x86-64, IA-32 и IA-64 19

Intel Itanium 20

Основы многопоточной архитектуры 20

Сравнение параллельной и конвейерной организации вычислительных систем 21

Многоядерные или многопроцессорные системы 22

SMP-архитектура 22

MPP-архитектура 22

Кластерная архитектура 23

Организация оперативной памяти 24

Основные характеристики систем памяти 24

BIOS 24

Основная память 25

Динамическая память 26

Асинхронная память 26

Синхронный режим 27

Динамические ОЗУ для видеоадаптеров 28

Многопортовые ОЗУ 29

Управление вводом/выводом. Файловая система 30

Внешние запоминающие устройства. 30

Повышение отказоустойчивости 30

Код Хэмминга (дополнительно) 30

Биты паритета (дополнительно) 31

RAID 0 31

RAID 1 31

RAID 2 32

RAID 3 32

RAID 4 32

RAID 5 33

Шины и системы ввода/вывода 34

Подключение памяти и систем ввода/вывода к ЦП через отдельные шины 34

Совместно используемые линии данных и адреса 34

Подключение системы ввода/вывода к шине на общих правах с ЦП и памятью 35

PCI 36

PCMCIA 36

PCI-E 37

SATA 37

Многоуровневая компьютерная организация Общая классификация систем обработки данных

Рассмотрим подробнее пункты приведенной схемы.

Система обработки данных – совокупность технических средств и программного обеспечения, предназначенного для обработки данных.

Электронная вычислительная машина – СОД из одной машины. Машина должна быть надежной и производительной.

Вычислительный комплекс – совокупность технических средств, включающих несколько ЭВМ или процессоров и общесистемное (базовое) ПО

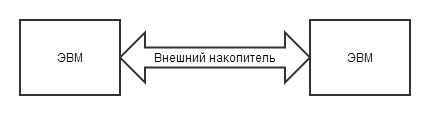

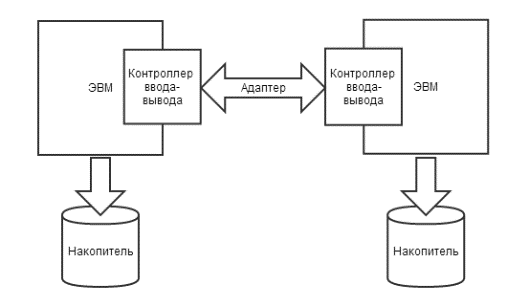

Многомашинный вычислительный комплекс - СОД из нескольких независимых машин. Может быть организован:

Косвенным способом

Прямая связь

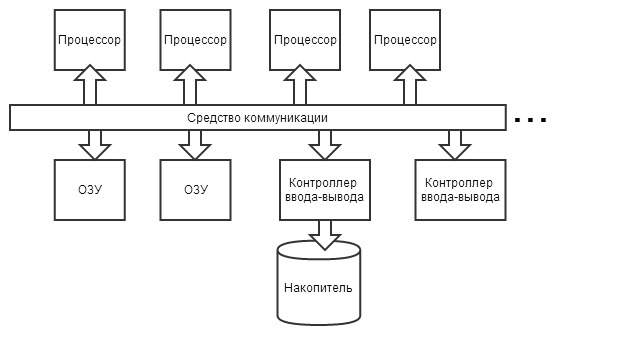

Многопроцессорный вычислительный комплекс – комплекс, использующий пару или больше физических процессоров. Термин также относится к способности комплекса поддержать больше чем один процессор и/или способность распределить задачи между ними.

Вычислительная система – СОД, настроенная на решение задач некоторой области применения (по сути, вычислительный комплекс и проблемно-ориентированное ПО к нему)

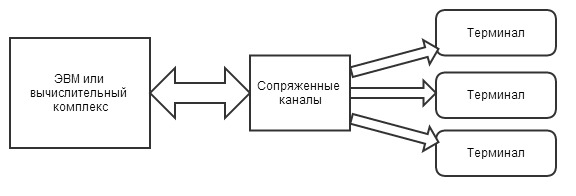

Системы телеобработки (СТО) – системы, предназначенный для обработки данных, передаваемых по каналам связи

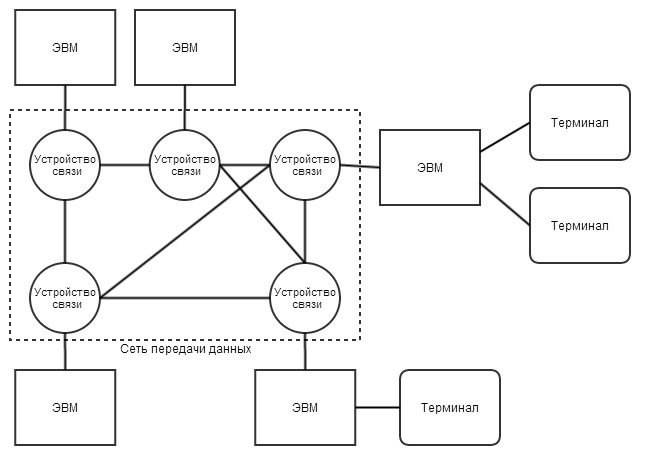

Сеть ЭВМ – Совокупность ЭВМ, объединенных сетью передачи данных.

Сеть передачи данных – базовая сеть передачи данных, состоящая из устройств передачи данных, и каналов, их соединяющих.

Вычислительная сеть – Совокупность сети передачи данных, основанной на ней сети ЭВМ и терминальная система для взаимодействия.

Многоуровневая компьютерная организация

Вычислительная машина – это комплекс технических и программных средств, предназначенный для автоматизации, подготовки и решения задач пользователей.

Под архитектурой обычно понимают логическое построение вычислительной машины. Сюда не входят вопросы построения физических устройств. Рассмотрим архитектуру ЭВМ с точки зрения организации логической структуры. Выделяют четыре уровня детализации архитектуры:

Уровень черного ящика. ЭВМ рассматривается как устройство, способное хранить и обрабатывать информацию, а также обмениваться ей с внешним миром.

Уровень общей архитектуры. ЭВМ рассматривается как совокупность запоминающих устройств (основной памяти), контроллеров ввода-вывода, центрального процессора и шины, соединяющей компоненты.

Уровень процессора. Рассматривается внутреннее устройство центрального процессора ЭВМ, в частности, блок вычислений с плавающей запятой, устройство управления, арифметико-логическое устройство, регистры и шины обмена данными.

Уровень устройства управления процессора. Рассматривается внутреннее устройство компонент процессора – так, например, устройство управления центрального процессора разбивается на устройства управления

регистрами,

шиной,

памятью,

логикой формирования управления и

логикой программной последовательности.

Представим себе компьютер как стек виртуальных машин:

N. Виртуальная машина N, машинный язык ЯN … 1. Виртуальная машина 1, машинный язык Я1 0. Виртуальная машина 0, машинный язык Я0

Традиционно, под уровнем 0 подразумевают аппаратное обеспечение машины. Это цифровой логический уровень, объекты которого – вентили. Каждый вентиль:

Имеет один или несколько цифровых входов или сигналов, сопоставляемых с 0 или 1.

Каждый вентиль вычисляет простую функцию этих сигналов.

Несколько вентилей формируют один бит памяти.

Биты памяти, объединенные в группы по 8, 16, 32 … формируют регистры.

Каждый регистр может содержать одно двоичное число (ограниченного размера).

Опишем классическую структуру уровней ЭВМ.

5. Уровень языка прикладных программистов транслируется или интерпретируется на 4. Уровень Ассемблера (приложение) транслируется на 3. Уровень операционной системы (ядро ОС) интерпретируется (или программа) на 2. Уровень архитектуры набора команд (центральный процессор) интерпретируется (или микропрограмма) на 1. Уровень микроархитектуры (аппаратура) 0. Цифровой логический уровень (вентили)