- •У множители напряжения

- •Регистры

- •Параллельные регистры (регистры памяти)

- •1 Параллельный регистр

- •Регистры сдвига

- •3.2.1. Сдвиговый регистр в динамическом режиме.

- •Цифровые запоминающие устройства

- •Информационная ёмкость цифрового запоминающего устройства

- •Классификация[править | править исходный текст]

- •Однофазный двухполупериодный выпрямитель со средней точкой

- •Особенности выбора выпрямительных диодов

- •Однофазный двухполупериодный выпрямитель со средней точкой

- •Способы реализации цап с взвешенным суммированием токов

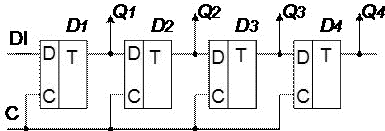

Регистры сдвига

Регистры сдвига представляют собой цепочку последовательно включённых D-триггеров или RS- и JK-триггеров, включённых в режим D-триггера. Появление импульса на тактовом входе регистра сдвига вызывает перемещение записанной в нём информации на один разряд вправо или влево. Как и другие регистры, регистры сдвига используются для записи, хранения и выдачи информации, но основным их назначением является преобразование последовательного кода в параллельный или параллельного в последовательный.

Схема 4-разрядного регистра сдвига приведена на рисунке 55. Схема работает следующим образом. Благодаря тому, что выход предыдущего разряда соединён со входом «D» последующего, каждый тактовый импульс устанавливает последующий триггер в состояние, в котором до этого находился предыдущий. Так осуществляется сдвиг информации вправо.

Рисунок 54 4-разрядный регистр сдвига

Вход «D» первого триггера служит для приёма в регистр входной информации DI в виде последовательного кода. С каждым тактовым импульсом на этот вход должен подаваться код нового разряда входной информации.

Запись

параллельного кода информации может

быть произведена через нетактируемые

установочные входы ![]() триггеров (на рисунке 55 не показаны).

триггеров (на рисунке 55 не показаны).

С выхода «Q4» последнего триггера снимается последовательный выходной код. Код на этом выходе регистра появляется с задержкой относительно входного последовательного кода на число периодов тактовых импульсов, равное числу разрядов регистра.

Параллельный выходной код можно снять с выходов Q1…Q4 всех триггеров регистра сдвига, снабдив их выходными ключами, подобными выходным ключам параллельного регистра (См. рисунок 54,а).

3.2. Сдвиговый регистр.

3.2.1. Сдвиговый регистр в статическом режиме.

3.2.1.1. Режим сдвига вправо.

Логическая единица смещается от Q0 к Q3.

3.2.1.2. Режим сдвига влево.

Логическая единица смещается от Q3 к Q0.

3.2.1.3. Режим параллельной загрузки.

Данные на выходах Q0, Q1, Q2 и Q3 соответствуют тем, которые были поданы на входы D0, D1, D2 и D3.

3.2.1.4. Режим хранения.

При подаче на входы S1 и S2 логического нуля, регистр переходит в режим хранения информации, при этом сигналы на входах параллельной загрузки D0-D3 и последовательной загрузки DL и DR не влияют на состояние выходов Q0-Q3. Значение на выходах сохраняется.

Таблица истинности регистра сдвига

R |

S0 |

S1 |

Q0t |

Q1t |

Q2t |

Q3t |

0 |

X |

X |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

DR |

Q0t-1 |

Q1t-1 |

Q2t-1 |

1 |

1 |

0 |

DR |

Q0t-1 |

Q1t-1 |

Q2t-1 |

1 |

0 |

1 |

Q1t-1 |

Q2t-1 |

Q3t-1 |

DL |

1 |

0 |

1 |

Q1t-1 |

Q2t-1 |

Q3t-1 |

DL |

1 |

1 |

1 |

D0 |

D1 |

D2 |

D3 |

1 |

0 |

0 |

Q0t-1 |

Q1t-1 |

Q2t-1 |

Q3t-1 |