- •1)Обобщенная схема цвм.

- •2)Автомат Мура.

- •3)Основы анализа логических схем с обратными связями.

- •4)Анализ логических схем с помощью карт Карно.

- •7)Элементарные автоматы. Элементарные автоматы с одним входом.

- •8)Элементарные автоматы с двумя входами.

- •9)Обобщенная схема цифрового автомата.

- •10) Синтез комбинационных схем с помощью сднф и диаграмм Вейча.

- •11)Синтез цифровых автоматов.

- •Дешифраторы (декодеры)

- •15,16) 15 И 16 билеты совместно, про rs – триггеры на и элементах в 5 билете.

- •17)Серии цифровых логических микросхем (мс). Мс выключающие триггеры.

- •18)Синтез триггерных схем.

- •19)Д-триггер.

- •20)Т-триггер.

- •21)Jk-триггер.

- •22)Двойные триггеры.

- •23)Синтез двойного jk-триггера на элементах “и-не”.

- •24)Синтез двойного jk-триггера на элементах “или-не”.

- •25)Синхронный rs-триггер с динамическим управлением.

- •26)Синхронный jk-триггер с динамическим управлением.

- •27)Синтез синхронных триггеров со статическим управлением.

- •28)Регистры.

- •29) Регистр к555ир1

- •30) Регистр с тремя выходными состояниями. Кр 1804 ир1.

- •31) Счетчики. Двоичные суммирующие счетчики с последовательным переносом.

- •33) Вычитающие двоичные счетчики.

- •35)Десятичные счетчики.

- •36)Счетчик с произвольным модулем счета на jk – триггере.

- •37) Счетчики с принудительным насчетом сигналов

- •39)Делители частоты с модулем деления на 3.

- •40)Сумматоры. Сумматор на регистрах и кс суммирования.

- •43)Основные элементы памяти.

- •44)Организация памяти в вычислительной технике.

- •45) Дешифраторы. 3-х разрядный дешифратор на элементах “и”.

15,16) 15 И 16 билеты совместно, про rs – триггеры на и элементах в 5 билете.

Из таблицы состояний может быть получено уравнение, описывающее поведение триггера. Это уравнение носит название характеристического уравнения триггера. Оно показывает, как меняется состояние триггера в зависимости от текущих значений состояния и входов.

Для

получения упрощенного аналитического

выражения, описывающего поведение

RS-триггера, построим карту Карно и

проведем соответствующие контуры (рис.

3.3, в). Полученное характеристическое

уравнение триггера имеет вид

![]() .

.

Применив

закон де Моргана преобразуем полученные

выражение в базис И-НЕ:

![]() .

.

Схема RS- триггера, реализованного в выбранном базисе, приведена на рис. 3.3, г.

Из формулы RS - триггера видно, что при реализации его в базисе И-НЕ, триггер управляется сигналами низкого уровня, т.е. уровня лог. "0" (если не предусмотрены инверторы). Для приведения поведения триггера, выполненного на элементах И-HE, в соответствие с таблицей состояний сигналы S и R необходимо инвертировать.

Из анализа схемы рис. 3.3, г очевидно, что простой RS триггер можно сконструировать, соединив “крест-накрест” два элемента И-НЕ.

Входные

линии триггера обозначены как

![]() и

и

![]() ,

поскольку триггер устанавливается при

=0

и сбрасывается при

=0.

Такой триггер иногда называют RS-триггер

с инверсными входами или конъюнктивной

бистабильной ячейкой.

,

поскольку триггер устанавливается при

=0

и сбрасывается при

=0.

Такой триггер иногда называют RS-триггер

с инверсными входами или конъюнктивной

бистабильной ячейкой.

Схема RS-триггера, реализовнная в базисе И-HЕ в соответствии с таблицей состояний, приведена на рис. 3.3, д. Для построения RS -триггера на элементах ИЛИ-НЕ приведем формулу триггера в базис ИЛИ-НЕ

![]() .

.

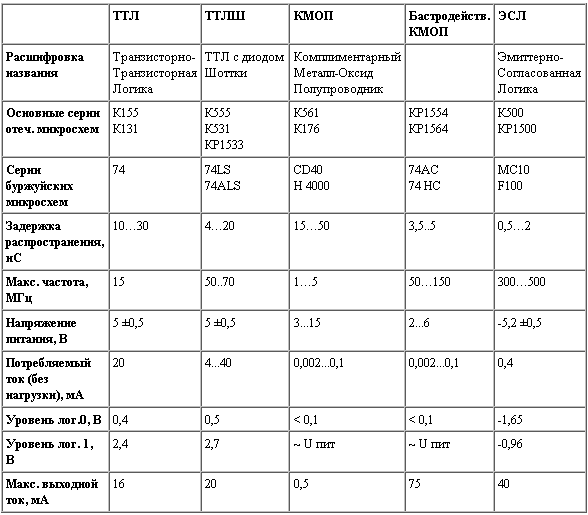

17)Серии цифровых логических микросхем (мс). Мс выключающие триггеры.

18)Синтез триггерных схем.

19)Д-триггер.

D-триггером называют синхронный триггер, имеющий два входа: вход данных D и вход синхронизации С. Этот тип триггера исключительно широко используется в цифровых устройствах. Другие его названия: прозрачная защелка (transparent latch), D-триггер, управляемый уровнем синхросигнала. D-триггер переключается только по сигналу на С-входе и притом в состояние, предписываемое D-входом. Условное обозначение D-триггера показано на рис. 4.3, а.

а) б)

Рис.4.3. D – триггер

На рис. 4.3, б показан универсальный способ построения D-триггера из синхронного RS-триггера: с помощью инвертора 1 однофазный вход данных D превращается в парафазный и подается на S- и R -входы.

Изменения D-входа при С= 0 никак не влияют на состояние выхода Q: триггер заперт по С-входу и находится в режиме хранения. Фронт С-сигнала вызывает переключение триггера в то состояние, которое было к этому моменту на входе D. При С=1 защелка прозрачна: любое изменение D-входа вызывает изменение выхода Q. По спаду синхросигнала триггер – защелка фиксирует на выходе то состояние, которое было на D-входе непосредственно перед этим моментом. Следующее изменение Q будет возможно только по фронту следующего синхроимпульса. Если на С-вход подать постоянный единичный уровень, то свойство запоминания у защелки проявляться никак не будет и она будет выполнять функции обычного буферного усилителя мощности в тракте передачи данных.

Чтобы процесс фиксации состояния D-входа прошел без сбоев, т. е. был бы однозначно предсказуемым, переходной процесс в схеме защелки, вызванный срезом С-сигнала, не должен накладываться на переходной процесс, вызванный переключением D-входа. Это значит, что всякие изменения состояния D-входа должны прекратиться за некоторое время до среза С-сигнала, называемое временем подготовки (setup time), и могут снова начинаться после среза С-сигнала не ранее чем через время выдержки (удержания) (hold time).

Необходимость введения и нормирования интервалов подготовки и выдержки характерна не только для защелки, но и для всех функциональных узлов, имеющих вход синхронизации. Кроме того, для защелки, как и для любого синхронного узла, существует минимально допустимая длительность синхроимпульса, обеспечивающая отсутствие сбоев из-за наложения переходных процессов от фронта и среза этого импульса.

Для триггеров-защелок, выпускаемых в виде микросхем, временные характеристики приводятся в справочниках. Примерами выпускаемых промышленностью D-триггеров-защелок могут служить интегральные микросхемы (ИМС) К155ТМ5, К155ТМ7, К561ТМЗ, которые содержат по четыре триггера с объединенными С-входами.