- •Технічне завдання

- •Загальні відомості про серію к1810

- •Максимальний режим вм86 з кпдп вт37

- •Опис мікросхем

- •3.1 Мікропроцесор к1810вм86

- •3.2 Контролер прямого доступу до пам’ямі к1810вт37

- •3.3 Генератор тактових імпульсів к1810гф84

- •3.4 Буферні регістри к1810ир82

- •3.5 Шинні формувачі к1810ва86

- •Принципова схема мікропроцесорної системи

- •Висновок

- •Список літератури

3.3 Генератор тактових імпульсів к1810гф84

Генератор тактових імпульсів (ГТІ) К1810ГФ84 призначений для управління ЦП К1810ВМ86 і периферійними пристроями, а також для синхронізації сигналів READY з тактовими сигналами ЦП і сигналів інтерфейсної шини.

Вибір режиму функціонування визначається потенціалом на вході F/C̅. Якщо цей вхід під’єднаний до «землі», то ГТІ працює в режимі формування сигналів від внутрішнього генератора, а якщо на F/C̅ подається високий потенціал – то в режимі формування.

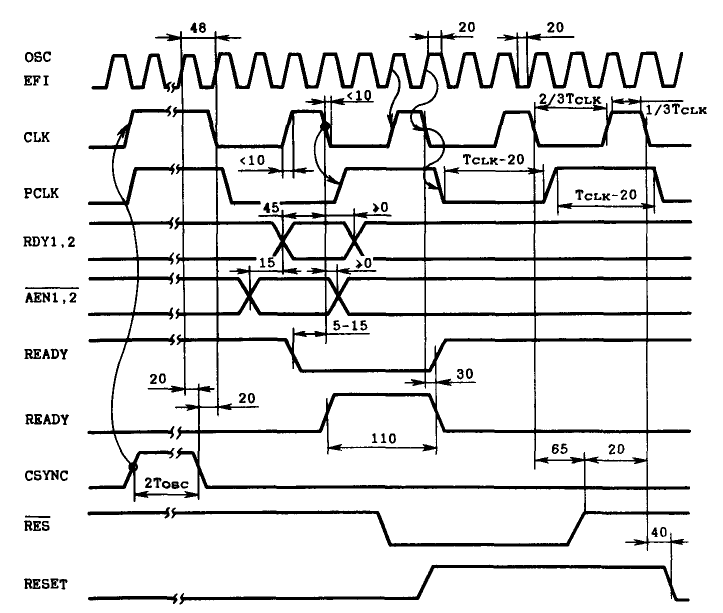

Сигнали OCS, CLK, PCLK синхронні і їх частоти пов’язані співвідношенням:

FOCS=3FCLK=6FPCLK

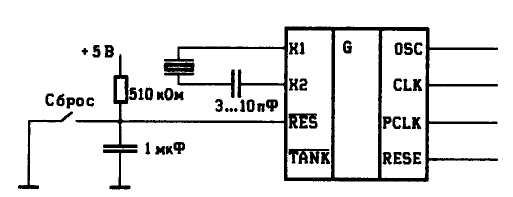

До входу R̅E̅S̅ підключається RC-ланцюг, забезпечуючи автоматичне формування сигналу при включенні джерела живлення.

Таблиця 2.3

Найменування входу/виходу |

Призначення |

CLK |

Тактовий сигнал для ЦП К1810ВМ86 |

PCLK |

Тактовий сигнал для периферійних БІС |

OCS |

Тактовий сигнал задаючого генератора |

RESET |

Сигнал скидання |

READY |

Сигнал готовності |

X2, X1 |

Входи для кварцового резонатора |

EFI |

Для зовнішнього джерела частоти |

F/C̅ |

Вибір джерела тактової частоти |

R̅E̅S̅ |

Сигнал початкового встановлення |

RDY1, RDY2 |

Сигнал готовності від 2 систем И-41 |

A̅E̅N̅1̅, A̅E̅N̅2̅ |

Сигнали доступу до адреси по відношенню до сигналів готовності RDY1, RDY2 |

CSYNC |

Вхід синхронізації для тактової частоти декількох БІС |

TANK |

Для кристалу з обертоном |

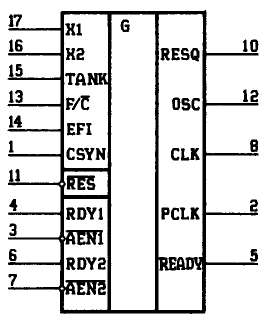

Рис. 6.

Умовно графічне зображення К1810ГФ84

Рис. 7. Схема підключення ГТІ до кварцового резонатора.

Рис. 8. Часова діаграма роботи ГТІ К1810ГФ84

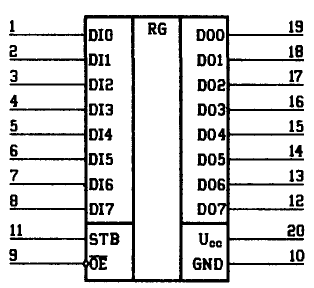

3.4 Буферні регістри к1810ир82

Буферні регістри призначені для організації запам’ятовуючих буферів, адресних засувок, портів вводу/виводу, мультиплексорів и т.д.

Регістр К1810ИР82 являє собою запам’ятовуючий пристрій, який зберігає 8 біт інформації. Серія К1810 означає, що він сумісний і має використовуватись з іншими мікросхемами серії К1810.

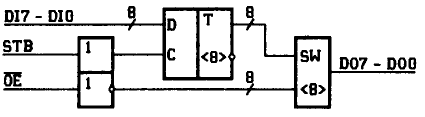

Рис. 9. Функціональна схема К1810ИР82

Таблиця 2.4

Найменування входу/виходу |

Призначення |

DI0 – DI7 |

Лінії вхідних даних |

DO0 – DO7 |

Лінії вихідних даних |

STB |

Стробуючий сигнал |

O̅E̅ |

Дозвіл видачі даних |

Ucc |

Напруга живлення |

GND |

Заземлення |

Рис. 10. Умовно графічне зображення К1810ИР82

При подачі сигналу високого рівня на вхід STB стан вхідних ліній DI7-DI0 передається на вихідні лінії DO7-DO0. Запам’ятовування в інформаційних тригерах здійснюється при переході сигналу STB від високого рівня до низького(1-0). Сигнал ОЕ управляє вихідними буферами: при ОЕ=0 буфер відпирається, при ОЕ=1 він встановлюється в Z-стан. Сигнал ОЕ не впливає ні на стан інформаційних тригерів, ні на функцію запису.

Так як за варіантом розрядність адреси даних = 8 біт то необхідно використовувати 8/8 = 1 мікросхему регістрів К1810ИР82.

Рис. 11. Часова діаграма роботи К1810ИР82