- •Технічне завдання

- •Загальні відомості про серію к1810

- •Максимальний режим вм86 з кпдп вт37

- •Опис мікросхем

- •3.1 Мікропроцесор к1810вм86

- •3.2 Контролер прямого доступу до пам’ямі к1810вт37

- •3.3 Генератор тактових імпульсів к1810гф84

- •3.4 Буферні регістри к1810ир82

- •3.5 Шинні формувачі к1810ва86

- •Принципова схема мікропроцесорної системи

- •Висновок

- •Список літератури

3.2 Контролер прямого доступу до пам’ямі к1810вт37

Контролер ПДП К1810ВТ37 використовується в складі МПС, виконаних на базі МПК К580, К1810, К1821, для реалізації прямого доступу до пам’яті по чотирьом незалежним каналам з позитивним чи негативним прирощенням адреси зі швидкістю до 1,6 Мбайт/с. КПДП дозволяє реалізувати передачу пам’ять – пам’ять, має широкі можливості програмного управління і каскадування. Кожен канал може виконувати до 64К циклів ПДП і має можливість автоматичної ініціалізації, повторення циклів ПДП з такими ж самими параметрами.

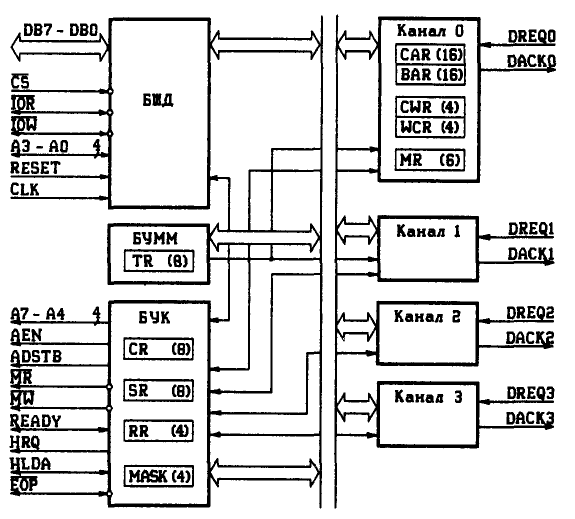

Рис. Структурна схема КПДП

Контролер включає 4 канали, кожен з яких складається із 4 16-ти розрядних регістрів.

Регістр поточної адреси CAR зберігає поточну адресу пам’яті при виконанні циклу ПДП. Після виконання циклу ПДП склад цього регістру збільшується чи зменшується на одиницю. Воно може бути прочитано чи загружено за допомогою двох команд вводу-виводу.

Регістр циклів ПДП CWR зберігає число слів, що назначені для передачі. При загрузці цього регстру необхідно пам’ятати, що завантажувальна константа повинна бути на одиницю больше числа слів, необхідних для передачі. При виконанні регістр працює у режимі віднімаючого лічильника.

Регістр зберігання початкової адреси BAR і регістр зберігання базового числа циклів ПДП WCR зберігає базові значення адреси і числа циклів ПДП, участують у авто ініціалізації.

КПДП включає 3 функціональні блоки, котрі виконують функції управління. Буфер шини даних необхідний для синхронізації КПДП з ЦП. Блок управління контролером при передачі у пам’ять-пам’ять включає один 8-ми розрядний регістр TR тимчасового зберігання даних, забезпечуючих зберігання байту в циклі передачі пам’ять-пам’ять на час зміни адреси. Блок управління ПДП виробляє необхідні сигнали управління при передачі даних в циклах ПДП.

Регістр команд CR визначає основні параметри роботи каналу. Завантаження здійснюється командою виводу від ЦП, а скидання – по сигналу RESET чи команді загального скидання.

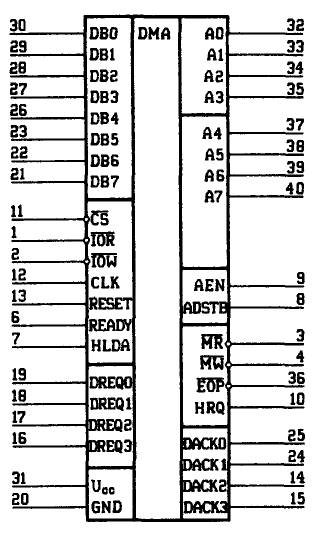

Рис. 5. Умовно графічне зображення К1810ВТ37

Таблиця 2.2

Найменування входу/виходу |

Призначення |

CLK |

Вхід для підключення тактового генератора |

CS |

Вибір кристалу |

RESET |

Скидання |

READY |

Готовність |

HLDA |

Підтвердження захвату. Вхідний сигнал для повідомлень КПДП про можливість виконання циклів ПДП |

DREQ3-DREQ0 |

Входи запросів на ПВП від зовнішніх пристроїв. |

DB7-DB0 |

Двонаправленя шина даних з буфером, має Z стан |

IOR |

Читання. Використовується ЦП для читання внутрішніх регістрів КПДП |

IOW |

Запис. Використовується ЦП для загрузки даних в регістри КПДП |

EOP |

Закінчення процесу. Вхід/вихід |

A3-A0 |

Адресні входи/виходи. Використовуються в роботи з ЦП і для адресації до каналів і регістрів каналів ПДП |

A7-A4 |

Адресні виходи, на котрі в режимі ПДП передаються відповідні розряди адреси ОЗУ. |

HRQ |

Вихід запросу захвату на управління системною шиною. Запрос на ПДП ЦП |

DACK3-DACK0 |

Підтвердження ПДП. Вихідні лінії на котрі видаються повідомлення для ВУ про можливість виконання циклів ПДП |

AEN |

Дозвіл адреси |

ADSTB |

Строб адреси |

MEMR |

Читання з пам’яті. Вихід в режимі ПДП для управління операцією читання з пам’яті. |

MEMW |

Запис до пам’яті. Вихід в режимі ПДП для управління операцією запису в пам’ять. |

Ucc |

Шина живлення (+5В) |

GND |

Загальний |