- •Методическое пособие по теме:

- •Содержание

- •1. Введение.

- •2. Теоретическая часть.

- •2.1. Общие вопросы проектирования цифровых схем.

- •2.2. Внутренняя структура плис.

- •2.3. Основы языка описания цифровых схем vhdl.

- •2.4. Краткое описание используемой отладочной платы.

- •2.5. Краткое описание средств проектирования плис.

- •3. Практическая часть.

- •3.1. Знакомство со средой Xilinx ise WebPack. Создание проекта.

- •3.2. Реализация проекта при помощи графического редактора схем.

- •3.3. Реализация проекта при помощи языка vhdl.

- •3.4. Моделирование проекта в среде ModelSim se.

- •3.5. Конфигурирование кристалла и проверка его работы на отладочном комплекте.

- •3.6. Задание для самостоятельного выполнения.

- •4. Список литературы.

3.4. Моделирование проекта в среде ModelSim se.

Теперь перейдем к процессу отладки наших проектов. Для этого нужно создать так называемый испытательный стенд, или TestBench, суть которого в том, что он будет подавать на блок, который мы создали путём использования графического редактора или кода VHDL, определенные сигналы, позволяющие проверить его работу посредством анализа получающихся временных диаграмм.

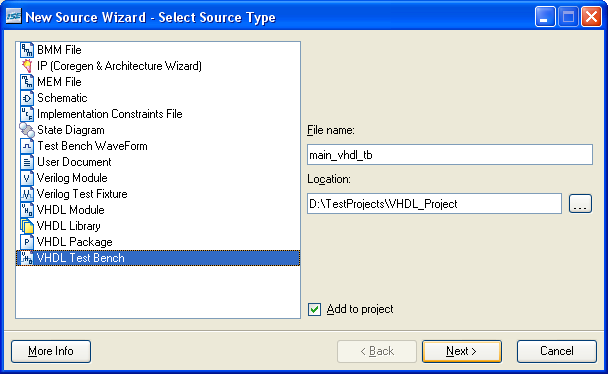

Итак, вызываем пункт меню New Source…, в появившемся диалоговом окне указываем параметры, как на рисунке 3.4.1.

Рис. 3.4.1.

Нажимаем кнопку Next, в следующем диалоговом окне будет предложено выбрать файл, к которому следует прикрепить наш испытательный стенд. Выбираем файл main_vhdl и нажимаем Next. В следующем диалоговом окне содержится краткая информация о создаваемом файле, убедившись в правильности которой нажимаем кнопку Finish.

В результате получаем файл main_vhdl_tb.vhd, с исходным кодом, который представлен в листинге 3.4.1.

Листинг 3.4.1.

--------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 15:43:38 03/06/2009

-- Design Name: main_vhdl

-- Module Name: D:/TestProjects/VHDL_Project/main_vhdl_tb.vhd

-- Project Name: VHDL_Project

-- Target Device:

-- Tool versions:

-- Description:

--

-- VHDL Test Bench Created by ISE for module: main_vhdl

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

-- Notes:

-- This testbench has been automatically generated using types std_logic and

-- std_logic_vector for the ports of the unit under test. Xilinx recommends

-- that these types always be used for the top-level I/O of a design in order

-- to guarantee that the testbench will bind correctly to the post-implementation

-- simulation model.

--------------------------------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.all;

USE ieee.numeric_std.ALL;

ENTITY main_vhdl_tb_vhd IS

END main_vhdl_tb_vhd;

ARCHITECTURE behavior OF main_vhdl_tb_vhd IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT main_vhdl

PORT(

Clock : IN std_logic;

Button : IN std_logic;

Segment_A : OUT std_logic;

Segment_B : OUT std_logic;

Segment_C : OUT std_logic;

Segment_D : OUT std_logic;

Segment_E : OUT std_logic;

Segment_F : OUT std_logic;

Segment_G : OUT std_logic

);

END COMPONENT;

--Inputs

SIGNAL Clock : std_logic := '0';

SIGNAL Button : std_logic := '0';

--Outputs

SIGNAL Segment_A : std_logic;

SIGNAL Segment_B : std_logic;

SIGNAL Segment_C : std_logic;

SIGNAL Segment_D : std_logic;

SIGNAL Segment_E : std_logic;

SIGNAL Segment_F : std_logic;

SIGNAL Segment_G : std_logic;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: main_vhdl PORT MAP(

Clock => Clock,

Button => Button,

Segment_A => Segment_A,

Segment_B => Segment_B,

Segment_C => Segment_C,

Segment_D => Segment_D,

Segment_E => Segment_E,

Segment_F => Segment_F,

Segment_G => Segment_G

);

tb : PROCESS

BEGIN

-- Wait 100 ns for global reset to finish

wait for 100 ns;

-- Place stimulus here

wait; -- will wait forever

END PROCESS;

END;

Дописываем код в соответствии с листингом 3.4.2.

Листинг 3.4.2.

…

<предыдущую часть оставляем без изменений>

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: main_vhdl PORT MAP(

Clock => Clock,

Button => Button,

Segment_A => Segment_A,

Segment_B => Segment_B,

Segment_C => Segment_C,

Segment_D => Segment_D,

Segment_E => Segment_E,

Segment_F => Segment_F,

Segment_G => Segment_G

);

Clock <= not Clock after 10 ns;

tb : PROCESS

BEGIN

-- Wait 100 ns for global reset to finish

wait for 100 ns;

Button <= '0';

wait for 500 ns;

Button <= '1';

wait for 300 ns;

Button <= '0';

wait for 700 ns;

Button <= '1';

wait for 150 ns;

Button <= '0';

wait for 400 ns;

Button <= '1';

wait for 200 ns;

Button <= '0';

wait for 600 ns;

Button <= '1';

wait for 250 ns;

wait; -- will wait forever

END PROCESS;

END;

Как можно сообразить, здесь мы задаем частоту изменения сигнала Clock (50МГц в данном случае), а также имитируем нажатия на кнопку, различные по длительности.

Теперь в окне Sources в поле Sources for: выбираем значение Behavorial Simulation. Выбираем наш испытательный стенд в окне Sources и в окне Procsesses дважды щелкаем по надписи Simulate Behavorial Model.

В результате этих действий загрузится среда ModelSim.

Установите в поле

ввода

![]() время 10000 ns,

нажмите кнопку

время 10000 ns,

нажмите кнопку

![]() (Restart),

в появившемся диалоговом окне нажмите

Restart,

затем нажмите кнопку

(Restart),

в появившемся диалоговом окне нажмите

Restart,

затем нажмите кнопку

![]() (Run).

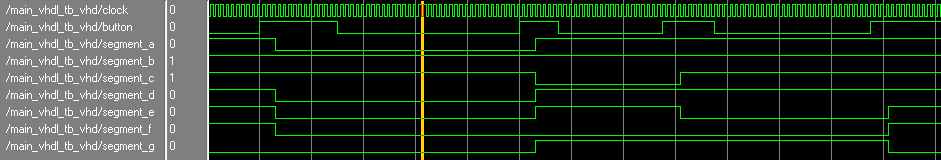

В результате Вы получите временную

диаграмму, как на рисунке 3.4.2, из которой

ясно видно работу нашего проекта.

(Run).

В результате Вы получите временную

диаграмму, как на рисунке 3.4.2, из которой

ясно видно работу нашего проекта.

Рис. 3.4.2.

Аналогичные действия следует провести и с проектом, реализованном в графическом редакторе, чтобы убедиться в совпадении его временной диаграммы с временной диаграммой проекта на VHDL.