- •Методическое пособие по теме:

- •Содержание

- •1. Введение.

- •2. Теоретическая часть.

- •2.1. Общие вопросы проектирования цифровых схем.

- •2.2. Внутренняя структура плис.

- •2.3. Основы языка описания цифровых схем vhdl.

- •2.4. Краткое описание используемой отладочной платы.

- •2.5. Краткое описание средств проектирования плис.

- •3. Практическая часть.

- •3.1. Знакомство со средой Xilinx ise WebPack. Создание проекта.

- •3.2. Реализация проекта при помощи графического редактора схем.

- •3.3. Реализация проекта при помощи языка vhdl.

- •3.4. Моделирование проекта в среде ModelSim se.

- •3.5. Конфигурирование кристалла и проверка его работы на отладочном комплекте.

- •3.6. Задание для самостоятельного выполнения.

- •4. Список литературы.

3.3. Реализация проекта при помощи языка vhdl.

В этом разделе мы реализуем проект, аналогичный по функциональности проекту предыдущего раздела, но на этот раз – с применением VHDL.

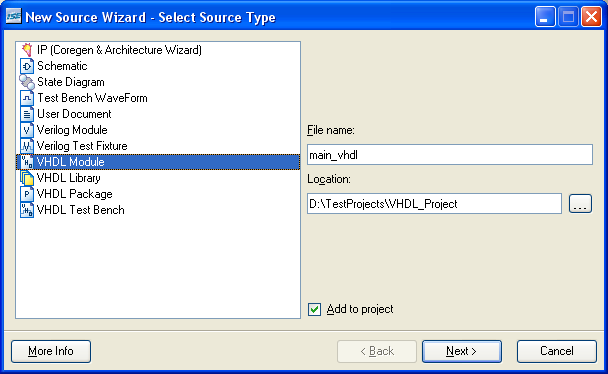

Итак, создадим второй проект, который назовем VHDL_Project. Добавим в него исходник VHDL-кода, для этого в уже известном нам диалоговом окне укажем параметры, как на рисунке 3.3.1.

Рис. 3.3.1.

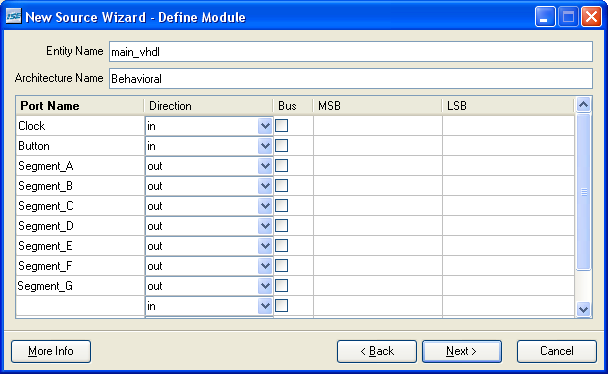

Нажимаем кнопку Next. Появляется диалоговое окно, в котором нужно указать входы и выходы создаваемого блока. Укажем их в соответствии со схемой из предыдущего раздела, см. рисунок 3.3.2.

Рис. 3.3.2.

После этого нажимаем Next и убедившись в следующем диалоговом окне с краткой информацией о создаваемом файле, что всё верно, нажимаем Finish.

В результате будет создан код, представленный на листинге 3.3.1.

Листинг 3.3.1.

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 14:55:56 03/06/2009

-- Design Name:

-- Module Name: main_vhdl - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity main_vhdl is

Port ( Clock : in STD_LOGIC;

Button : in STD_LOGIC;

Segment_A : out STD_LOGIC;

Segment_B : out STD_LOGIC;

Segment_C : out STD_LOGIC;

Segment_D : out STD_LOGIC;

Segment_E : out STD_LOGIC;

Segment_F : out STD_LOGIC;

Segment_G : out STD_LOGIC);

end main_vhdl;

architecture Behavioral of main_vhdl is

begin

end Behavioral;

Чтобы реализовать нужную нам функциональность, нужно ввести код, представленный на листинге 3.3.2. В коде даны комментарии, проводящие параллель между описанием схемы из предыдущего раздела и непосредственно самим кодом.

Листинг 3.3.2.

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 14:55:56 03/06/2009

-- Design Name:

-- Module Name: main_vhdl - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity main_vhdl is

Port ( Clock : in STD_LOGIC;

Button : in STD_LOGIC;

Segment_A : out STD_LOGIC;

Segment_B : out STD_LOGIC;

Segment_C : out STD_LOGIC;

Segment_D : out STD_LOGIC;

Segment_E : out STD_LOGIC;

Segment_F : out STD_LOGIC;

Segment_G : out STD_LOGIC);

end main_vhdl;

architecture Behavioral of main_vhdl is

signal Button_Sync: std_logic;

signal Button_Sync_NoMS: std_logic;

signal Button_Sync_NoMS_Delayed: std_logic;

signal Button_Pulse: std_logic;

signal Count: integer range 0 to 4;

signal Reset: std_logic;

signal Count_Bus: std_logic_vector (1 downto 0);

begin

-- Три D-триггера: для синхронизации, защиты от метастабильности и задержки сигнала

process (Clock)

begin

if rising_edge(Clock) then -- условие переднего фронта сигнала Clock

Button_Sync <= Button;

Button_Sync_NoMS <= Button_Sync;

Button_Sync_NoMS_Delayed <= Button_Sync_NoMS;

end if;

end process;

-- Преобразование фронта в короткий импульс

Button_Pulse <= Button_Sync_NoMS and not Button_Sync_NoMS_Delayed;

-- Двоичный счетчик

process (Clock)

begin

if (Reset = '1') then -- асинхронный сброс счетчика, здесь его нужно сделать вручную

Count <= 0;

elsif rising_edge(Clock) then

if (Button_Pulse = '1') then -- сигнал разрешения работы счетчика

Count <= Count + 1;

end if;

end if;

end process;

-- Компаратор (проверяет, досчитал ли счетчик до 3 и выдает сигнал сброса)

process (Clock)

begin

if rising_edge(Clock) then

if (Count > 3) then

Reset <= '1';

else

Reset <= '0';

end if;

end if;

end process;

-- преобразовываем переменную Count в двухразрядную шину

Count_Bus <= CONV_STD_LOGIC_VECTOR(Count, 2);

-- Семисегментный дешифратор, здесь он выполняется простым case

process (Clock)

begin

case (Count_Bus) is

when "00" =>

Segment_A <= '1';

Segment_B <= '1';

Segment_C <= '1';

Segment_D <= '1';

Segment_E <= '1';

Segment_F <= '1';

Segment_G <= '0';

when "01" =>

Segment_A <= '0';

Segment_B <= '1';

Segment_C <= '1';

Segment_D <= '0';

Segment_E <= '0';

Segment_F <= '0';

Segment_G <= '0';

when "10" =>

Segment_A <= '1';

Segment_B <= '1';

Segment_C <= '0';

Segment_D <= '1';

Segment_E <= '1';

Segment_F <= '0';

Segment_G <= '1';

when "11" =>

Segment_A <= '1';

Segment_B <= '1';

Segment_C <= '1';

Segment_D <= '1';

Segment_E <= '0';

Segment_F <= '0';

Segment_G <= '1';

when others =>

end case;

end process;

end Behavioral;