- •Методическое пособие по теме:

- •Содержание

- •1. Введение.

- •2. Теоретическая часть.

- •2.1. Общие вопросы проектирования цифровых схем.

- •2.2. Внутренняя структура плис.

- •2.3. Основы языка описания цифровых схем vhdl.

- •2.4. Краткое описание используемой отладочной платы.

- •2.5. Краткое описание средств проектирования плис.

- •3. Практическая часть.

- •3.1. Знакомство со средой Xilinx ise WebPack. Создание проекта.

- •3.2. Реализация проекта при помощи графического редактора схем.

- •3.3. Реализация проекта при помощи языка vhdl.

- •3.4. Моделирование проекта в среде ModelSim se.

- •3.5. Конфигурирование кристалла и проверка его работы на отладочном комплекте.

- •3.6. Задание для самостоятельного выполнения.

- •4. Список литературы.

2.3. Основы языка описания цифровых схем vhdl.

VHDL (VHSIC (very-high-speed-integrated-circuit) hardware description language) – специальный язык для описания высокоскоростных цифровых схем. Он отличается от всем привычных и широко используемых ныне императивных языков программирования (таких, как С++ или Pascal; далее будем называть их «обычными» языками). И основное его отличие заключается в следующем. Суть обычного языка программирования сводится к тому, что компьютер последовательно, команду за командой выполняет программу. И в каждый конкретный момент времени выполняется только одна команда (не будем сейчас рассматривать многозадачность и создание потоков, в простейшем случае – это так). И вообще говоря, это соответствует изначальной структуре всех процессоров – последовательное выполнение кода.

Но всем известно, что в цифровой схеме может одновременно, параллельно проходить несколько цепочек вычислений. Реализацию такой функциональности и даёт нам VHDL.

Чтобы понять, как реализован этот принцип, рассмотрим такой простой пример. Строки:

Net1 <= ‘0’;

Net2 <= Net1;

приведут к тому же результату, что и

Net2 <= Net1;

Net1 <= ‘0’;

а именно к тому, что двум цепям (сигналам, или просто кускам провода, если хотите), Net1 и Net2 будет присвоено значение «0», т.е. выражаясь понятиями цифровой схемотехники, логического нуля.

Здесь «<=», как нетрудно догадаться, это оператор присваивания в языке VHDL. В конце каждой команды ставится точка с запятой.

Значения сигналов пишутся в одинарных кавычках – ‘0’, ‘1’.

Значения шин – в двойных кавычках – “00001010”, X”0A”.

По умолчанию все данные представляются в двоичном коде, если же перед первой кавычкой стоит знак X – то в шестнадцатеричном.

Сами сигналы объявляются следующим образом:

signal Net1: std_logic;

signal Net2: std_logic = ‘1’;

Здесь во второй строчке сигналу присвоено значение по умолчанию, которое будет загружено в него сразу после загрузки кристалла.

Для объявления шины используется следующая конструкция:

signal Bus1: std_logic_vector (7 downto 0);

- это мы объявили 8-разрядную шину.

Помимо сигналов, можно объявлять также и всем привычные переменные целого типа, integer, которые нам также пригодятся (забегая вперед – для реализации счетчиков), к примеру:

signal Count: integer range 0 to 65535;

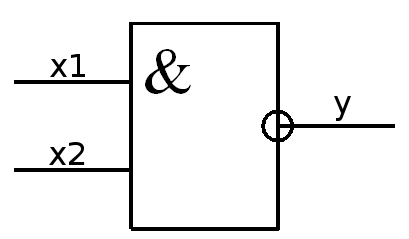

Простейшие логические операции, такие как НЕ, И, ИЛИ, исключающее ИЛИ, выполняются соответствующими ключевыми словами — not, and, or, xor, к примеру, следующая конструкция

y <= not (x1 and x2);

является аналогией такой схемы:

Рис. 2.3.1.

Еще одним важным элементом языка VHDL является процесс – он используется для описания как элементов комбинаторной, так и последовательностной логики. Выглядит он в общем случае вот так:

process (<all_input_signals_separated_by_commas>)

begin

<statements>;

end process;

Вне процессов описываются только элементы комбинаторной логики.

Есть в VHDL и оператор условия, используется внутри процесса:

if <condition> then

<statement>

elsif <condition> then

<statement>

else

<statement>

end if;

Есть и оператор CASE, также для процесса:

case (<2-bit select>) is

when "00" => <statement>;

when "01" => <statement>;

when "10" => <statement>;

when "11" => <statement>;

when others => <statement>;

end case;

У обоих последних операторов есть аналоги для использования вне процесса. Для IF:

<name> <= <expression> when <condition> else

<expression> when <condition> else

<expression>;

Для CASE:

with <choice_expression> select

<name> <= <expression> when <choices>,

<expression> when <choices>,

<expression> when others;

Всевозможные шифраторы-дешифраторы реализуются очень просто – при помощи выше описанных операторов CASE, и комбинаторных аналогов IF и CASE.

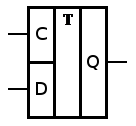

Чтобы описать простейший D-триггер, используется следующая конструкция (на рисунке 2.3.2, справа от кода, представлено соответствующее УГО элемента):

p rocess

(C)

rocess

(C)

begin

if rising_edge(C) then

Q <= D;

end if;

end process;

Рис. 2.3.2.

Описание простейшего счетчика выглядит так:

process (<clock>)

begin

if <clock>='1' and <clock>'event then

if <clock_enable>='1' then

<count> <= <count> + 1;

end if;

end if;

end process;

Все эти конструкции запоминать не обязательно, т.к. они есть в специальном «Language Templates» среды Xilinx ISE WebPACK, работу с которой мы рассмотрим далее. Помимо выше приведенных, там еще очень много всевозможных шаблонов кода на все случаи жизни.