- •1.Ассемблер 8080/85. Поясните, в каких случаях необходимо использовать перемещаемый сегмент, а в каких абсолютный?

- •11.Опишите средства документирования пп.

- •12.Перечислите из каких полей состоит ассемблерная строка?

- •13. Перечислите поля ассемблерной строки. Укажите варианты задания границ полей.

- •14. Перечислите средства документирования программ. Приведите примеры.

- •15. Почему ассемблер (в отличие от яву) называют языком низкого уровня?

- •16. Поясните, почему директивы ассемблера называют "псевдокомандами".

- •17. Укажите назначение директив db, dw, ds. В чем их сходство, отличие?

- •25. Мп 8085. Куда помещается код инструкции команды после выполнения цикла выборки?

- •26. Мп 8085. Укажите варианты изменения содержимого регистра sp при использовании стековых команд

- •27. Отметьте положительные и отрицательные стороны косвенного метода адресации.

- •28. Перечислите методы адресации данных и переходов.

- •29. Перечислите методы адресации, используемые в системе команд мп 8080/85.

- •30. Почему мп 8080 называются 8-разрядными.

- •32. Укажите формат (размер в байтах), который используют команды условного перехода. Опишите назначение каждого байта.

- •33. Укажите форматы команд, используемые при прямой адресации.

- •34. В чём заключается отличие в мп8080/85 непосредственной адресации операндов от прямой?

- •36. Вывод программный с квитированием. Как мп узнаёт, что данные приёмником информации приняты?

- •37. Дайте определение понятию интерфейс. Приведите примеры интерфейсов.

- •38. Для чего используется регистр статуса, имеющийся в увв с квитированием?

- •39. Какие пины мп 8080/85 используется для Ввода/Вывода по готовности?

- •40. Перечислите сигналы, которые связывают источник и приемник информации, если между ними используется передача данных (Вывод) с квитированием?

- •41. Перечислите три основных метода обмена информацией в микропроцессорных системах. Приведите примеры применения.

- •42 Пины Ready, Wait мп 8080/85 используются для Ввода/Вывода по готовности. Какой из этих пинов вход, а какойвыход? Что генерирует сигнал готовности?

- •43 Поясните, почему связывают время доступа к памяти с вводом по готовности.

- •44 Прибор памяти имеет время доступа большее, чем это допускает мп 8085. Что необходимо предпринять для

- •46 Укажите варианты использования Ввода/Вывода по готовности.

- •47 Укажите области использования Ввода/Вывода по готовности.

- •48 Укажите, как согласуется скорость современных мп со скоростью основной память?

- •49 Укажите, какого типа регистры входят в состав увв.Мп 8080/85

- •51 Дайте определение понятию цикл команды (мп 8080/85).

- •76 Какие требования предъявляются к пинам управления прибора памяти, подключаемого в шине данных?

- •78 Перечислите основные технологические различия приборов памяти типа ram.

- •79 Перечислите отличия прибора памяти 8185 (1kB) от приборов памяти общего назначения такого же размера.

- •81 Укажите возможности расширения памяти мп системы на мп 8085.

- •82 Укажите максимальный размер памяти типа ram, которую можно подключить к такому мп?

- •83 Для питания периферийных приборов стандарта rs-232 используются не ttl напряжения. Укажите, какие?

- •84 Зависит ли в стандарте rs-232 скорость передачи информации от длины соединения? Почему?

- •86 На какие части последовательного интерфейса распространяется стандарт rs-232?

- •87 Объясните наивысшую скорость передачи информации стандарта rs-422 по сравнению с остальными, изученными в курсе.

- •88 Объясните широкую распространенность последовательного интерфейса (rs-232, rs-485, rs-422, rs-423, usb,ieee 1394 и др.) по сравнению с параллельным (Centronics).

- •89 Перечислите варианты последовательной передачи данных. Укажите различие в синхронных и асинхронных вариантах.

- •91. Поясните отличия синхронной и асинхронной последовательной линии передачи данных?

- •92. Поясните понятия: дуплексный, полудуплексный, симплексный в последовательных каналах связи.

- •93 Поясните различия в организации среды распространения сигнала (количество проводов, дополнительные ис и др.) в стандартах rs-422 и rs-485.

- •94 Поясните, какой из последовательных интерфейсов называется 4-х проводным?

- •95. Проводная линия связи по стандарту Rs-232. Чем отличается прибор dte от прибора dce.

- •96 Расположите в порядке повышения быстродействия приборы, реализующие стандарт последовательной передачи информации rs-232, rs-485, rs-422, rs-423.

- •97 Укажите, к какому типу последовательной передачи данных относятся интерфейсы spi и i2c?

- •98 Что такое модем? Для чего он используется в проводных линиях связи?

- •109.Поясните, в чем заключается широкое распространение Ввода/Вывода по прерыванию?

- •110.Укажите на различия в прерываниях rst7.5 и rst6.5, rst5.5.

- •111.Укажите назначения входа прерывания trap.

- •112.Укажите различия в функционировании мп при обработке прерывания в отличие от подпрограммы.

- •113.Что такое контроллер прерывания, встроенный в мп 8085?

- •114.Что такое приоритет прерывания в мп8085?

- •160. То такое параметр в пп? Какие варианты передачи параметров Вы знаете?

- •161. Все регистры таймера 8253 имеют формат 8 разрядов. Как производится программирование 16-разрядных счетчиков-таймеров?

- •189. Укажите назначение селектора адреса в микропроцессорных системах. Приведите примеры реализации.

- •190. Укажите состав и разрядность системной шины.

- •192. Как подключаются цап с 10 и 12-ю разрядами к 8-разрядной шине данных?

- •193. Как различаются цап по типу загрузки кода?

- •195. Опишите основные принципы построения многоканальных ацп (на примере aDuC812).

- •196. Опишите основные сигналы системной шины, которые используются для подключения adc к микропроцессору.

- •197. Перечислите основные принципы преобразования аналоговой величины в цифровой код.

- •199. Сравните по быстродействию медоды поразрядного взвешивания и последовательного приближения.

- •200. Укажите назначение сигналов clk и eoc в adc.

- •201. Укажите назначение сигналов clk и start в adс.

- •202.Укажите различия в построении последовательных и параллельных цап.

- •203. Укажите, случаи предпочтительного использование внешнего и внутреннего тактового генератора.

- •205. Чем отличается метод последовательного приближения от поразрядного взвешивания в ацп?

- •206. Что такое опорное напряжение? Как оно используется в цап?

- •207. Что такое цифровые потенциометры?

- •208. Перечислите основные моменты описания подпрограмм (процедур*).(???)

- •209. Перечислите основные элементы структурного программирования

- •216. Структура данных, что это такой? Приведите пример.

- •221. Укажите различия в циклах типа "До" и "Пока".

- •222. Укажите, чем отличается структура обход от структуры ветвление?

189. Укажите назначение селектора адреса в микропроцессорных системах. Приведите примеры реализации.

Селектор адреса предназначен для применения в микропроцессорной системе с унифицированным интерфейсом и осуществляет выбор регистра внешнего устройства, управление чтением регистра внешнего устройства, управление записью в регистр внешнего устройства слова, младшего и старшего байтов.

190. Укажите состав и разрядность системной шины.

Системная шина процессора предназначена для обмена информацией микропроцессора с любыми внутренними устройствами микропроцессорной системы (контроллера или компьютера).

В состав системной шины в зависимости от типа процессора входит одна или несколько шин адреса, одна или несколько шин данных и шина управления. Несколько шин данных и адреса применяется для увеличения производительности процессора и используется только в сигнальных процессорах. В универсальных процессорах и контроллерах обычно применяется одна шина адреса и одна шина данных.

Адресное

пространство микропроцессорного

устройства изображается графически

прямоугольником, одна из сторон которого

представляет разрядность адресуемой

ячейки этого микропроцессора, а другая

сторона - весь диапазон доступных адресов

для этого же микропроцессора. Обычно в

качестве минимально адресуемой ячейки

памяти выбирается восьмиразрядная

ячейка памяти (байт). Диапазон доступных

адресов микропроцессора определяется

разрядностью шины адреса системной

шины. При этом минимальный номер ячейки

памяти (адрес) будет равен 0, а максимальный

определяется из формулы:

![]()

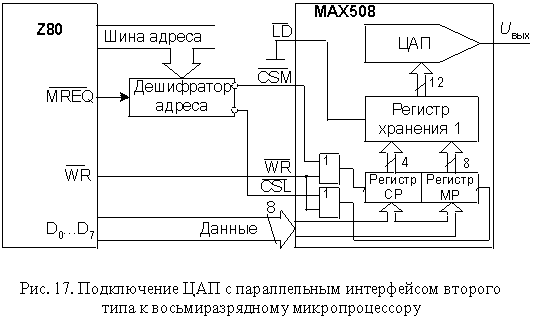

192. Как подключаются цап с 10 и 12-ю разрядами к 8-разрядной шине данных?

Для

подключения многоразрядных ЦАП к

восьмиразрядным микропроцессорам и

микроконтроллерам используется второй

вариант параллельного интерфейса. Он

предусматривает наличие двух параллельных

загрузочных регистров для приема

младшего байта входного слова МБ и

старшего байта – СБ. Пересылка байтов

входного слова в загрузочные регистры

может происходить в любой последовательности.

193. Как различаются цап по типу загрузки кода?

ЦАП без триггера или с одним триггером должен быть заполнен сразу по всем разрядам, так как иначе его выходной сигнал в течение загрузки может сильно отличаться от тех значений, которые были до преобразования и появятся после преобразования. С другой стороны, ЦАП с двойной буферизацией может быть загружен параллельными данными, последовательными данными, 4-разрядными или 8-разрядными словами или чем-то подобным, и выход его остается неизменным до тех пор, пока новые данные полностью не загрузятся, и на ЦАП не поступит команда модификации выходных данных.

195. Опишите основные принципы построения многоканальных ацп (на примере aDuC812).

Микропроцессорный стенд SDK-1 построен на базе однокристального микроконтроллера фирмы Analog Device типа ADuC812 (вычислительное ядро x51). Стенд имеет в своем составе разнообразные устройства, предназначенные для ввода, обработки и вывода информации в цифровом и аналоговом виде:

8-ми канальный аналого-цифровой преобразователь;

2-х канальный цифроаналоговый преобразователь;

устройства ввода и отображения информации (матричная клавиатура 4?4 клавиши, текстовый жидкокристаллический дисплей, пьезокерамический акустический излучатель, набор сигнальных светодиодов и переключателей);

параллельный 16-разрядный порт;

часы/календарь реального времени;

электрически стираемое программируемое ПЗУ (EEPROM) на кристалле микроконтроллера ADuC812 (640 байт);

внешнее EEPROM ёмкостью 128 байт.