- •Росжелдор

- •Лабораторная работа. Исследование функциональных узлов миус. Цифро-аналоговые преобразователи

- •Цель работы Изучить принцип формирования аналоговых сигналов в микропроцессорных системах, познакомиться с работой цап.

- •Общие сведения

- •Подготовка к работе

- •Выполнение работы

- •Содержание отчета

- •Предварительные расчеты и результаты дискретизации заданных сигналов.

- •1. Цель работы

- •2. Общие сведения

- •2.1. Память программ

- •2.2. Память данных

- •2.3. Программная модель микроконтроллеров семейства Intel 8051

- •2.4 Система команд микроконтроллеров семейства Intel 8051

- •2.4.1. Правила записи программ на языке ассемблера

- •2.4.2. Режимы адресации данных

- •2.4.3. Общая характеристика системы команд

- •2.4.4. Директивы ассемблера

- •3. Подготовка к работе

- •4. Выполнение работы

- •5. Содержание отчета

- •Формат регистра рsw

- •Формат регистра pcon

- •Формат регистра tcon

- •Формат регистра ie

- •Формат регистра ip

- •Лабораторная работа. ИнтЕгрированная среда разработки

- •1. Цель работы

- •2. Общие сведения

- •2.1. Этапы подготовки программного обеспечения микропроцессорных систем

- •2.2. Общая характеристика программы Keil mVision ide

- •2.3 Интерфейс пользователя и общие правила работы

- •3. Подготовка к работе

- •4. Выполнение работы

- •4.1. Создание нового проекта

- •4.2. Создание исходного текстового файла

- •Добавление файла в рабочую группу

- •Компиляция и компоновка проекта

- •Отладка проекта

- •5. Содержание отчета

- •Инструменты отладчика

Содержание отчета

Предварительные расчеты и результаты дискретизации заданных сигналов.

Схема исследования преобразования сигналов.

Временные диаграммы полученных сигналов.

Лабораторная работа программная модель и система команд

микроконтроллеров семейства Intel 8051

1. Цель работы

Изучить организацию памяти и программную модель, познакомиться с системой команд однокристальных микроконтроллеров семейства Intel 8051.

2. Общие сведения

Микроконтроллеры семейства Intel 8051 имеют несколько адресных пространств, функционально и логически разделенных за счет реализации различных алгоритмов адресации и сигналов управления. К ним относятся:

- внешняя память программ (ВПП),

- резидентная память программ (РПП),

- внешняя память данных (ВПД),

- резидентная память данных (РПД).

2.1. Память программ

Память программ предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных переменных и т.п. Резидентная память программ может быть дополнена внешней памятью. В этом случае общий максимально допустимый объем памяти программ составляет 64 Кбайта. Организация памяти программ базовой модели микроконтроллера семейства Intel 8051 представлена на рисунке 1 а.

При обращении к внешней памяти программ микроконтроллеры семейства Intel 8051 всегда используют полный шестнадцатиразрядный адрес, что обеспечивает доступ к 64 Кбайтам адресного пространства внешней памяти программ.

а) б)

Рисунок 1 - Организация памяти программ базового микроконтроллера Intel 8051

Обращение

к ВПП сопровождается сигналом чтения

внешней памяти программ

![]() (Program

Store

Enable)

и производится в двух случаях:

(Program

Store

Enable)

и производится в двух случаях:

1. Когда сигнал

![]() (External Access

enable) активен,

т.е. имеет уровень логического нуля.

Микроконтроллер в этом случае выполняет

программу, начиная с нулевого адреса

ВПП.

(External Access

enable) активен,

т.е. имеет уровень логического нуля.

Микроконтроллер в этом случае выполняет

программу, начиная с нулевого адреса

ВПП.

2. Когда сигнал имеет уровень логической единицы, а программный счетчик содержит число больше 0FFFh. Микроконтроллер, выбрав все команды из внутренней памяти программ, продолжает выполнять программу из внешней.

Резидентная

память программ

адресуется при помощи регистра счетчика

команд PC

(Programs

Counter).

Младшие адреса резидентной памяти

программ отведены под обработку

прерываний (рисунок 1 б). Система прерываний

микроконтроллера Intel

8051 состоит из пяти источников прерываний:

двух внешних

![]() и

и

![]() ,

двух прерываний от таймеров/счетчиков

T/C0

и T/C1

и прерывания от приемника RI

или передатчика TI

последовательного порта.

,

двух прерываний от таймеров/счетчиков

T/C0

и T/C1

и прерывания от приемника RI

или передатчика TI

последовательного порта.

В случае возникновения какого-либо прерывания происходит обращение к соответствующей ячейке резидентной памяти программ – вектору прерывания (например, при возникновении прерывания от таймера Т0 в регистр PC записывается адрес 000Вh).

Современные модифицированные серии микроконтроллеров семейства Intel 8051имеют до 15 источников прерываний, вектора которых размещаются в резидентной памяти программ, начиная с адреса 03h, через каждые восемь байт.

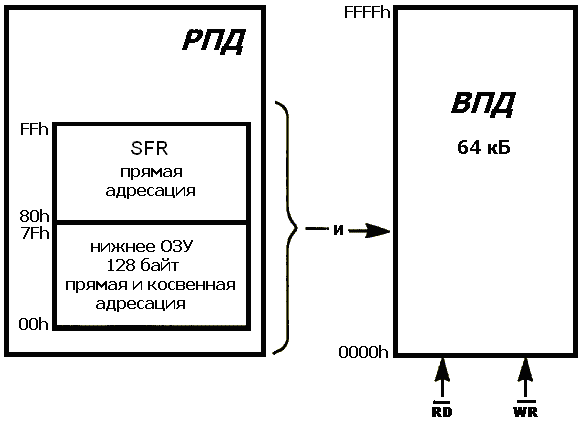

2.2. Память данных

Объем внешней

памяти данных может достигать 64

Кбайта. Для обращения к внешней памяти

данных используется косвенная адресация

с помощью восьмиразрядных регистров

R0 и R1 или с помощью

шестнадцатиразрядного регистра-указателя

DPTR. Обращение к внешней памяти

данных сопровождается стробирующими

сигналами чтения

![]() и записи

и записи

![]() .

Резидентная память данных

адресуется одним байтом и предназначена

для хранения переменных в процессе

выполнения прикладной программы.

Организация памяти данных приведена

на рисунке 2.

.

Резидентная память данных

адресуется одним байтом и предназначена

для хранения переменных в процессе

выполнения прикладной программы.

Организация памяти данных приведена

на рисунке 2.

Рисунок 2 - Организация памяти данных базового микроконтроллера Intel 8051

В нижней зоне РПД выделяют несколько специализированных областей. Первые 32 байта памяти с адреса 00h по 1Fh организованы в четыре банка регистров общего назначения, обозначаемых соответственно Банк 0 – Банк 3. Каждый банк состоит из восьми регистров R0-R7.

В любой момент программе доступен только один банк регистров общего назначения. Переключение банков производится при помощи регистра слова состояния программы PSW (Program Status Word).

Следующие 16 байт памяти с адреса 20h по 2Fh представляют собой побитно адресуемую область. Она предоставляет возможность обращения к 128 битам ячеек памяти при помощи специальных битовых команд.

Рисунок 3 - Структура нижнего ОЗУ микроконтроллеров семейства Intel 8051

С адресным пространством резидентной памяти данных граничит адресное пространство блока регистров специальных функций (РСФ). Эта область памяти в диапазоне адресов с 80h по FFh адресуется только прямо и заполнена не полностью. Количество используемых ячеек памяти соответствует количеству регистров специальных функций конкретного типа микроконтроллера. Незанятые ячейки блока РСФ физически отсутствуют, при обращении к ним читается код команды возврата.