- •Форматы и структура команд микропроцессора к580.

- •Способы адресации микропроцессора к580. Примеры ассемблерных команд Способы адресации:

- •Способы выбора адресов зу и портов ввода вывода микропроцессорной системы на базе к580.

- •Способы обмена информацией мп с зу и устройствами ввода-вывода. Сравнительная оценка способов обмена.

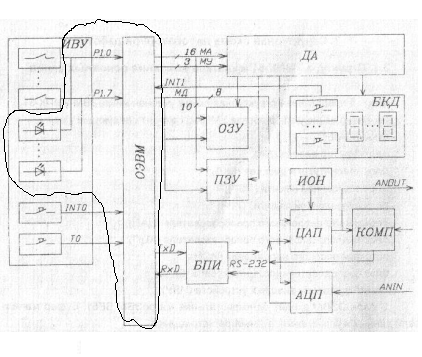

- •Разобрать фрагмент программы обмена информации мп с внешними устройствами. Тип микропроцессора определяет студент. Дать структурную схему.

- •Проектирование вычислительных систем на базе мпк кр580 (проектирование цп, схемы подключения зу и внешних устройств).

- •3)Устройства ввода/вывода

- •Разобрать фрагмент программы с использованием асинхронно-программного обмена информацией. Тип микропроцессора определяет студент. Дать структурную схему.

- •Методы преобразования десятичных чисел в двоичный, восьмеричный и шестнадцатеричный код.

- •Методы преобразования двоичных, восьмеричных и шестнадцатеричных чисел в десятичные.

- •Пример организации дешифрации адресов внешних устройств и микросхем памяти. Понятие о раздельной и совместной картах адресации.

- •15. Разработать мпс пуска асинхронного двигателя с фазным ротором в две ступени в функции скорости. Датчик скорости аналоговый.

- •16. Методы адресации микроконтроллера 1816ве51. Примеры ассемблерных команд.

- •17. Составить фрагмент программы считывания информации с ацп для контроллера 1816ве51 (Адреса: пуск - 8300н, готов – 8200н, выход данных – 8000н).

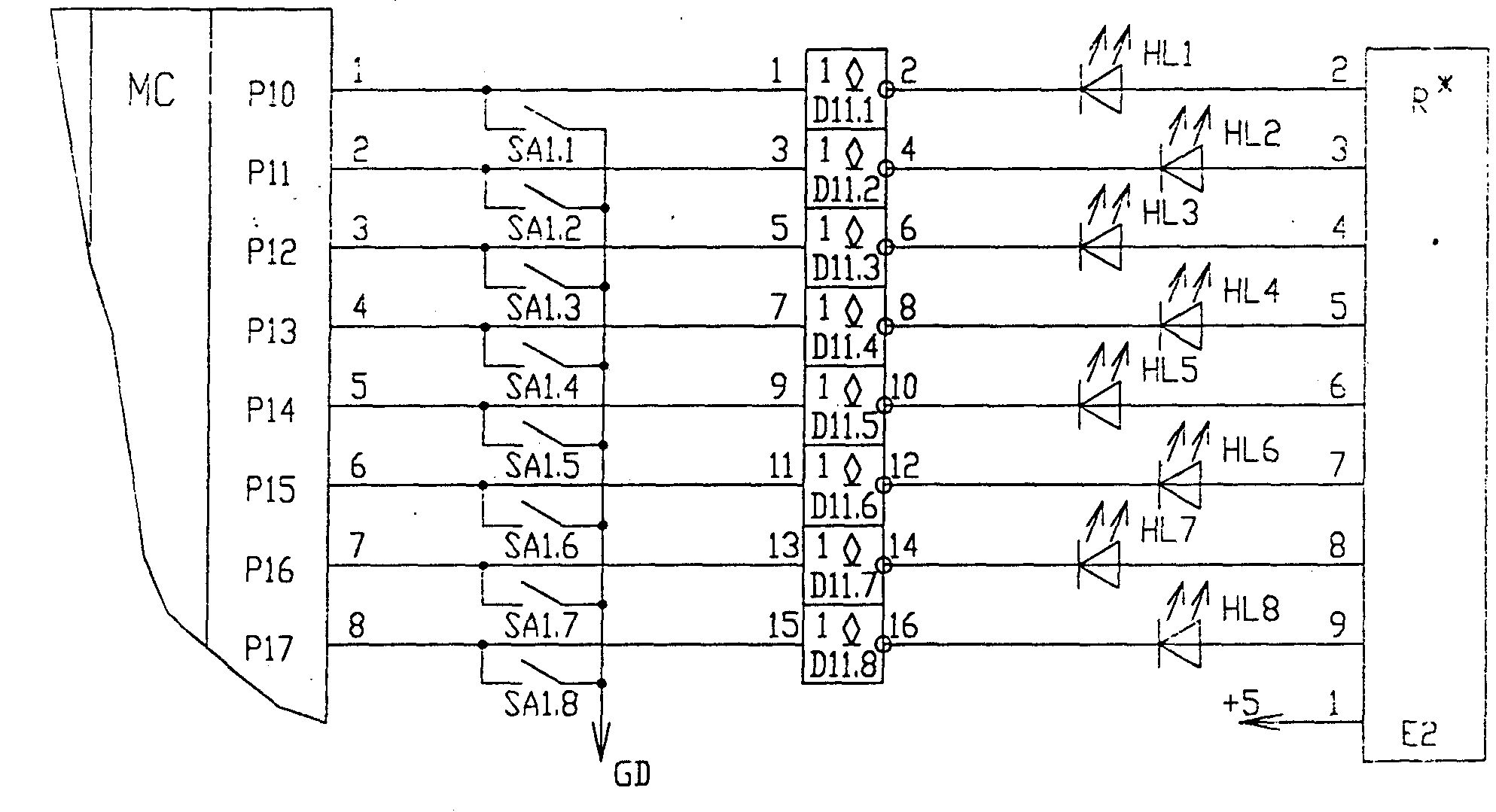

- •18. Составить подпрограмму «бегущего огня» на микроконтроллере 1816ве51. Дать структурную схему. Выдержка времени аппаратная.

- •19. Составить подпрограмму потетрадного свечения светодиодов схемы, построенной на мк1816ве51. Дать структурную схему мп - схемы.

- •23. Разработать функциональную схему мп – системы сбора четырех аналоговых сигналов. Составить программу. Тип контроллера выбирает студент.

- •24. Система прерывания микроконтроллера семейства мк51. Вектор прерываний. Прерывание от внешних событий. Пример управления программой кнопки “Пуск” в режиме прерывания.

- •25. Система таймеров мк семейства мк-51. Режимы работы таймеров. Организация выдержки времени. Пример.

18. Составить подпрограмму «бегущего огня» на микроконтроллере 1816ве51. Дать структурную схему. Выдержка времени аппаратная.

Метка |

Команды на языке ассемблера |

Коментарий |

|

ORG 1000H |

|

|

EQU STOP,02F3H |

|

|

||

|

MOV 089H,#02H |

Инициальзация таймера 0 |

|

MOV 0A8H,#82H |

|

|

MOV 8AH,#05H |

|

|

MOV 8CH,#05H |

|

|

MOV 90H,# FFH |

FFH->P1 |

|

|

01->A |

|

MOV A,#01H |

|

|

MOV R6,#40H |

Запись в регистры числа определяющего ВРЕМЕННую выдержку. |

|

MOV R7,#1FH |

|

|

MOV 2EH,R6 |

|

|

MOV 2FH,R7 |

|

|

MOV 90H,#00H |

Отключение питания индикаторов |

|

SETB 08CH |

Включение таймера |

J00: |

SJMP J00 |

Бесконечный цикл |

|

||

J9: |

DJNZ 2EH,J10 |

Выдержка времени |

|

DJNZ 2FH,J10 |

|

|

RL A |

Сдвиг влево содержимого аккумулятора |

|

MOV 90H,A |

Высвечивание содержимого аккумулятора |

|

MOV 2EH,R6 |

Восстановление содержимого ячеек , для последующей выдержки времени |

|

MOV 2FH,R7 |

|

J10: |

RETI |

Выход из подпрограммы прерывания |

|

ORG 1753H |

Вектор прерывания по таймеру 0 |

|

LJMP J9 |

Переход на подпрограмму прерывания |

19. Составить подпрограмму потетрадного свечения светодиодов схемы, построенной на мк1816ве51. Дать структурную схему мп - схемы.

Метка |

Команды на языке ассемблера |

Коментарий |

|

ORG 1000H |

|

|

EQU STOP,02F3H |

|

|

||

|

MOV 089H,#02H |

Инициальзация таймера 0 |

|

MOV 0A8H,#82H |

|

|

MOV 8AH,#05H |

|

|

MOV 8CH,#05H |

|

|

MOV 90H,# FFH |

FFH->P1 |

|

|

00001111->A |

|

MOV A,#0FH |

|

|

MOV R6,#40H |

Запись в регистры числа определяющего ВРЕМЕННую выдержку. |

|

MOV R7,#1FH |

|

|

MOV 2EH,R6 |

|

|

MOV 2FH,R7 |

|

|

MOV 90H,#00H |

Отключение питания индикаторов |

|

SETB 08CH |

Включение таймера |

J00: |

SJMP J00 |

Бесконечный цикл |

|

||

J9: |

DJNZ 2EH,J10 |

Выдержка времени |

|

DJNZ 2FH,J10 |

|

|

RL A, RL A, RL A, RL A |

Сдвиг влево содержимого аккумулятора |

|

MOV 90H,A |

Высвечивание содержимого аккумулятора |

|

MOV 2EH,R6 |

Восстановление содержимого ячеек , для последующей выдержки времени |

|

MOV 2FH,R7 |

|

J10: |

RETI |

Выход из подпрограммы прерывания |

|

ORG 1753H |

Вектор прерывания по таймеру 0 |

|

LJMP J9 |

Переход на подпрограмму прерывания |

20. Подключите к системной магистрали МП - системы, построенной на МК 1816ВЕ51, микросхему памяти. Определите диапазон адресов, в котором лежит микросхема. Считайте информацию из любой ячейки микросхемы в аккумулятор.

Если объема внутренней памяти недостаточно, используется режим работы с внешней памятью. При этом встроенное ПЗУ может либо включаться, либо не включаться в адресное пространство в зависимости от состояния вывода ЕА ВЕ51 (при подаче на ЕА нулевого потенциала ВЕ51 устанавливается в режим работы только с внешней памятью). При этом порты Р0 и Р2 используются для обеспечения обмена с внешней памятью (это

относится как к внешней памяти программ, так и к внешней памяти данных):

при обращении к внешней памяти через порт Р2 выводится старший байт адреса ячейки внешней памяти и удерживается в течении всего цикла обращения, через порт РО вначале цикла обращения выводится младший байт адреса, который стробируется сигналом ALE, затем через порт РО производится обмен данными.

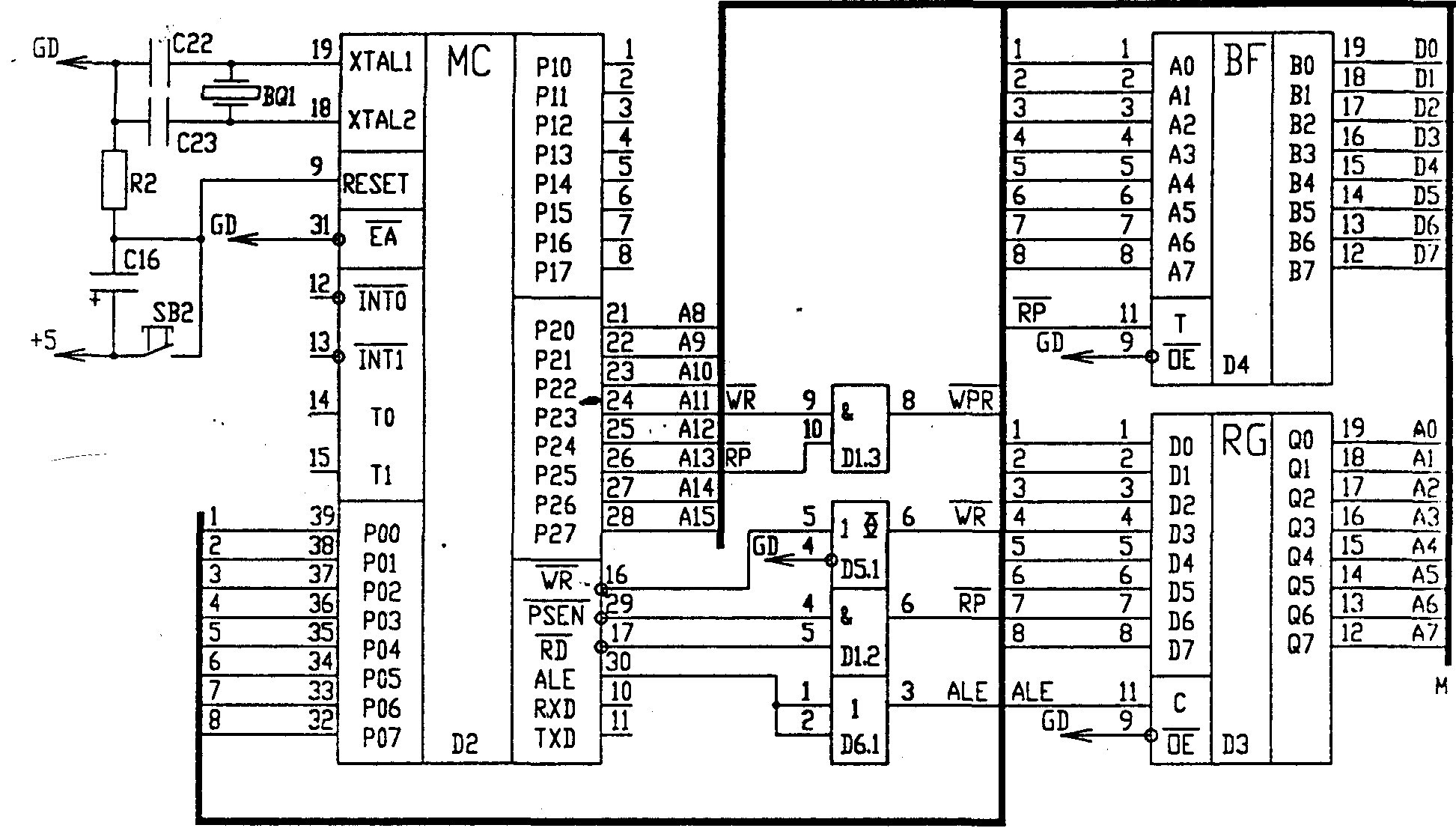

Рассмотрим схему подключения внешней памяти к ВЕ51 на примере УМПК—51, которую удобно разделить на две части. Первая из них, приведенная на рис. 11, представляет собой стандартное "ядро" устройства на базе ВЕ51 при работе с внешней памятью. Вторая часть схемы, показанная на рис. 12, представляет собой один из вариантов подключения статического ОЗУ : ПЗУ к схеме, представленной на рис.11.

Тактовая частота работы ВЕ51 задается кварцевым резонатором BQ1 и составляет в УМПК—51 6 МГц. Начальная установка осуществляется нажатием на клавишу SB2 ("R"), а также при включении питания с помощью цепи R2, С 16. Буфер данных D4 служит для организации внутренней магистрали данных УМПК—51. Буфер переключается на ввод информации сигналом RP/, представляющим собой логическое "И" сигналов чтения памяти команд PSEN/ и чтения памяти данных RD/, и, таким образом, переключается на ввод данных при чтении из совмещенной внешней памяти команд и данных. Регистр адреса D3 защелкивает младший байт адреса по сигналу ALE. Сумма сигналов PSEN/, RD/ и WR/ (WPR/) предназначена для стробирования схем дешифрации адреса с целью исключения ложных выборок при сменах адресов.

Рис. 11. Ядро системы на базе ВЕ51 в режиме работы с внешней памятью.

Сигналы магистралей адреса (А0...А7), данных (D0...D7), и управления (WR/, RP/, WPR/), формируемые схемой, представленной на рис. 11, и объединенные в шину М, будут использоваться в некоторых схемах, приведенных ниже, в этом случае подразумевается использование всей схемы, представленной на рис. 11.

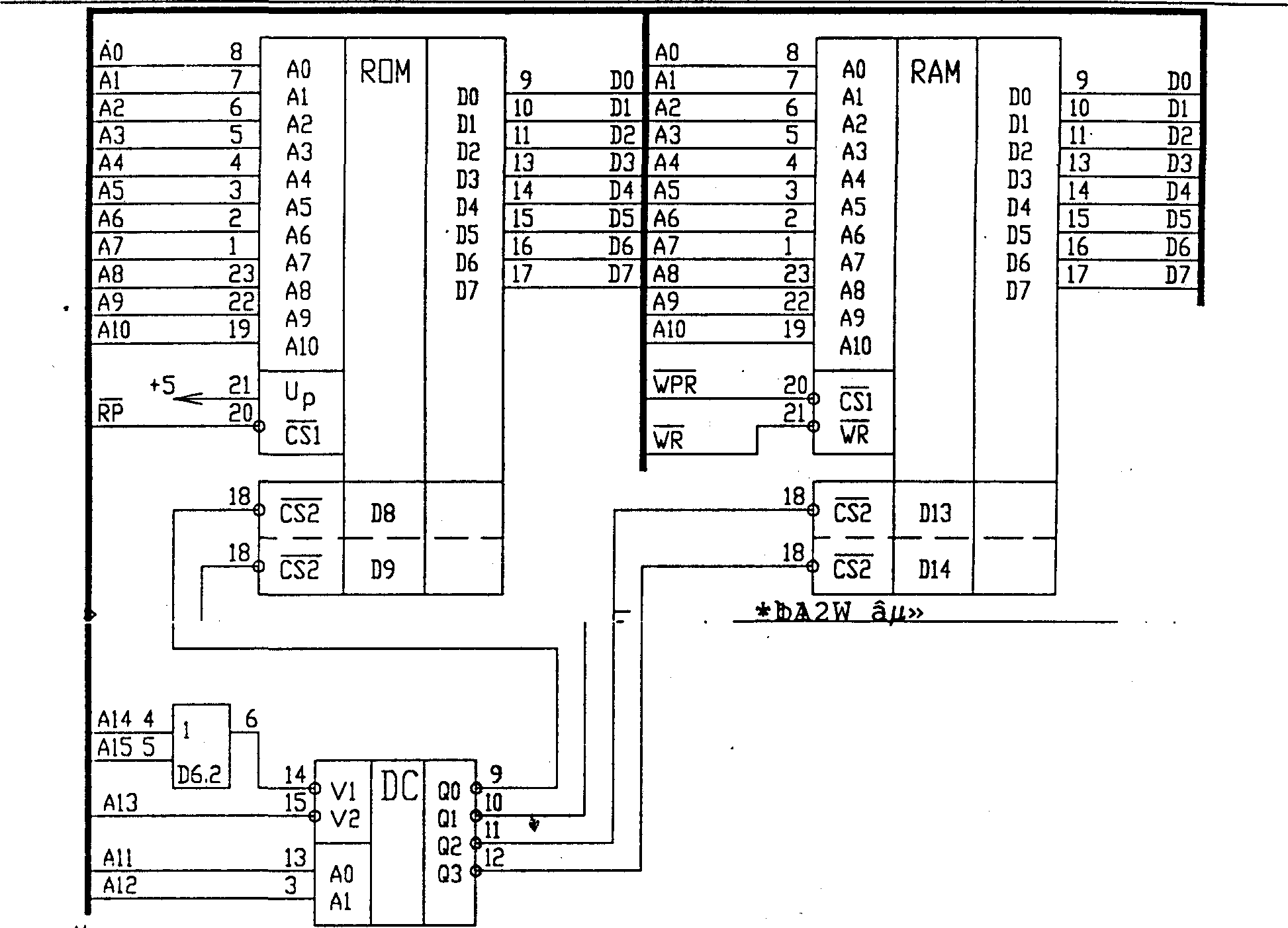

Схема подключения внешней памяти представлена на рис. 12. Блок постоянной памяти реализован на двух ПИЗУ с УФ стиранием типа К573РФ2 объемом по 2 кбайт (D8, D9), одна из которых содержит управляющую программу— монитор УМПК—51, вторая может быть использована для записи программ пользователя. Дешифратор адреса (D6.2, D10) формирует выборку для D8 при чтении команд или данных по адресам 0000...07FFH и для D9 при чтении по адресам 0800...0FFFH внешней памяти. Оперативная память содержит две ИС статического ОЗУ КР537РУ8 объемом по 2 кбайт (D13, D14). Дешифратор адреса формирует выборки для D13 и D14 при обращении к адресам 1000...17FFH и 1800...1FFFH внешнем памяти, соответственно.

Рис. 12. Подключение внешней памяти к ВЕ51.

СчитЫВАНИЕ информацию из ячейки микросхемы 0000H в аккумулятор.

МОV DPTR,#0000H

MOVX A,@DPTR

21. Подключите к системной магистрали МП – системы, построенной на МП К580, микросхему памяти. Определите диапазон адресов, в котором лежит микросхема. Запишите содержимое аккумулятора в любую ячейку памяти.

Если объема внутренней памяти недостаточно, используется режим работы с внешней памятью. При этом встроенное ПЗУ может либо включаться, либо не включаться в адресное пространство в зависимости от состояния вывода ЕА ВЕ51 (при подаче на ЕА нулевого потенциала ВЕ51 устанавливается в режим работы только с внешней памятью). При этом порты Р0 и Р2 используются для обеспечения обмена с внешней памятью (это

относится как к внешней памяти программ, так и к внешней памяти данных):

при обращении к внешней памяти через порт Р2 выводится старший байт адреса ячейки внешней памяти и удерживается в течении всего цикла обращения, через порт РО вначале цикла обращения выводится младший байт адреса, который стробируется сигналом ALE, затем через порт РО производится обмен данными.

Рассмотрим схему подключения внешней памяти к ВЕ51 на примере УМПК—51, которую удобно разделить на две части. Первая из них, приведенная на рис. 11, представляет собой стандартное "ядро" устройства на базе ВЕ51 при работе с внешней памятью. Вторая часть схемы, показанная на рис. 12, представляет собой один из вариантов подключения статического ОЗУ : ПЗУ к схеме, представленной на рис.11.

Тактовая частота работы ВЕ51 задается кварцевым резонатором BQ1 и составляет в УМПК—51 6 МГц. Начальная установка осуществляется нажатием на клавишу SB2 ("R"), а также при включении питания с помощью цепи R2, С 16. Буфер данных D4 служит для организации внутренней магистрали данных УМПК—51. Буфер переключается на ввод информации сигналом RP/, представляющим собой логическое "И" сигналов чтения памяти команд PSEN/ и чтения памяти данных RD/, и, таким образом, переключается на ввод данных при чтении из совмещенной внешней памяти команд и данных. Регистр адреса D3 защелкивает младший байт адреса по сигналу ALE. Сумма сигналов PSEN/, RD/ и WR/ (WPR/) предназначена для стробирования схем дешифрации адреса с целью исключения ложных выборок при сменах адресов.

Рис. 11. Ядро системы на базе ВЕ51 в режиме работы с внешней памятью.

Сигналы магистралей адреса (А0...А7), данных (D0...D7), и управления (WR/, RP/, WPR/), формируемые схемой, представленной на рис. 11, и объединенные в шину М, будут использоваться в некоторых схемах, приведенных ниже, в этом случае подразумевается использование всей схемы, представленной на рис. 11.

Схема подключения внешней памяти представлена на рис. 12. Блок постоянной памяти реализован на двух ПИЗУ с УФ стиранием типа К573РФ2 объемом по 2 кбайт (D8, D9), одна из которых содержит управляющую программу— монитор УМПК—51, вторая может быть использована для записи программ пользователя. Дешифратор адреса (D6.2, D10) формирует выборку для D8 при чтении команд или данных по адресам 0000...07FFH и для D9 при чтении по адресам 0800...0FFFH внешней памяти. Оперативная память содержит две ИС статического ОЗУ КР537РУ8 объемом по 2 кбайт (D13, D14). Дешифратор адреса формирует выборки для D13 и D14 при обращении к адресам 1000...17FFH и 1800...1FFFH внешнем памяти, соответственно.

Рис. 12. Подключение внешней памяти к ВЕ51.

СчитЫВАНИЕ информацию из ячейки микросхемы 0000H в аккумулятор.

МОV DPTR,#0000H

MOVX @DPTR,A

22. Программно реализовать логическую функцию «неравнозначности» на микроконтроллере К1816ВЕ51. Ввод сигналов имитировать состоянием переключателей, вывод свечением светодиодов. Переключатели и светодиоды подключить к порту Р1.

МЕТКИ |

МНЕМОНИКА |

КОМЕНТАРИИ |

|

ORG 1000H |

|

|

EQU STOP,02F3H |

|

|

MOV 90H,FFH |

|

|

|

|

K |

MOV C,90H |

|

|

ANL C,/91H |

|

|

MOV 00H,C |

|

|

MOV C,91H |

|

|

ANL C,/90H |

|

|

ORL C,00H |

|

|

MOV 92H,C |

|

|

SJMP K |

|