- •Форматы и структура команд микропроцессора к580.

- •Способы адресации микропроцессора к580. Примеры ассемблерных команд Способы адресации:

- •Способы выбора адресов зу и портов ввода вывода микропроцессорной системы на базе к580.

- •Способы обмена информацией мп с зу и устройствами ввода-вывода. Сравнительная оценка способов обмена.

- •Разобрать фрагмент программы обмена информации мп с внешними устройствами. Тип микропроцессора определяет студент. Дать структурную схему.

- •Проектирование вычислительных систем на базе мпк кр580 (проектирование цп, схемы подключения зу и внешних устройств).

- •3)Устройства ввода/вывода

- •Разобрать фрагмент программы с использованием асинхронно-программного обмена информацией. Тип микропроцессора определяет студент. Дать структурную схему.

- •Методы преобразования десятичных чисел в двоичный, восьмеричный и шестнадцатеричный код.

- •Методы преобразования двоичных, восьмеричных и шестнадцатеричных чисел в десятичные.

- •Пример организации дешифрации адресов внешних устройств и микросхем памяти. Понятие о раздельной и совместной картах адресации.

- •15. Разработать мпс пуска асинхронного двигателя с фазным ротором в две ступени в функции скорости. Датчик скорости аналоговый.

- •16. Методы адресации микроконтроллера 1816ве51. Примеры ассемблерных команд.

- •17. Составить фрагмент программы считывания информации с ацп для контроллера 1816ве51 (Адреса: пуск - 8300н, готов – 8200н, выход данных – 8000н).

- •18. Составить подпрограмму «бегущего огня» на микроконтроллере 1816ве51. Дать структурную схему. Выдержка времени аппаратная.

- •19. Составить подпрограмму потетрадного свечения светодиодов схемы, построенной на мк1816ве51. Дать структурную схему мп - схемы.

- •23. Разработать функциональную схему мп – системы сбора четырех аналоговых сигналов. Составить программу. Тип контроллера выбирает студент.

- •24. Система прерывания микроконтроллера семейства мк51. Вектор прерываний. Прерывание от внешних событий. Пример управления программой кнопки “Пуск” в режиме прерывания.

- •25. Система таймеров мк семейства мк-51. Режимы работы таймеров. Организация выдержки времени. Пример.

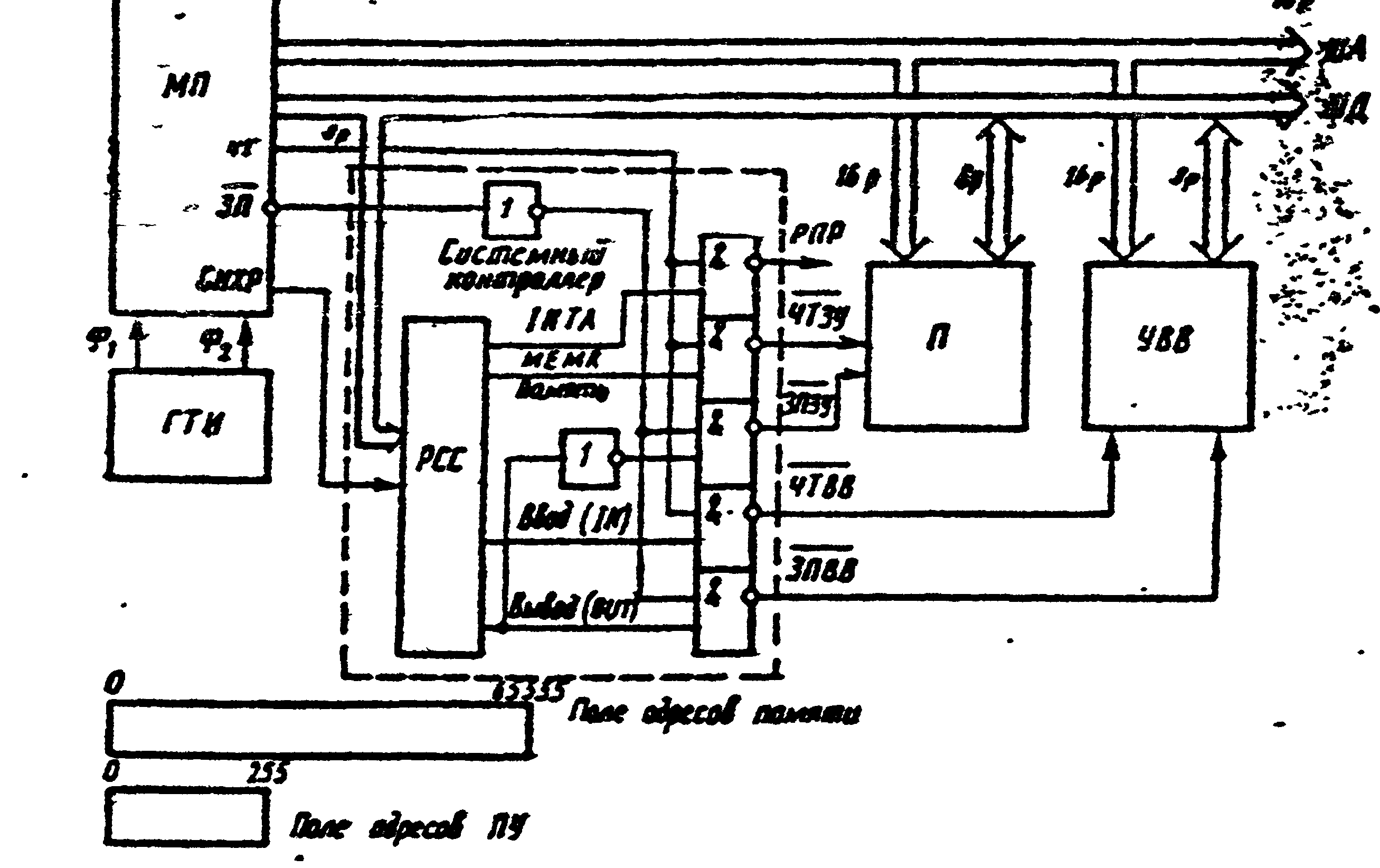

Пример организации дешифрации адресов внешних устройств и микросхем памяти. Понятие о раздельной и совместной картах адресации.

Рассмотрим схему на рис. 2.19, а.

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

||

стробы DC |

позиционный код DC |

ПЗУ |

|||||||||||||||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

||

0 |

0 |

0 |

0 |

||||||||||||||

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

||

0 |

7 |

F |

F |

||||||||||||||

Таким образом, диапазон адресов ПЗУ 0000÷07FF.

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

||

стробы DC |

позиционный код DC |

ОЗУ |

|||||||||||||||

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

||

0 |

8 |

0 |

0 |

||||||||||||||

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

||

0 |

F |

F |

F |

||||||||||||||

Таким образом, диапазон адресов ПЗУ 0800÷0FFF.

Рис. 2.19. Схема подключения памяти (а) и внешних устройств (б) к магистрали микроЭВМ

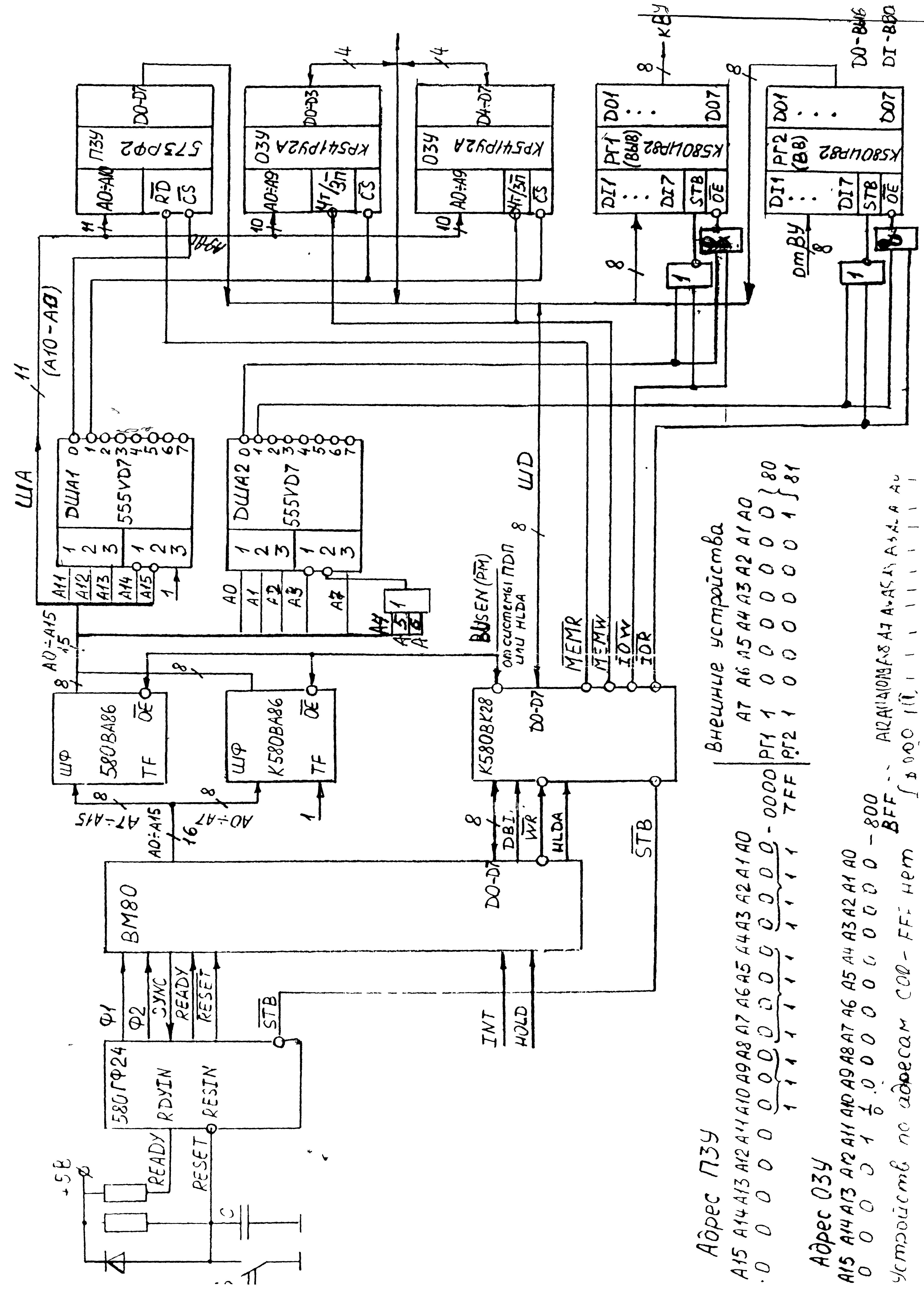

На рис. 2.19,а показан пример подключения микросхем ОЗУ и ПЗУ к магистралям ЭВМ. Дешифратор Д2 (К555ИД7) стробируется сигналом чтения памяти и запись в память и служит для выбора восьми областей памяти емкостью по 2 Кбайт и лежащих в диапазоне 0000÷3FFFH. Первую область(0000÷07FFH) занимает микросхема ПЗУ (Д5) емкостью 2 Кбайт, вторую (0800÷0FFFH) - микросхема ОЗУ (Д4) емкостью 1 Кбайт. К другим областям памяти микросхемы ОЗУ и ПЗУ подключаются аналогично.

На рис. 2.19, б показан пример организации дешифрации адреса внешних устройств. Схема позволяет подключать к магистралям до 64 устройств ввода/вывода. Использование четырех таких схем реализует возможности в микропроцессорной БИС по адресации внешних устройств. Дешифратор адреса Д2, стробируемый сигналом чтения ввода ( ) или записи ввода/ вывода для выбора либо дешифраторов адреса для восьми простейших регистров ввода, либо схем, содержащих несколько таких регистров (КР580ВВ55, КР580ВВ51, КР580ВТ57, КР580ВИ53, КР580ВН59). В качестве простейшего устройства на рис. 2.19, б показан регистр ввода/вывода К589АП16. Входные сигналы подключаются ко входам А0-А3 микросхем Д4, Д5, а выходные к выходам С0-С3.

При обращении к устройствам ввода/вывода и к ячейкам памяти дешифраторы адреса должны стробироваться сигналами , , , . При таком способе дешифрации необходимо следить, чтобы адресное пространство устройств ввода/вывода не перекрывалось с адресным пространством микросхем ОЗУ и ПЗУ.

Адресация устройств ввода/вывода производится как старшим байтом магистрали адреса, так и младшим байтом. Оба восьмиразрядных адреса дублируется на соответствующих байтах шины адреса.

Понятие о раздельной и совместной картах адресации

Конкретная структура интерфейса центрального процессора зависит от способа организации управления микросхем памяти и внешних устройств, а также от структуры системной магистрали. Память и интерфейс ввода/вывода по отношению к центральному процессору можно представить как совокупность запоминающих ячеек с произвольным доступом. При этом МП выдает адреса памяти и устройств ввода/вывода на общую адресную магистраль. Важной задачей интерфейса является разделение или селекция адресов памяти и устройств ввода/вывода. Способ селекции зависит от принятого способа адресации ячеек памяти и портов ввода/вывода. Существуют два способа: с раздельным полем адресов памяти и устройств ввода/вывода (с раздельной картой адресов) и с общим полем адресации памяти и устройств ввода/вывода.

При раздельном способе адресации формат адресного слова памяти и устройств ввода/вывода следующий. Адресное слово памяти

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

поле адресов памяти |

|||||||||||||||

0000-FFFF - область адресов памяти 64 Кбайт.

Формат адресного слова и поле адресов устройств ввода/вывода

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

поле адресов устройств ввода/вывода УВВ |

|||||||

00-FF - область адресов памяти 256 байт как для портов ввода, так и для портов вывода.

При этом способе память и УВВ разделяются сигналами управления памятью и и сигналами управления портами ввода/вывода (READ, WRITE). Эти сигналы формируются при выполнении команд обращения памяти и команд ввода/вывода. При таком способе адресации запоминающих устройств и УВВ область адресов УВВ незначительная (256 байт), но большой объем памяти. Обмен информацией между портами ввода/вывода и памятью производится через аккумулятор. При этом способе селекции адресов используется короткий адрес (дешифратор адреса всего на 8 выходов и в принципе его можно не использовать) и устройство можно расположить в любом месте адресного пространства. Пример схемы центрального процессора с раздельной адресацией показан на рис. 7.3. Пример схем с раздельной адресацией показан на рис. 10.14 и на рис. 6. Применение раздельного способа адресации для УВВ и памяти и выделение для выбора внешних устройств восьми разрядов уменьшает время выполнения команд, а наличие отдельных команд для обращения к памяти и устройствам ввода/вывода позволяет получить более наглядные программы.

Рис. 10.14. Структура микроЭВМ с раздельной адресацией памяти и ПУ

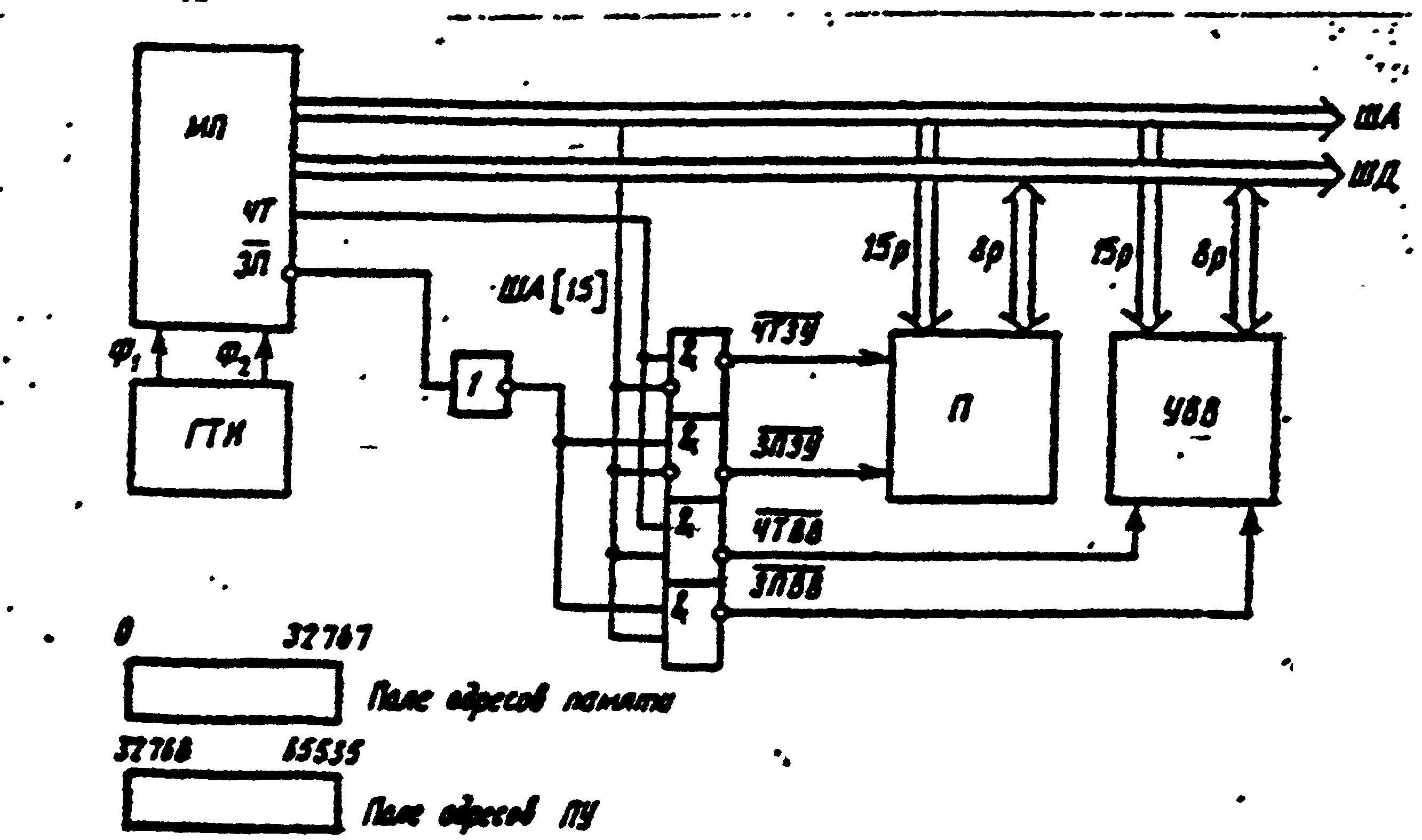

При способе адресации с общим полем запоминающих устройств и устройств ввода/вывода УВВ рассматриваются как ячейки памяти в общем поле адресов. Иногда вычислительное устройство с таким способом адресации называют вычислительным устройством или микроЭВМ с общей шиной. Разделительным признаком является один или группа разрядов адресов. Чаще всего в качестве разделительной линии используют пятнадцатый разряд. Если А15=0, то адресуется память; если А15=1, то адресуется устройство ввода/вывода. Отличительной чертой такой структуры является использование всех команд обращения памяти для работы с устройствами ввода/вывода. В том числе и команд арифметических операций над содержимым портов ввода/вывода без предварительного занесения их содержимого в аккумулятор.

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

Разд. признак |

поле адресов памяти и УВВ |

||||||||||||||

0000-7FFF - область адресов памяти 32 Кбайт.

8000-FFFF - область адресов УВВ 32 Кбайт.

Адресация с общим полем адресов позволяет повысить гибкость и производительность системы. Структура такого способа адресации показана на рис. 10.15.

Рис. 10.15. Структура микроЭВМ с общей шиной

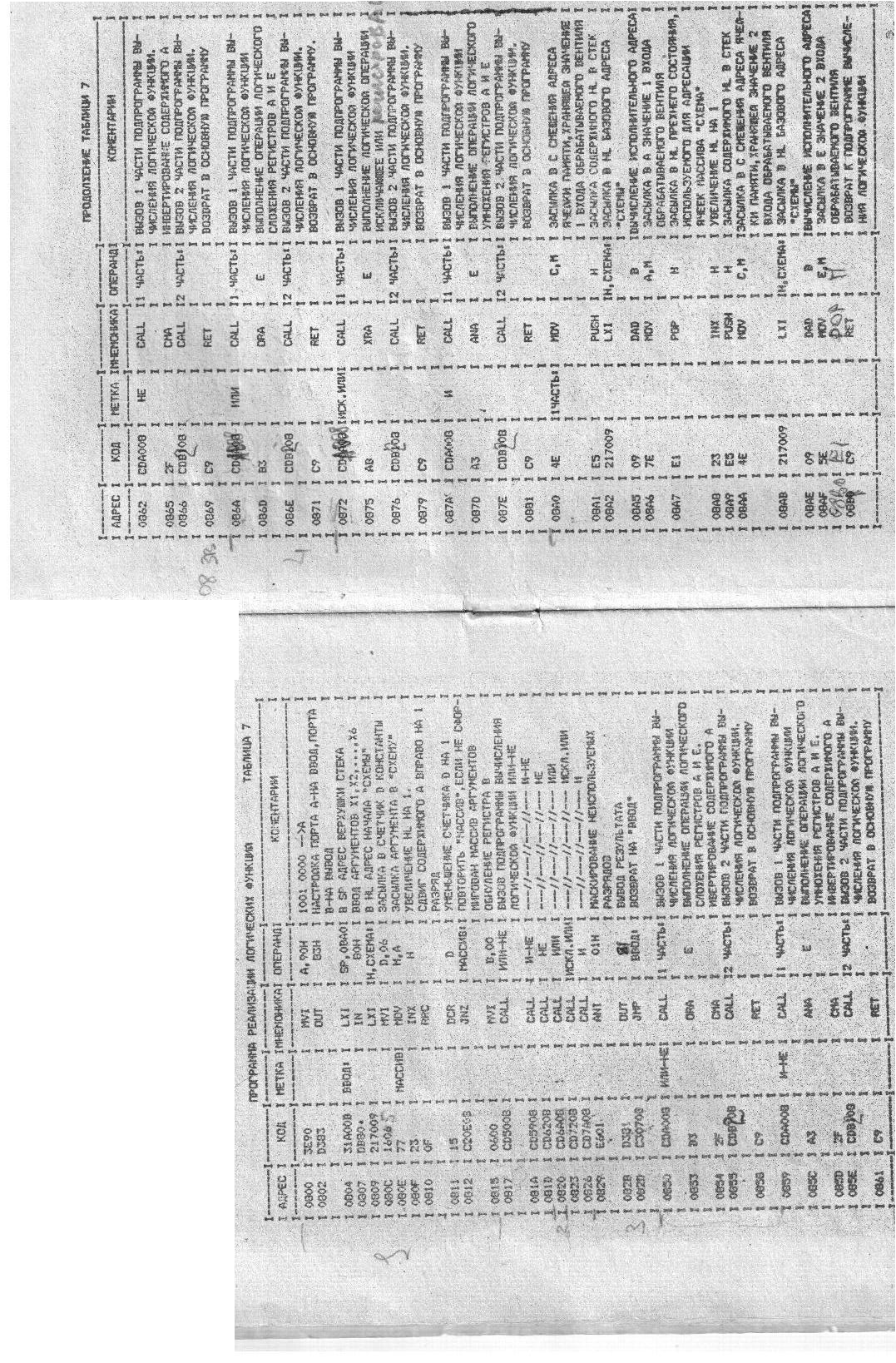

Программно реализовать логическую функцию «ИЛИ-НЕ» (на базе УМК-80).

Программно реализовать логическую функцию «И-НЕ» (на базе УМК-80).

13. Программно реализовать логическую функцию «И» (на базе УМК-80).

14. Программно реализовать логическую функцию «неравнозначности» (на базе УМК-80).

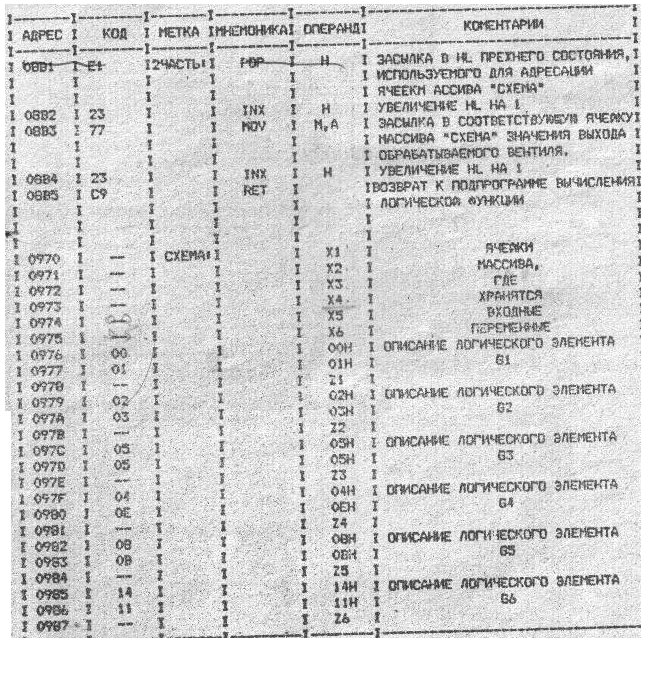

Любую по сложности функцию можно реализовать используя универсальную программу представленной таблицой ниже

Программа предложенная в таблице в зависимости от сложности предложенной функции корректируется в следующих ячейках:

Адрес ячейки |

Кррекция |

080С |

160х, х- максимальный номер переменной |

081А-0826 |

Последовательность выполняемых логических функций (в соответствии с заданием указываем нужную последовательность) |

0970-097(х-1) |

Ячейки искользуемые программой |

0976-0986 |

Описание заданных логических элементов |