- •Форматы и структура команд микропроцессора к580.

- •Способы адресации микропроцессора к580. Примеры ассемблерных команд Способы адресации:

- •Способы выбора адресов зу и портов ввода вывода микропроцессорной системы на базе к580.

- •Способы обмена информацией мп с зу и устройствами ввода-вывода. Сравнительная оценка способов обмена.

- •Разобрать фрагмент программы обмена информации мп с внешними устройствами. Тип микропроцессора определяет студент. Дать структурную схему.

- •Проектирование вычислительных систем на базе мпк кр580 (проектирование цп, схемы подключения зу и внешних устройств).

- •3)Устройства ввода/вывода

- •Разобрать фрагмент программы с использованием асинхронно-программного обмена информацией. Тип микропроцессора определяет студент. Дать структурную схему.

- •Методы преобразования десятичных чисел в двоичный, восьмеричный и шестнадцатеричный код.

- •Методы преобразования двоичных, восьмеричных и шестнадцатеричных чисел в десятичные.

- •Пример организации дешифрации адресов внешних устройств и микросхем памяти. Понятие о раздельной и совместной картах адресации.

- •15. Разработать мпс пуска асинхронного двигателя с фазным ротором в две ступени в функции скорости. Датчик скорости аналоговый.

- •16. Методы адресации микроконтроллера 1816ве51. Примеры ассемблерных команд.

- •17. Составить фрагмент программы считывания информации с ацп для контроллера 1816ве51 (Адреса: пуск - 8300н, готов – 8200н, выход данных – 8000н).

- •18. Составить подпрограмму «бегущего огня» на микроконтроллере 1816ве51. Дать структурную схему. Выдержка времени аппаратная.

- •19. Составить подпрограмму потетрадного свечения светодиодов схемы, построенной на мк1816ве51. Дать структурную схему мп - схемы.

- •23. Разработать функциональную схему мп – системы сбора четырех аналоговых сигналов. Составить программу. Тип контроллера выбирает студент.

- •24. Система прерывания микроконтроллера семейства мк51. Вектор прерываний. Прерывание от внешних событий. Пример управления программой кнопки “Пуск” в режиме прерывания.

- •25. Система таймеров мк семейства мк-51. Режимы работы таймеров. Организация выдержки времени. Пример.

Проектирование вычислительных систем на базе мпк кр580 (проектирование цп, схемы подключения зу и внешних устройств).

1) проектирование ЦП.

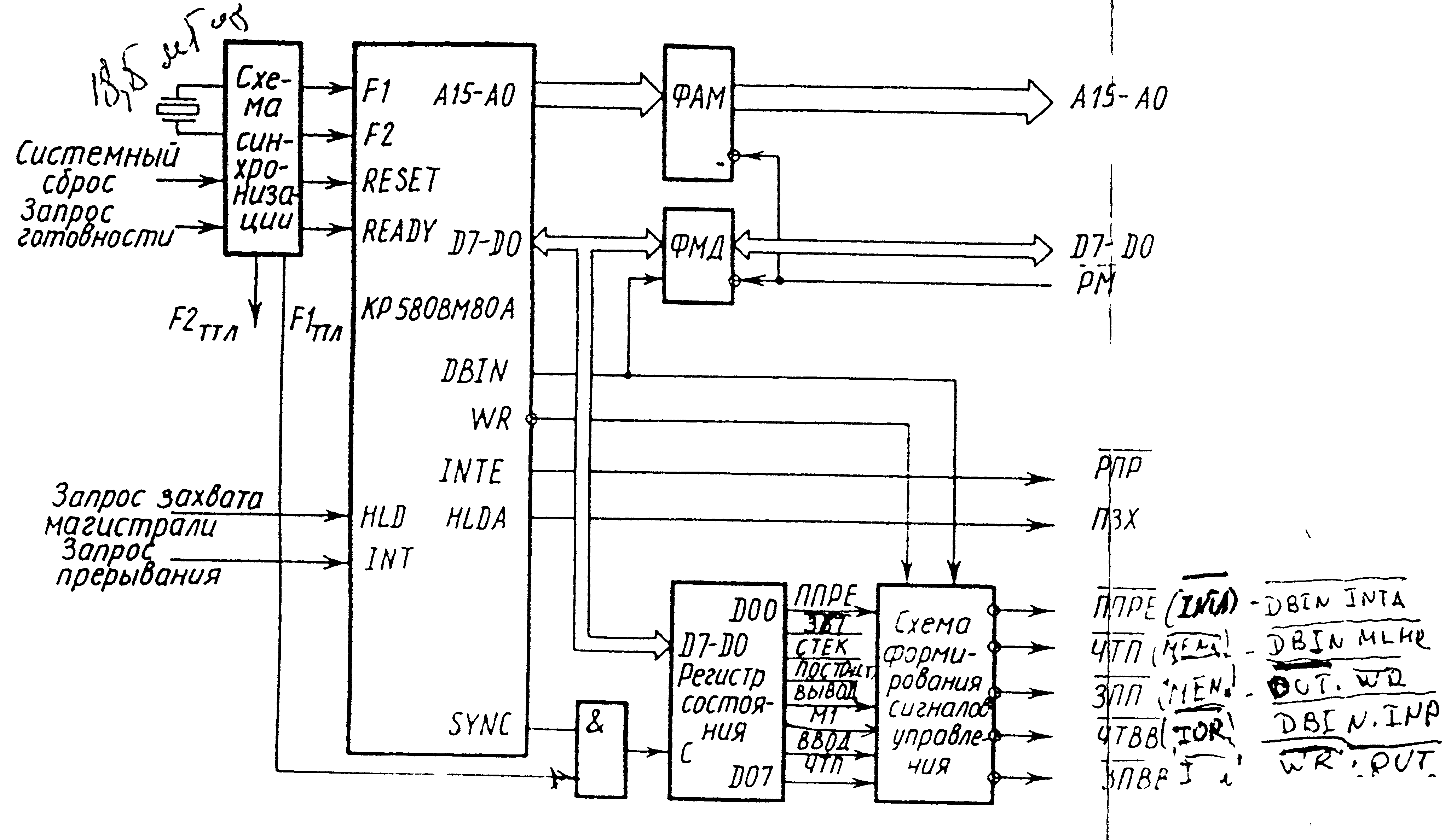

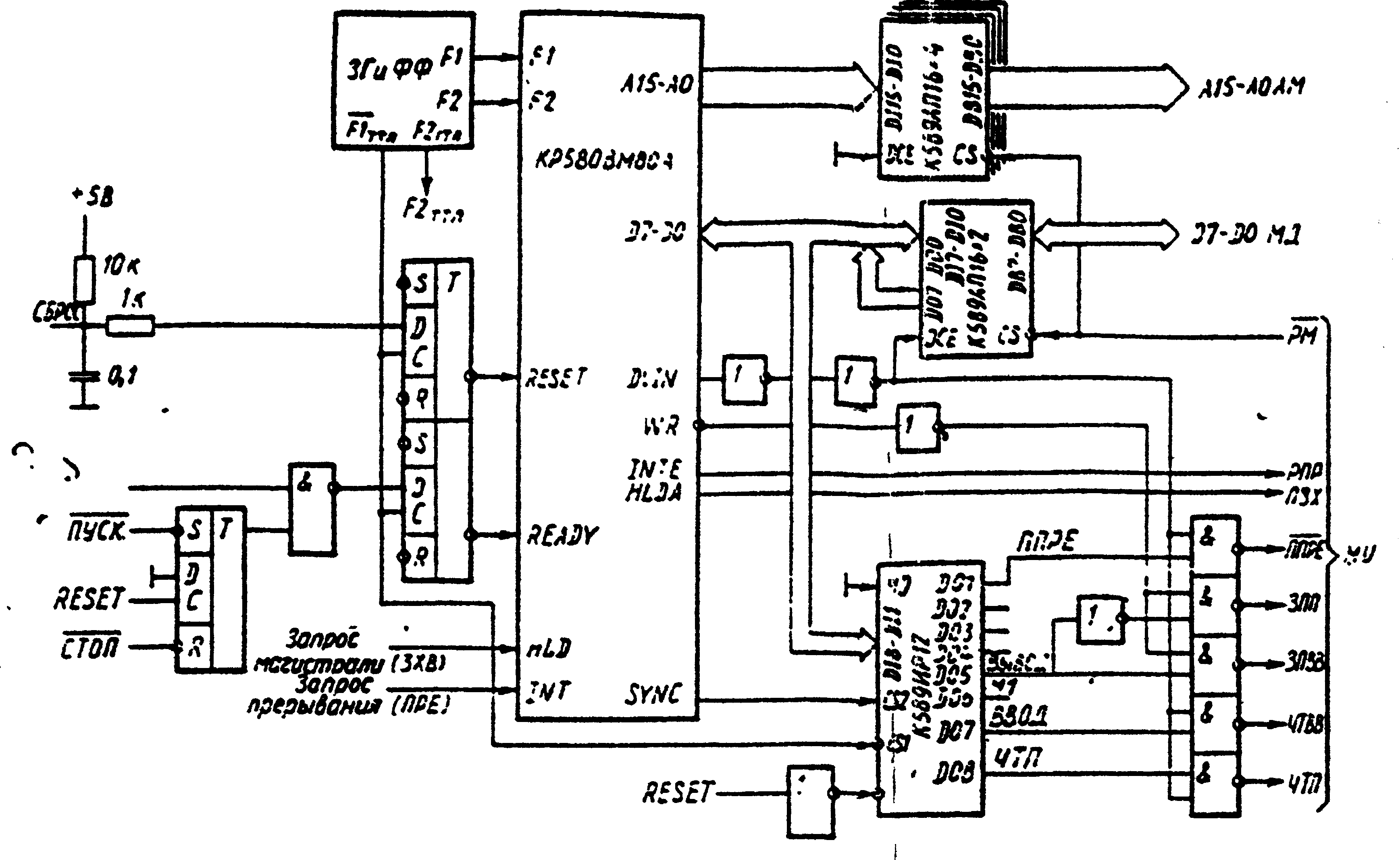

Для построения центрального процессора кроме центрального процессорного элемента дополнительно требуются микросхемы сигналов синхронизации и микросхемы сопряжения центрального микропроцессора с системной шиной. Структура центрального процессорного вычислительного устройства на базе МП КР580ВМ80А представлена на рис.1.

Структура состоит из БИС КР580ВМ80А, схемы синхронизации, схемы сопряжения и управления системной магистралью: формирователя адресной магистрали (ФАМ), формирователя магистрали данных (ФМД) и формирователя магистрали управления (ФМУ).

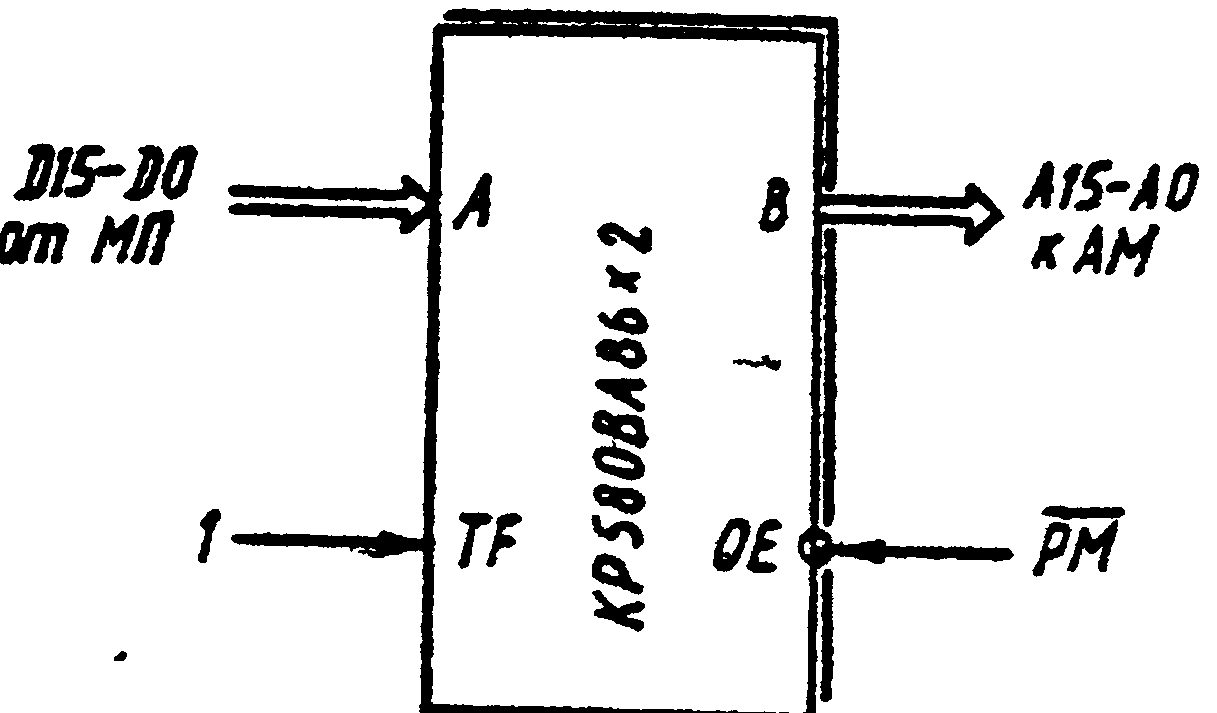

Для согласования по нагрузке шин МП и устройств ввода/вывода в ЦПУ вводятся магистральные формирователи, которые реализуются на микросхемах КР589АП16(26), КР580ВА86 (87). Иногда используются микросхемы КР589ИР12, КР580ИР82.

В качестве регистра состояния, служащего для запоминания и хранения байта состояния, используют различные интегральные схемы регистров или триггеров. Наиболее универсальными для К580 являются БИС восьмиразрядных регистров КР589ИР12 и КР580ИР82.

Для упрощения интерфейса центрального процессора разработаны специальные БИС системного контроллера КР580ВК28 и КР580ВК38. Они производят формирование выходных сигналов магистрали данных и сигналов системной шины управления.

Более подробно:

{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{{

Шинные формирователи

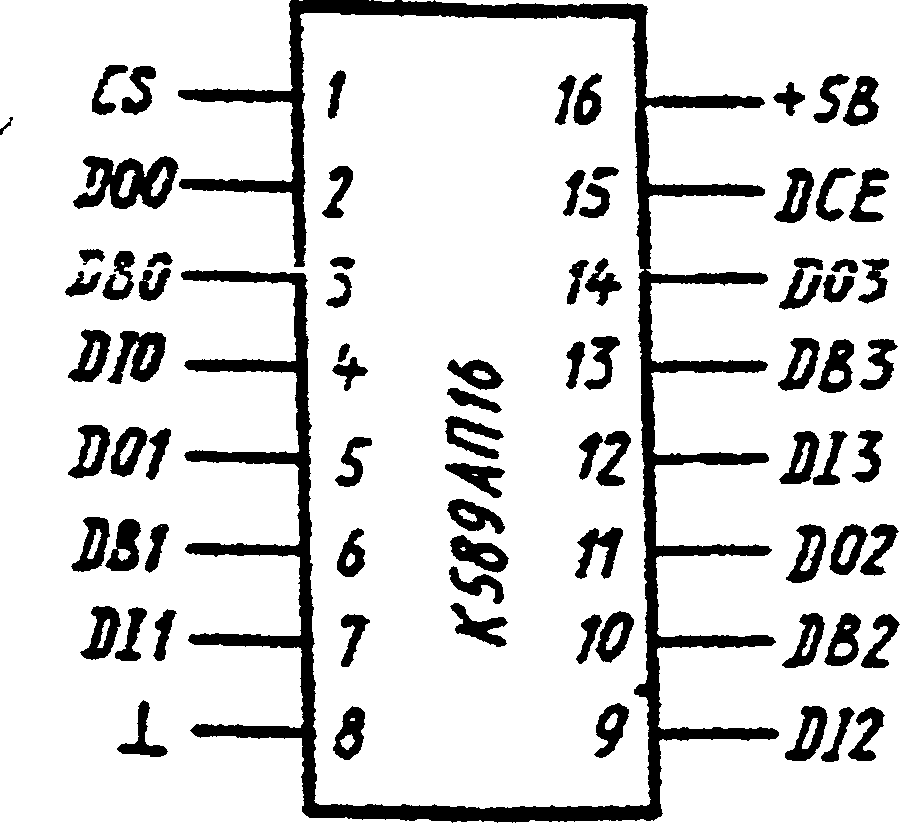

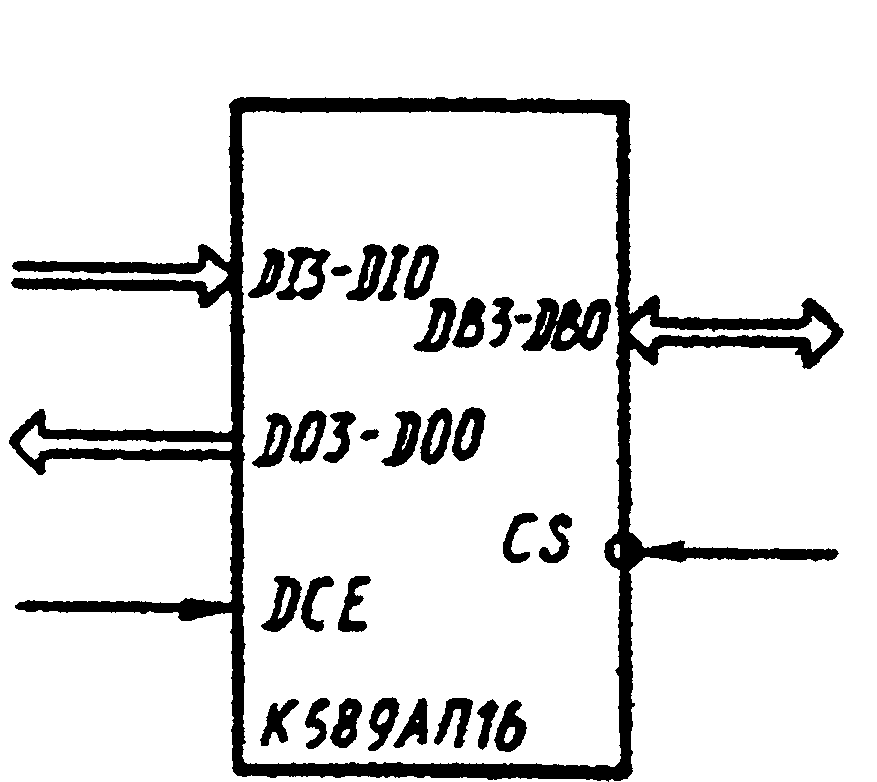

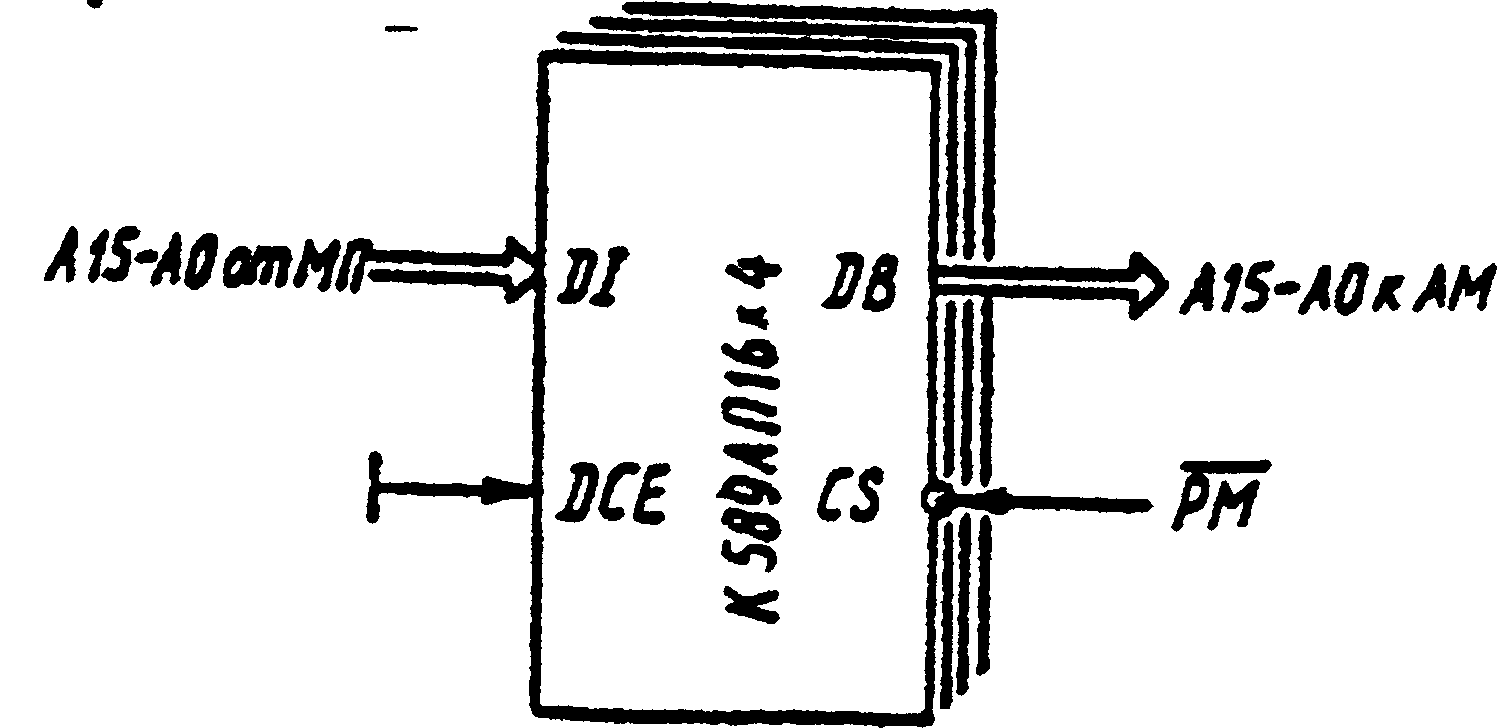

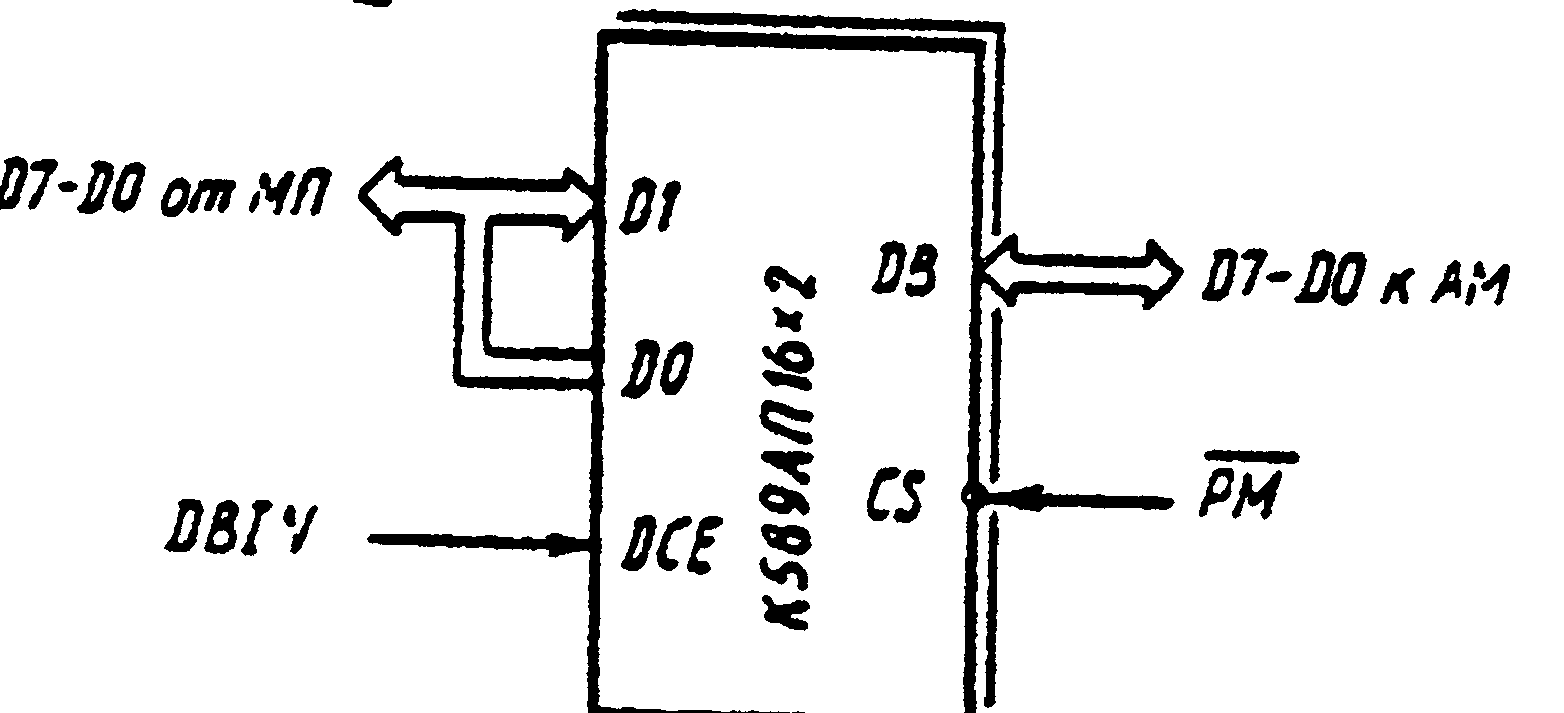

КР589АП16(26) представляет собой четырехразрядные формирователи коммутации. Условное обозначение, цоколевка, функциональная схема и схема подключения показаны на рис. 2.6-2.11.

Рис. 2.6. Цоколевка микросхемы К589АП16

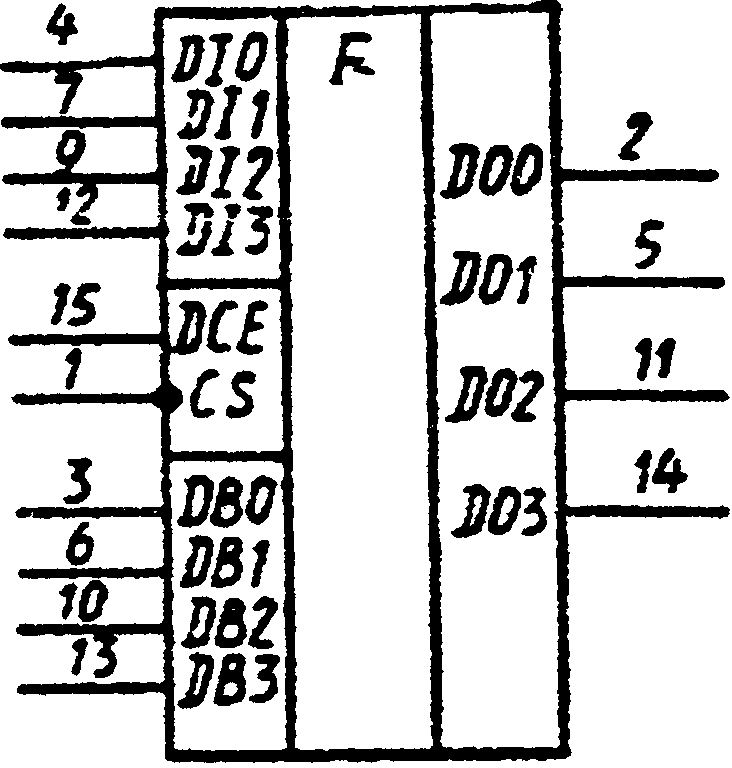

Рис. 2.7. Условное обозначение микросхемы К589АП16

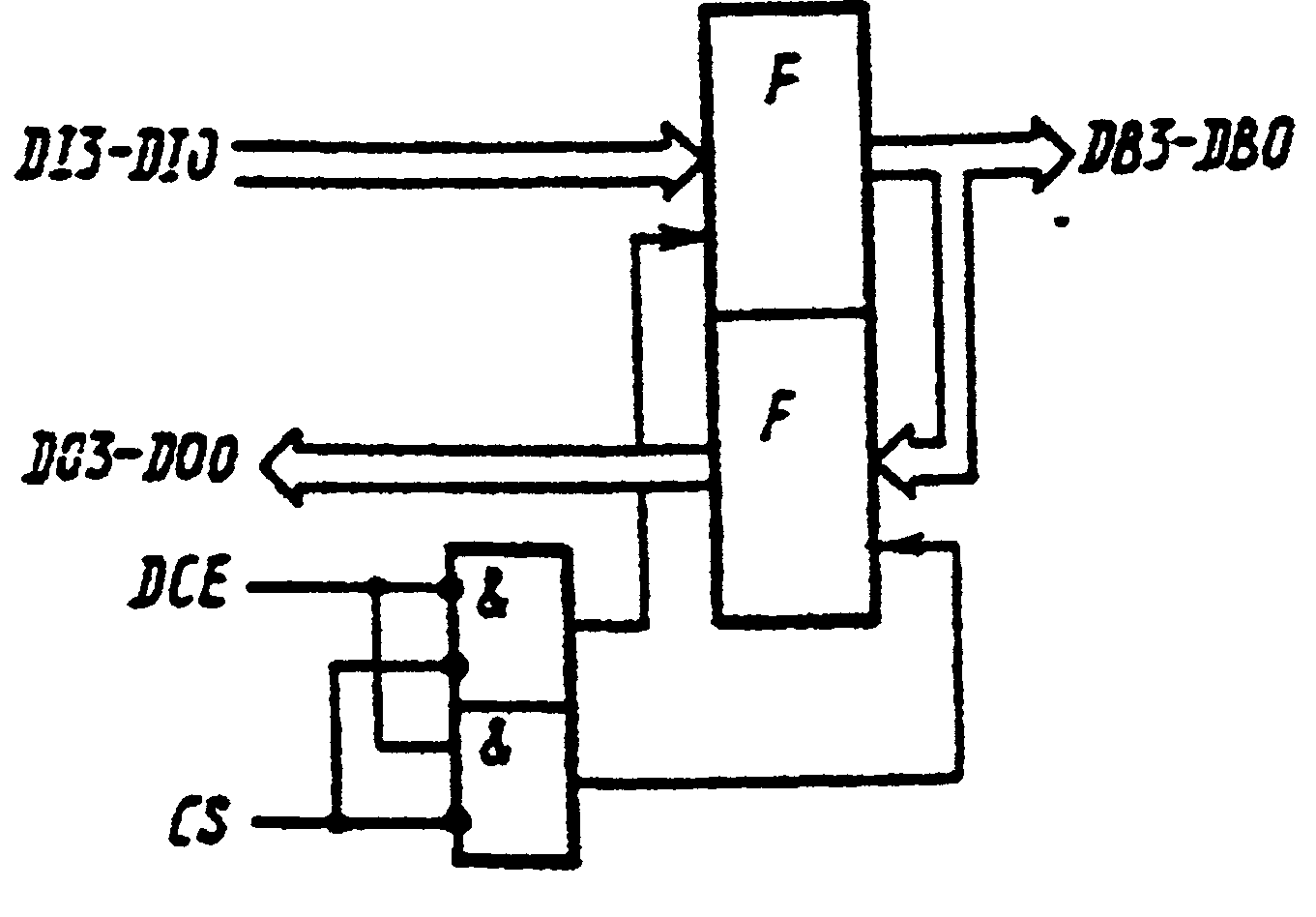

Рис. 2.8. Функциональная схема К589АП16

Рис. 2.9. Схема подключения К589АП16

Рис. 2.10. Схема включения К589АП16 в качестве формирователя адресной магистрали

Рис. 2.11. Схема включения К589АП16 в качестве формирователя магистрали данных

Микросхема имеет четырехразрядный входной канал DI3-DI0, четырехразрядный выходной канал D03-D00 и четырехразрядный двунаправленный канал DB3-DB0 и логические схемы управления режимами передачи данных. При значении сигнала выбора кристалла CS=1 все выходы находятся в состоянии высокого сопротивления, CS=0 микросхема обеспечивает передачу данных. Но при этом, если сигнал DCE=0, информация передается с входных шин на двунаправленную шину; если DCE=1, информация передается с входов двунаправленной шины на выходы выходной шины.

При использовании этой микросхемы в качестве формирователя магистрали данных управление направлением передачи данных производится с выхода «прием» DBIN МП. В режиме прямого доступа к памяти на вход кристалла подключен выход системного разрешения магистрали. Простые схемы в качестве сигнала разрешения магистрали используют сигналы DB3-DB0, в сложных схемах сигнал формируется контроллером прямого доступа к памяти.

При использовании этой микросхемы в качестве формирователя адресной магистрали выход заземлен, так как существует только однонаправленная передача адресов от входных шин к двунаправленным шинам.

Шинный формирователь КР589АП16 увеличивает нагрузку линии ША и ШД до 50 мА.

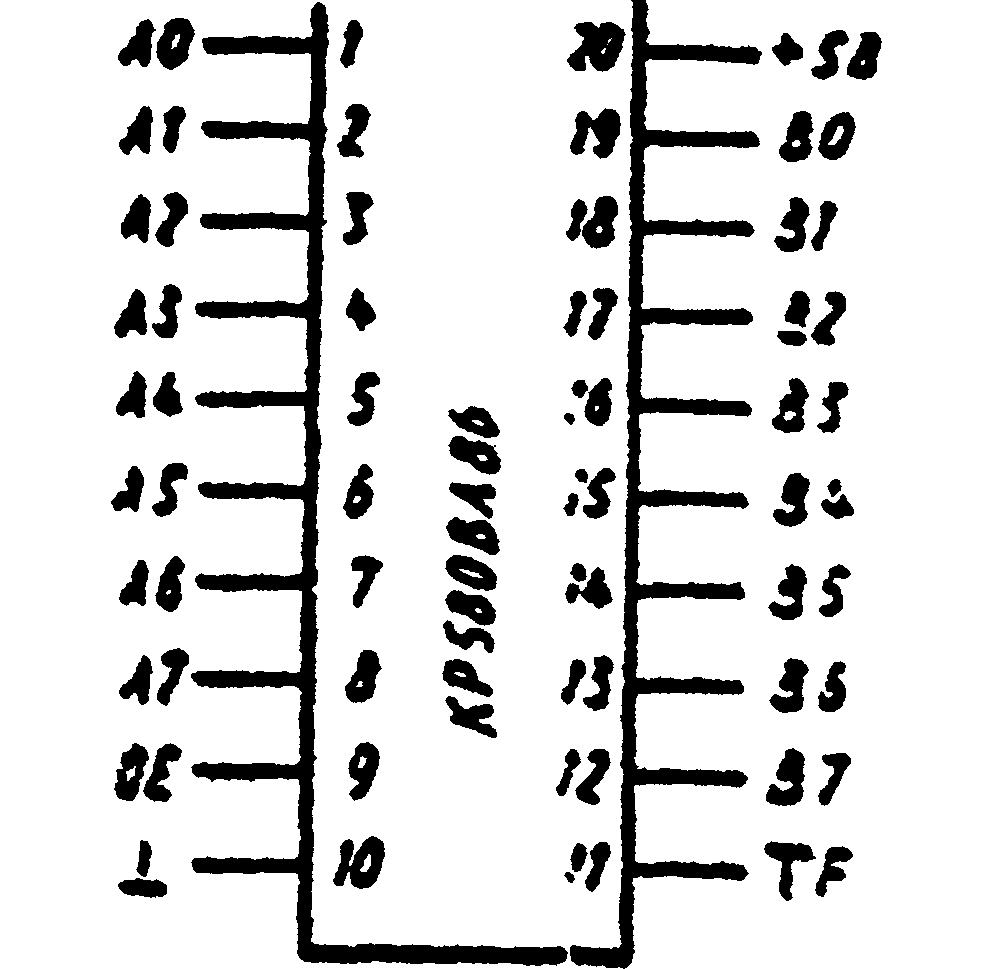

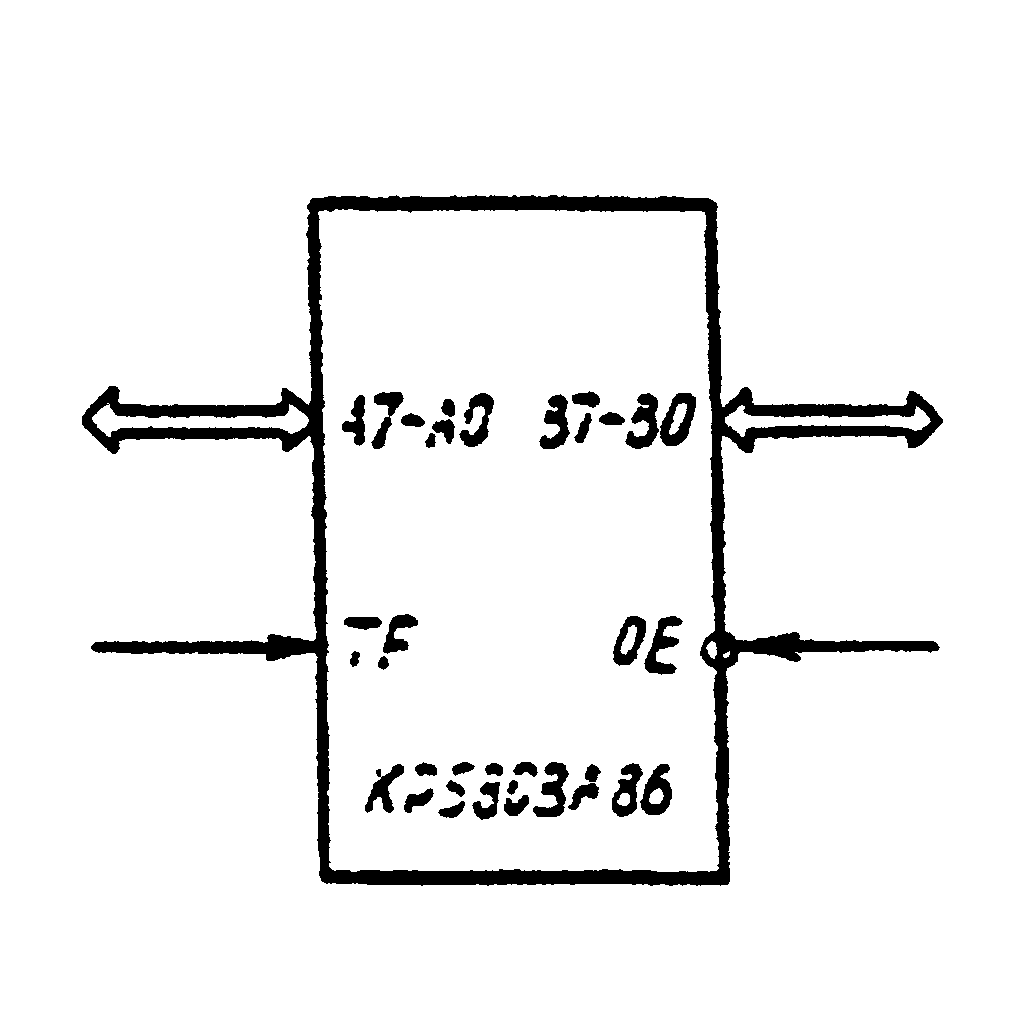

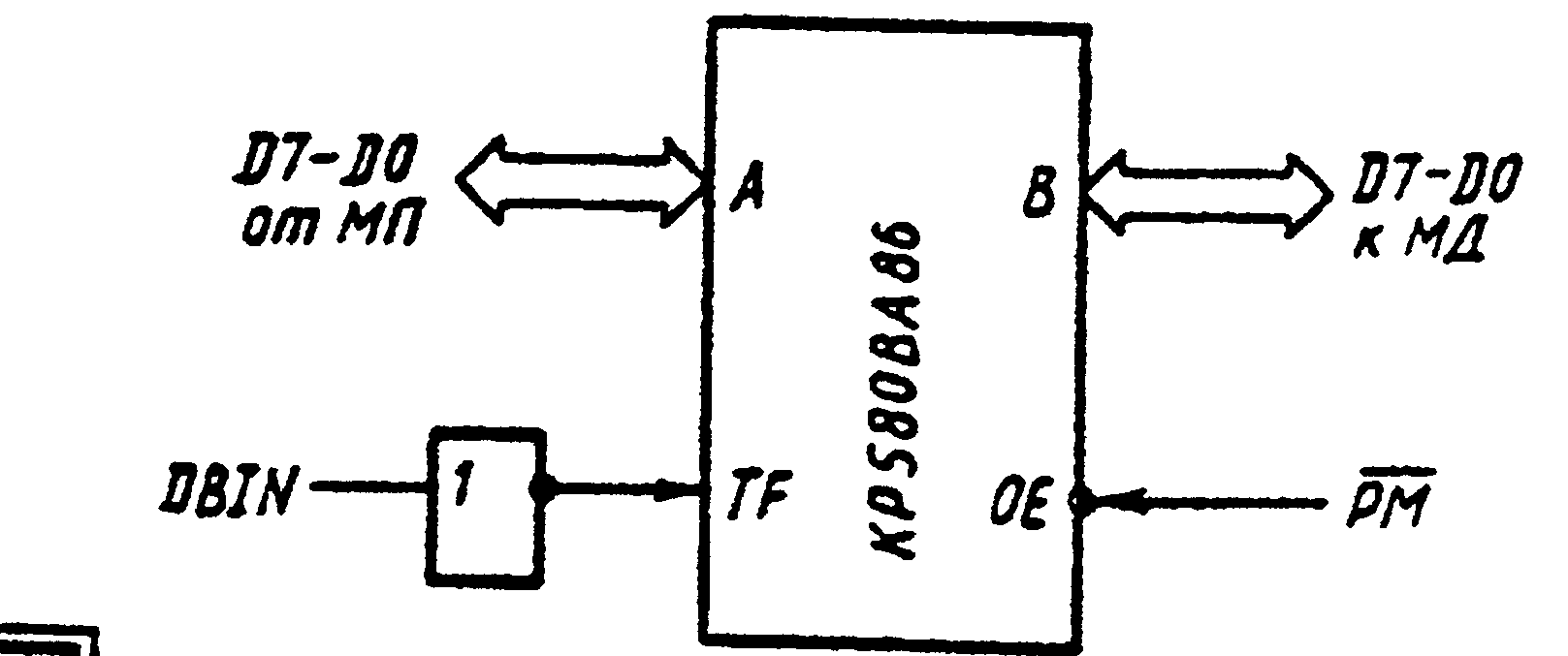

КР580ВА86 - восьмиразрядный двунаправленный формирователь, который обеспечивает ток нагрузки 32 мА. Цоколевка, условное обозначение, функциональная схема и схема включения микросхемы показаны на рис. 2.12-2.17.

В

состав этой микросхемы входит

двунаправленный восьмиразрядный

формирователь с трехстабильными выходами

и схема управления сигналами.

(off

enable)

- сигнал направления передачи информации,

TF

(transmission

fault).

Передача данных разрешена, если сигнал

=0.

Причем если TF=1,

то передача идет от шин A

к B;

если TF=0,то

от шин B

к A.

При

=1

выходы канала переводятся в третье

состояние.

(off

enable)

- сигнал направления передачи информации,

TF

(transmission

fault).

Передача данных разрешена, если сигнал

=0.

Причем если TF=1,

то передача идет от шин A

к B;

если TF=0,то

от шин B

к A.

При

=1

выходы канала переводятся в третье

состояние.

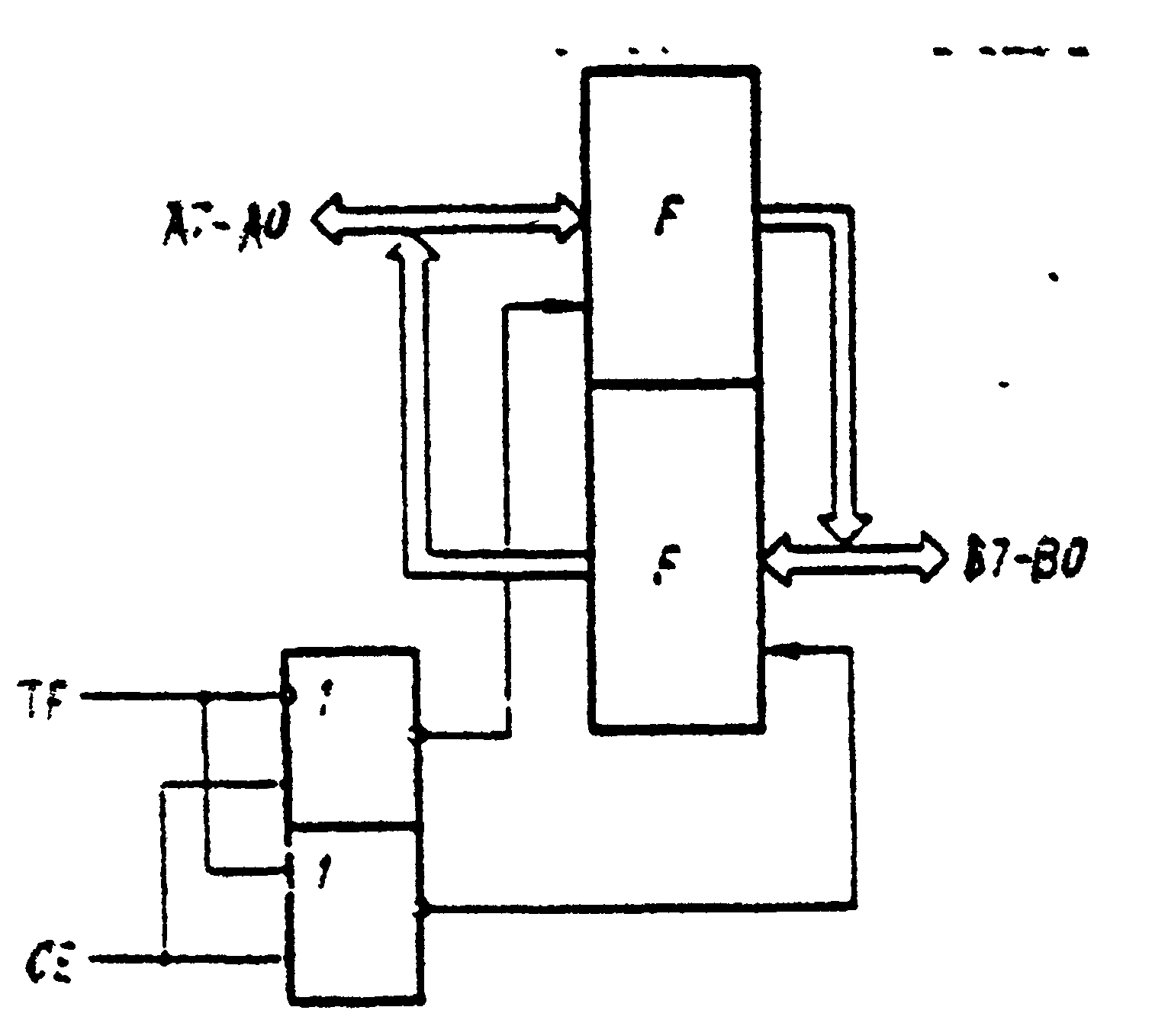

Рис. 2.13. Условное обозначение микросхемы К580ВА86

Рис. 2.14. Функциональная схема К580ВА86

Рис. 2.15. Схема подключения К580ВА86

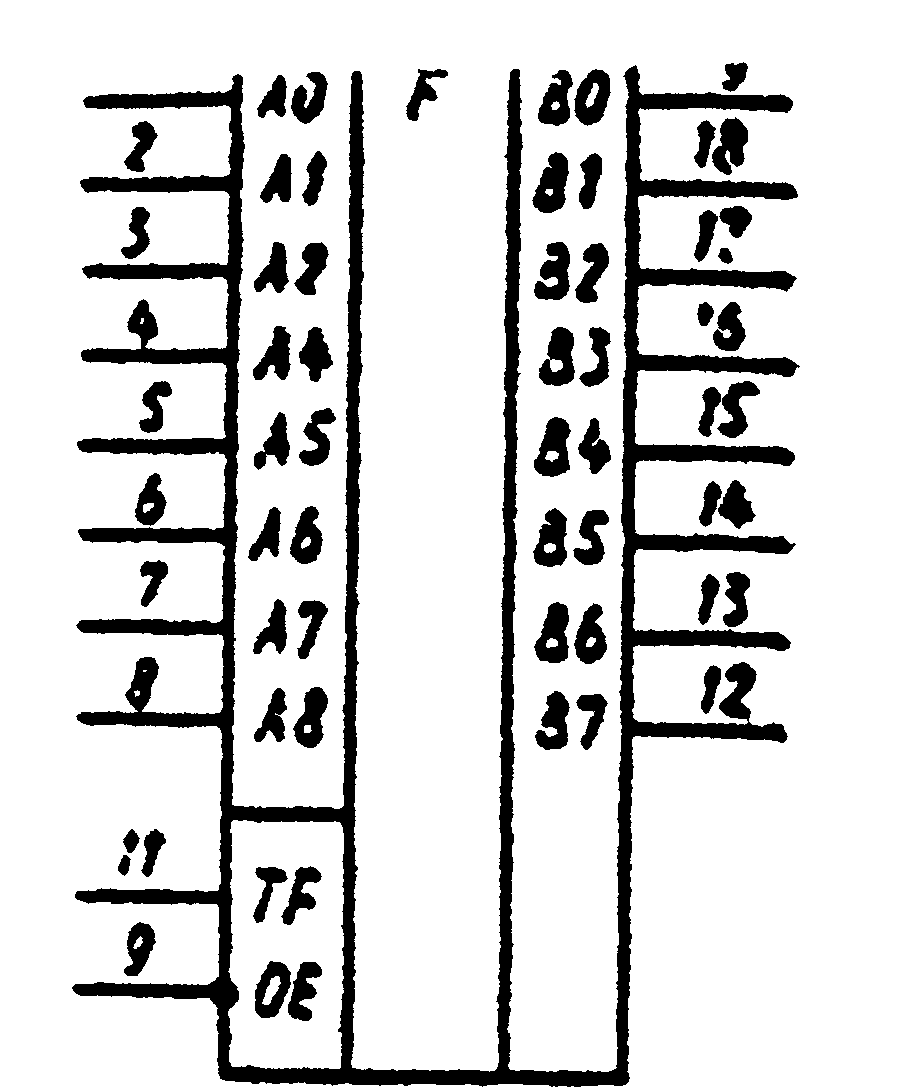

Рис. 2.12. Цоколевка микросхемы К580ВА86

Рис. 2.12. Цоколевка микросхемы К580ВА86

Рис. 2.16. Схема включения К580ВА86 в качестве формирователя адресной магистрали

Рис. 2.17. Схема включения К580ВА86 в качестве формирователя магистрали данных

Регистры состояния

В качестве регистра состояния, служащего для запоминания и хранения байта состояния, используют различные интегральные схемы регистров или триггеров. Наиболее универсальными для К580 являются БИС восьмиразрядных регистров КР589ИР12 и КР580ИР82. Схемы для КР580ИР82 показаны на рис. 2.22-2.26.

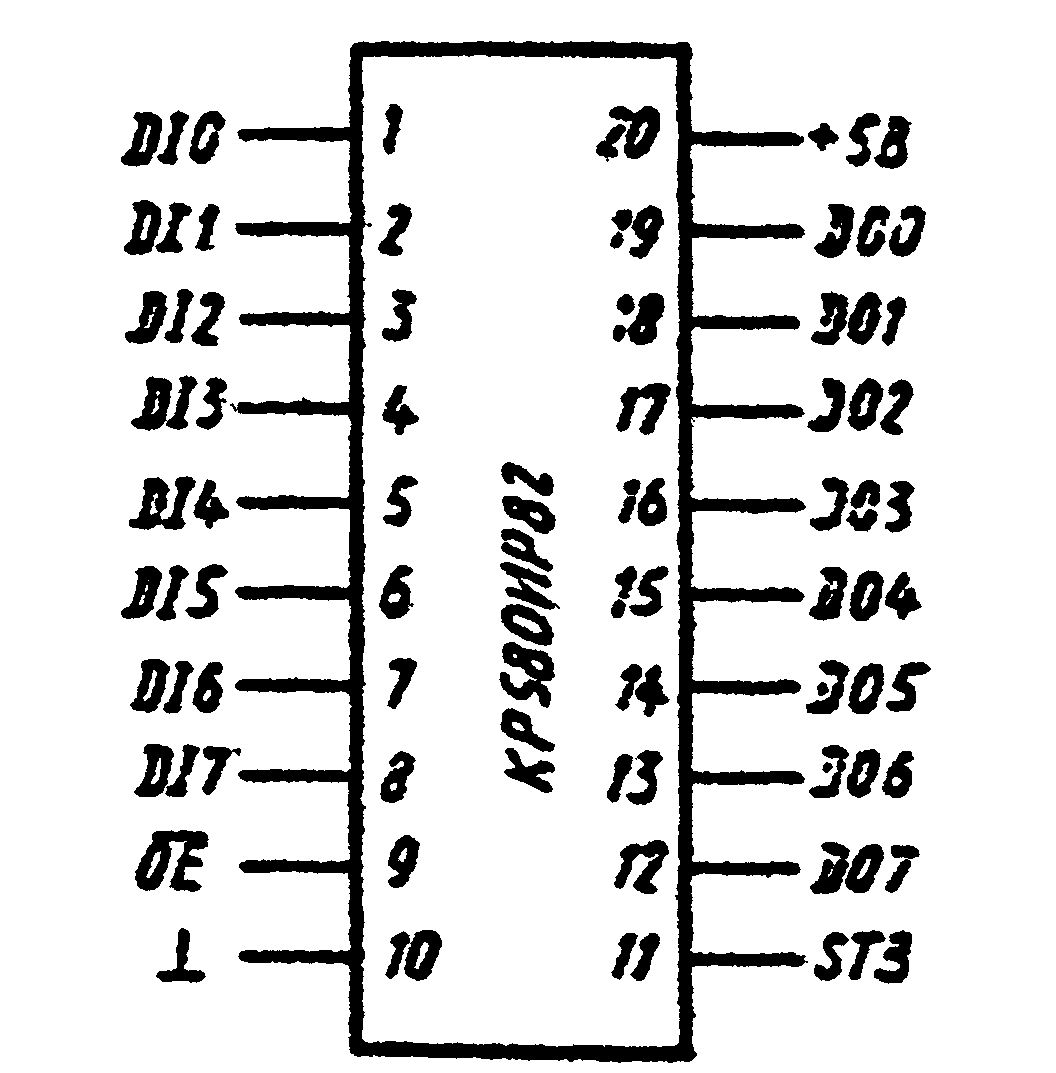

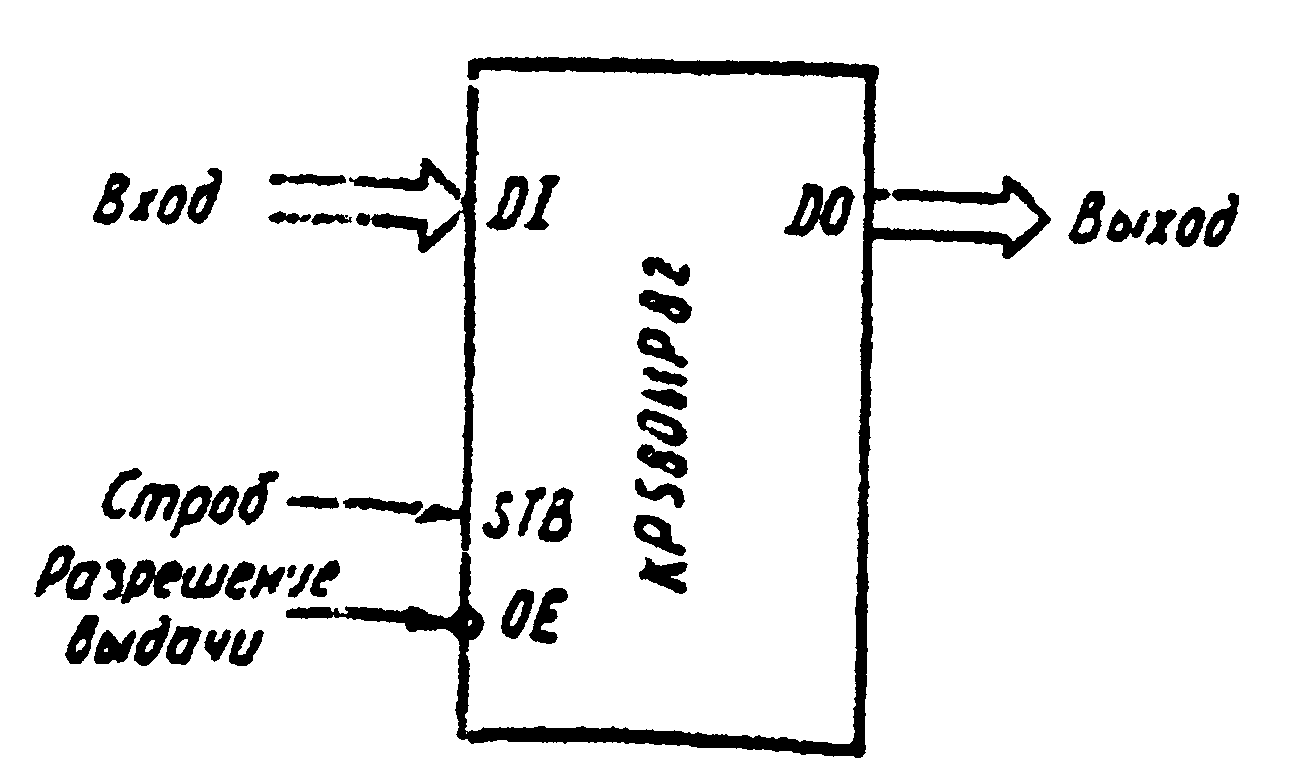

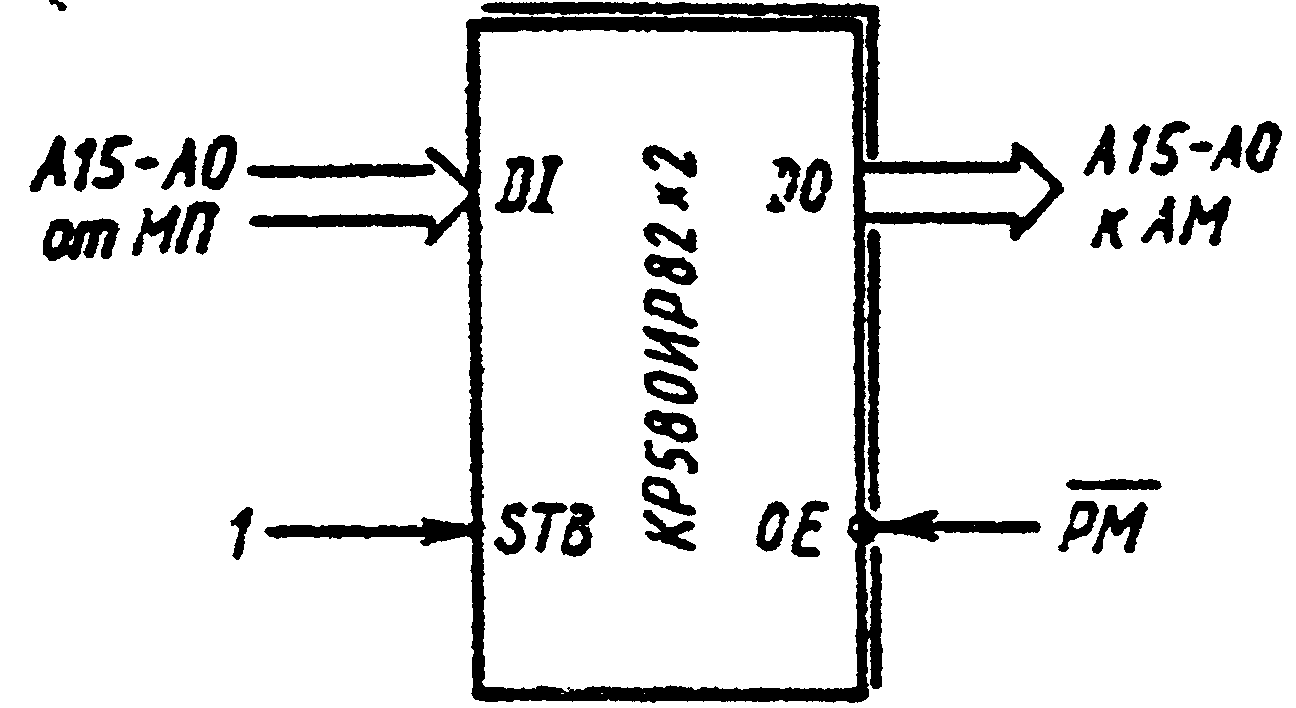

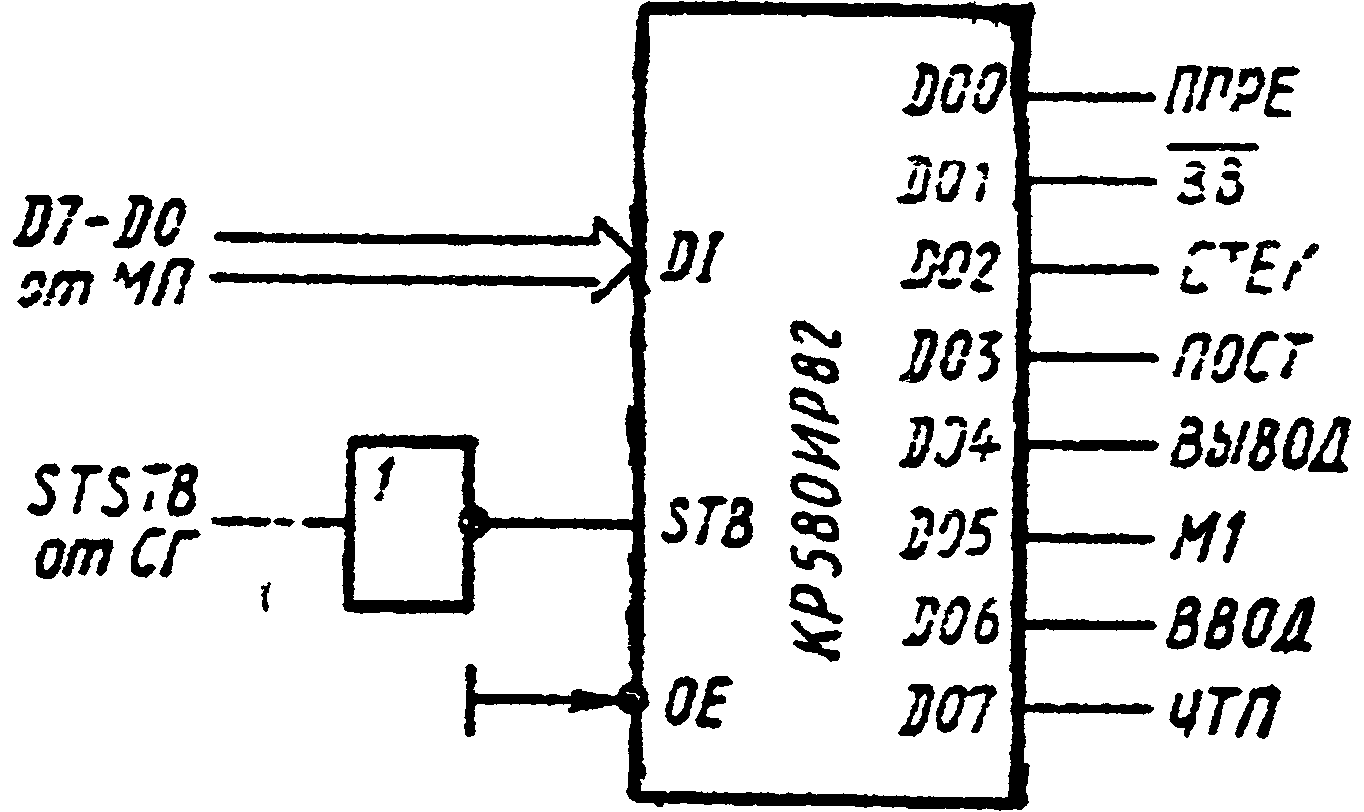

Микросхема КР580ИР82 представляет собой выходной формирователь с управляемыми выходами. Запись производится по сигналу на вход STB («строб»). Чтение информации происходит при сигнале =0. При использовании этой микросхемы в качестве буфера адреса схема его включения показана на рис. 2.25, буфера данных на рис. 2.24, в качестве регистра состояния на рис. 2.26.

Рис. 2.22. Цоколевка микросхемы К580ИР82

Рис. 2.23. Условное обозначение микросхемы К580ИР82

Рис. 2.24. Схема подключения К580ИР82 в качестве буфера данных

Рис. 2.25. Схема подключения К580ИР82 в качестве адресного буфера

Рис. 2.26. Схема подключения К580ИР82 в качестве регистра состояния

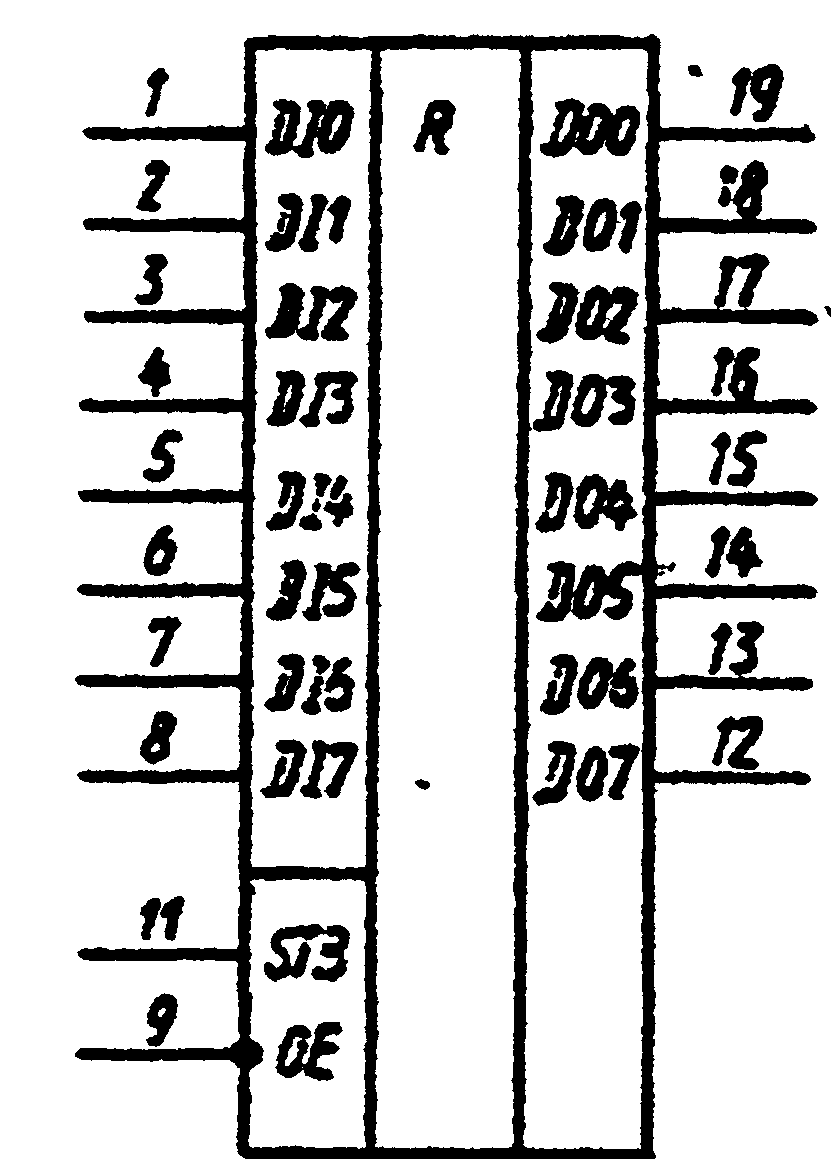

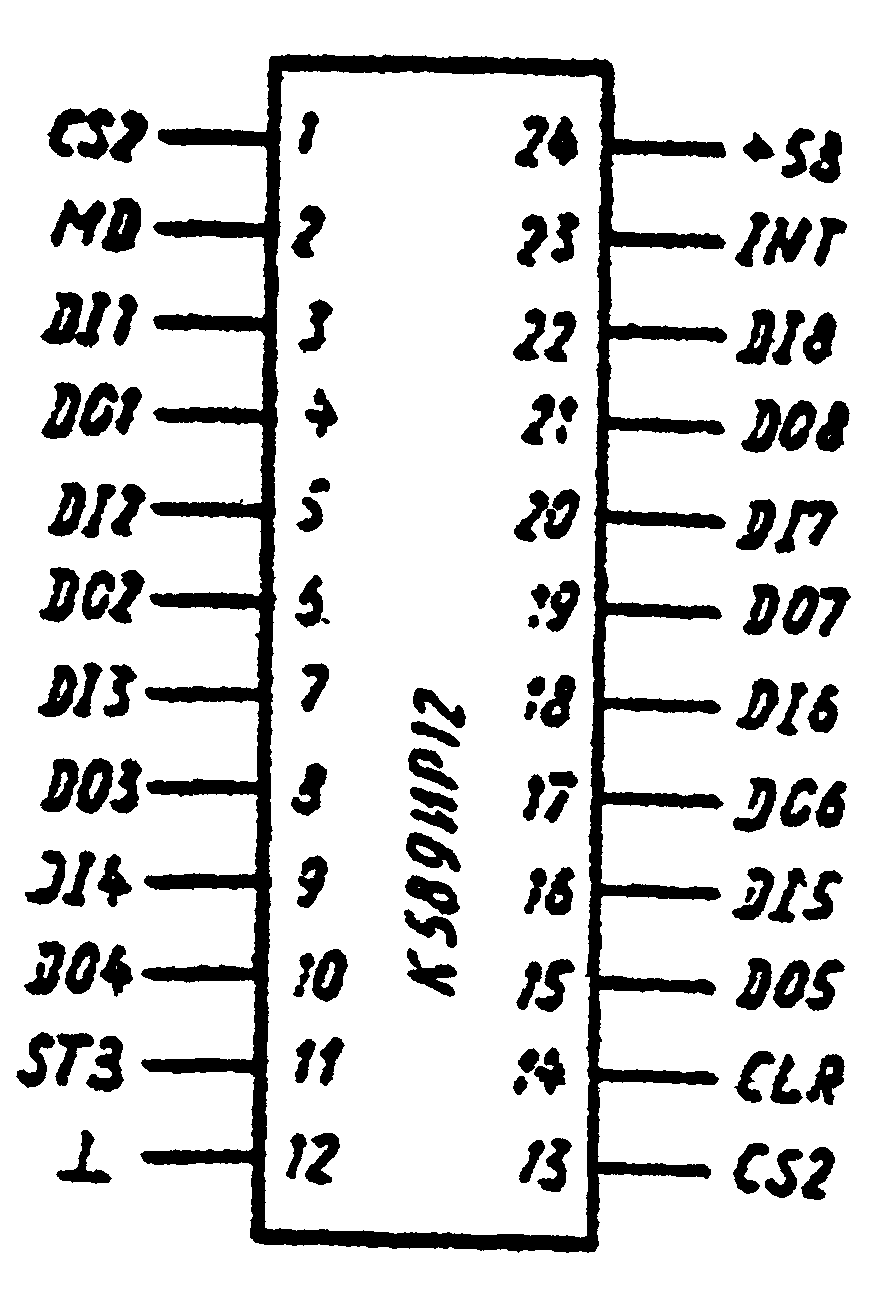

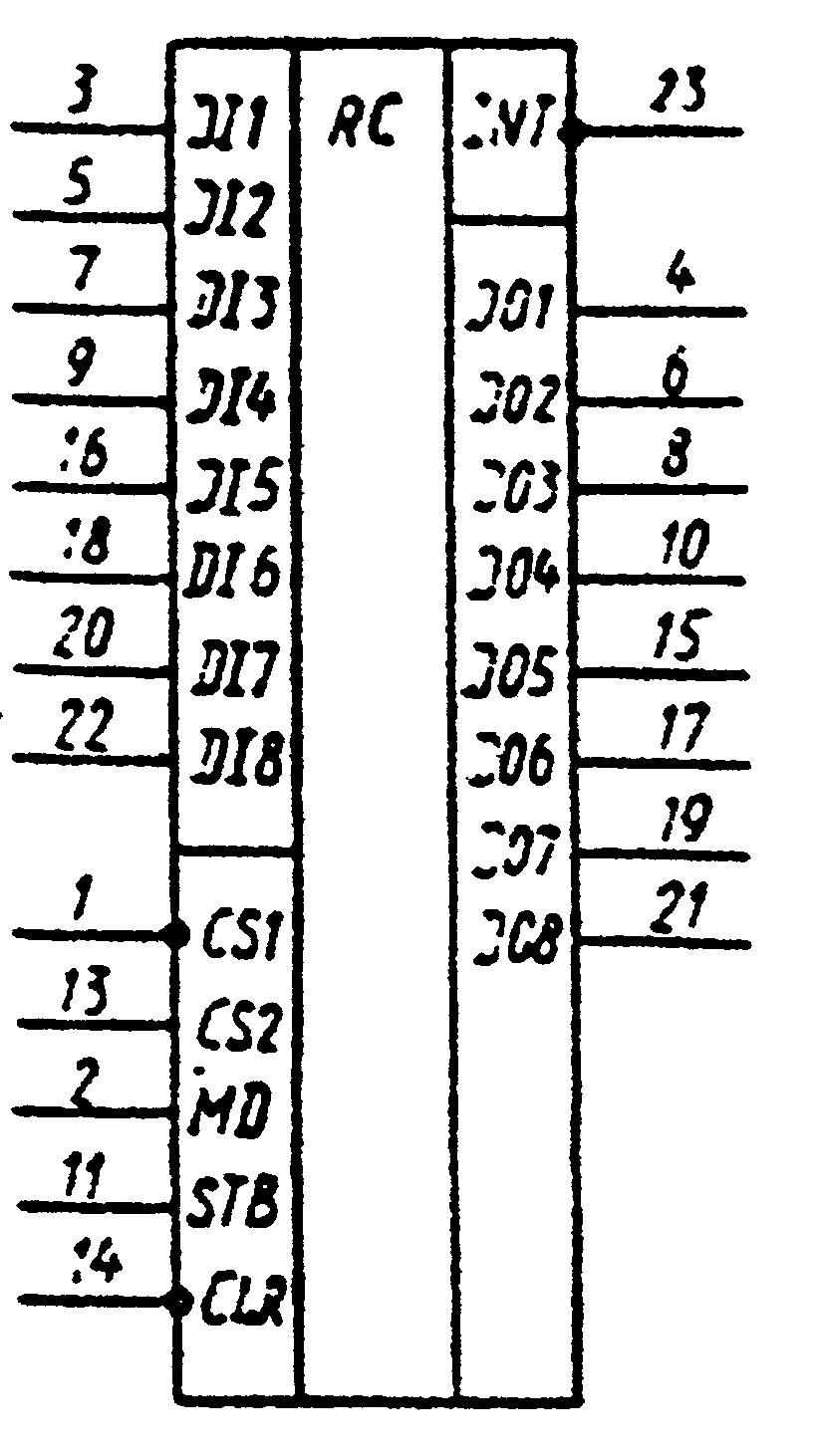

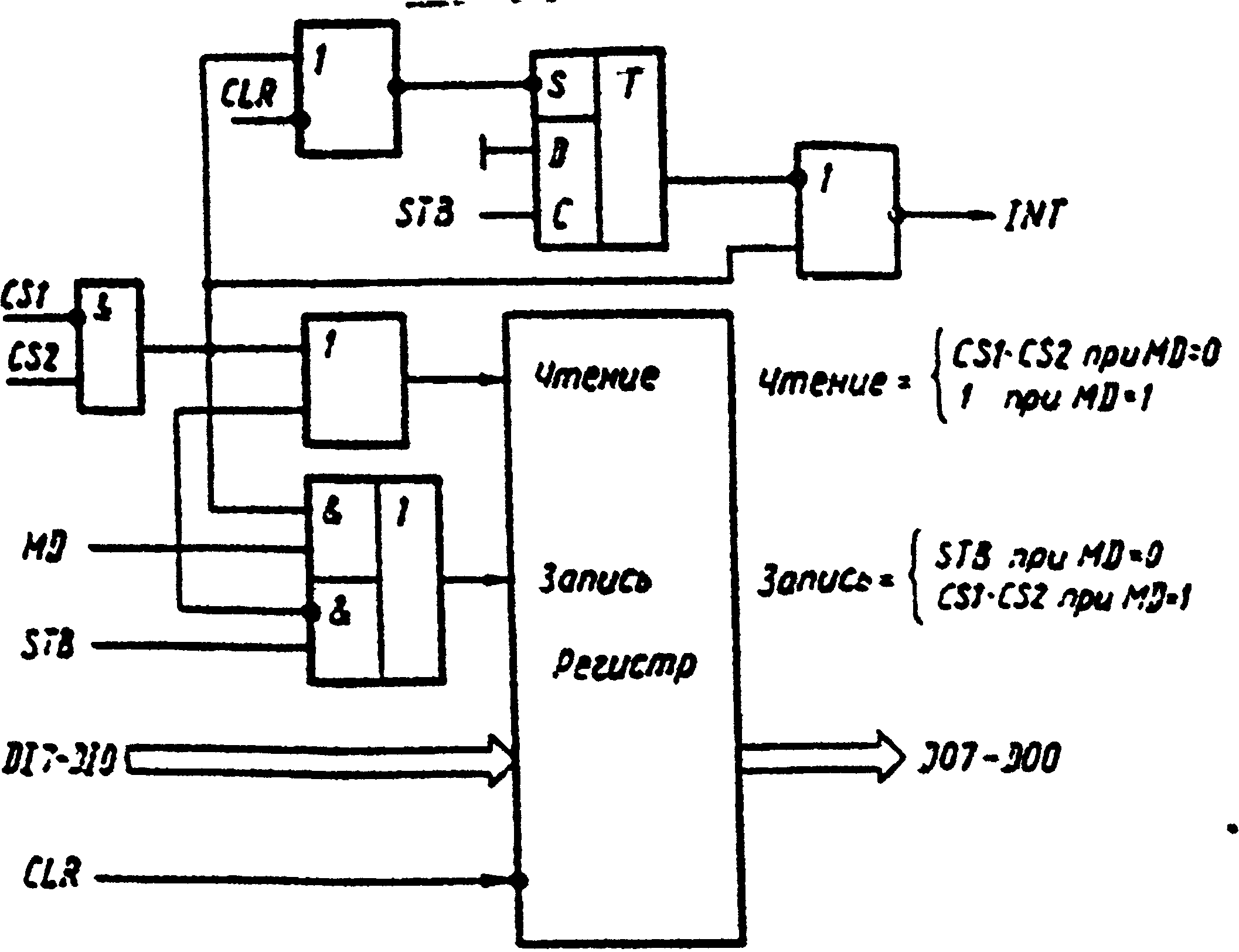

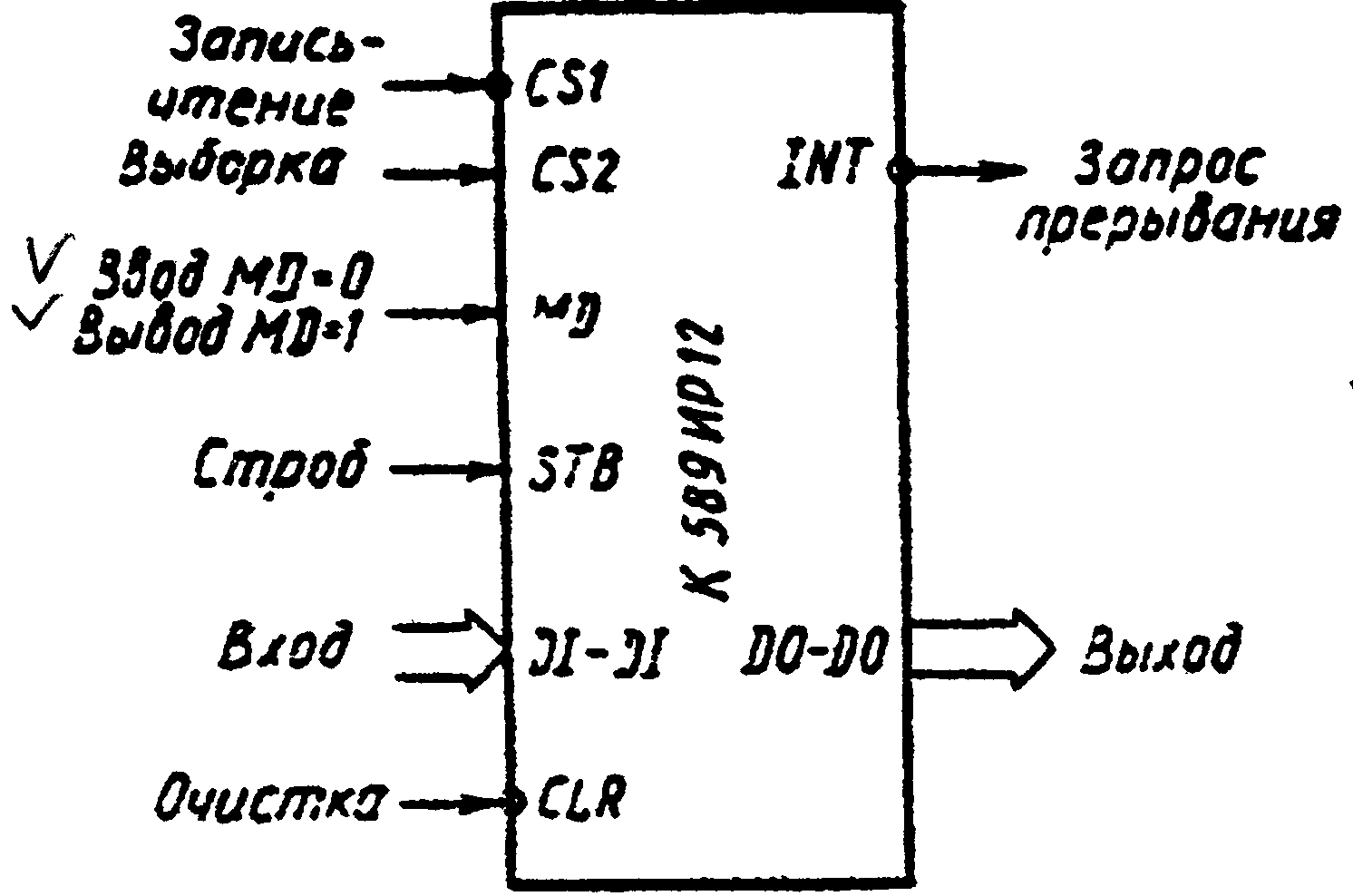

КР589ИР12 используется в качестве регистра состояния. Цоколевка, условное обозначение, функциональная схема и схема подключения представлена на рис. 2.18-2.21.

Микросхема

содержит восьмиразрядный регистр,

триггер прерываний Т и логические схемы

управления режимами работы. Регистр

имеет два режима работы, которые

определяются по состоянию входа MD.

Если MD=0,

то реализуется режим ввода; если MD=1,

то вывода. В режиме ввода информация с

входного канала DI7-DI0

по сигналу на входе STB.

Информация из регистра по выходному

каналу D00-D07

выдается по сигналам

-CS2.

-CS2.

Рис. 2.19. Условное обозначение микросхемы К589ИР12

Рис. 2.18. Цоколевка микросхемы К589ИР12

Рис. 2.20. Функциональная схема К589ИР12

Рис. 2.21. Схема подключения К589ИР12

В режиме вывода выходные формирователи открыты и выходная информация выдается в выходной канал постоянно. Запись информации в режиме вывода происходит по сигналам -CS2. Регистр может устанавливаться в нулевое положение при подаче сигнала «0» на вход очистки CLR. Т.е. запись информации в регистр описывается уравнением

.

.

Чтение информации

.

.

Триггер

прерывания принимает и хранит сигналы,

которые используются в качестве запросов

прерывания. Сигналы поступают на вход

синхронизации триггера со входа STB.

Запрос прерывания выдается через выход

INT.

В исходном состоянии сигналом очистка

на выходе INT

формируется «1», показывая на отсутствие

запросов прерывания. Под действием

сигнала на входе STB,

триггер устанавливается в «0», а на

выходе INT

появляется сигнал запроса нулевого

уровня. Сброс запроса прерывания

производится сигналами

-CS2.

В качестве регистра состояния данная

микросхема используется в структуре

центрального микропроцессора на рис.

2.27.

на выходе INT

формируется «1», показывая на отсутствие

запросов прерывания. Под действием

сигнала на входе STB,

триггер устанавливается в «0», а на

выходе INT

появляется сигнал запроса нулевого

уровня. Сброс запроса прерывания

производится сигналами

-CS2.

В качестве регистра состояния данная

микросхема используется в структуре

центрального микропроцессора на рис.

2.27.

Рис. 2.27. Структура центрального процессора на БИС КР580ВМ80А, К589, К155

Системные контроллеры

Для упрощения интерфейса центрального процессора разработаны специальные БИС системного контроллера КР580ВК28 и КР580ВК38. Они производят формирование выходных сигналов магистрали данных и сигналов системной шины управления (рис. 2.28).

Рис. 2.28. Микросхема КР580ВК28:

а - цоколевка; б - условное обозначение; в - функциональная схема; г - назначение выводов

Микросхема

содержит двунаправленный магистральный

формирователь Ф, регистр состояния РС

и схему формирования управляющих

сигналов СФУС. Схема формирования

управляется сигналами, подаваемыми на

входы DBIN,

HLDA,

с выходов МП и сигналом разрешения

магистрали, подаваемым на вход системы

прямого доступа к памяти (вход BUSEN).

Байт состояния запоминается по стробу

STSTB,

подаваемого на вход с одноименного

выхода тактового генератора КР580ГФ24.

Системный контроллер выполняет роль

буфера шины данных, регистра состояния

процессора (РС) и формирует сигналы

управления INTA

(подтверждения прерывания), MEMR

(чтение памяти), MEMW

(запись в память), IOR

(чтение внешнего устройства), IOW

(запись во внешнее устройство).

с выходов МП и сигналом разрешения

магистрали, подаваемым на вход системы

прямого доступа к памяти (вход BUSEN).

Байт состояния запоминается по стробу

STSTB,

подаваемого на вход с одноименного

выхода тактового генератора КР580ГФ24.

Системный контроллер выполняет роль

буфера шины данных, регистра состояния

процессора (РС) и формирует сигналы

управления INTA

(подтверждения прерывания), MEMR

(чтение памяти), MEMW

(запись в память), IOR

(чтение внешнего устройства), IOW

(запись во внешнее устройство).

Отличие

КР580ВК28 от системного контроллера

КР580ВК38 состоит в формировании сигналов

записи во внешнее устройство и в память

(IOW

и MEMW).

Микросхема КР580ВК28 формирует эти сигналы

относительно сигнала

(запись), а микросхема КР580ВК38 относительно

сигнала

(рис. 7.3). Это отличие позволяет при

применении контроллера КР580ВК38

использовать устройство памяти и портов

внешних устройств ввода/вывода с более

высоким быстродействием.

(рис. 7.3). Это отличие позволяет при

применении контроллера КР580ВК38

использовать устройство памяти и портов

внешних устройств ввода/вывода с более

высоким быстродействием.

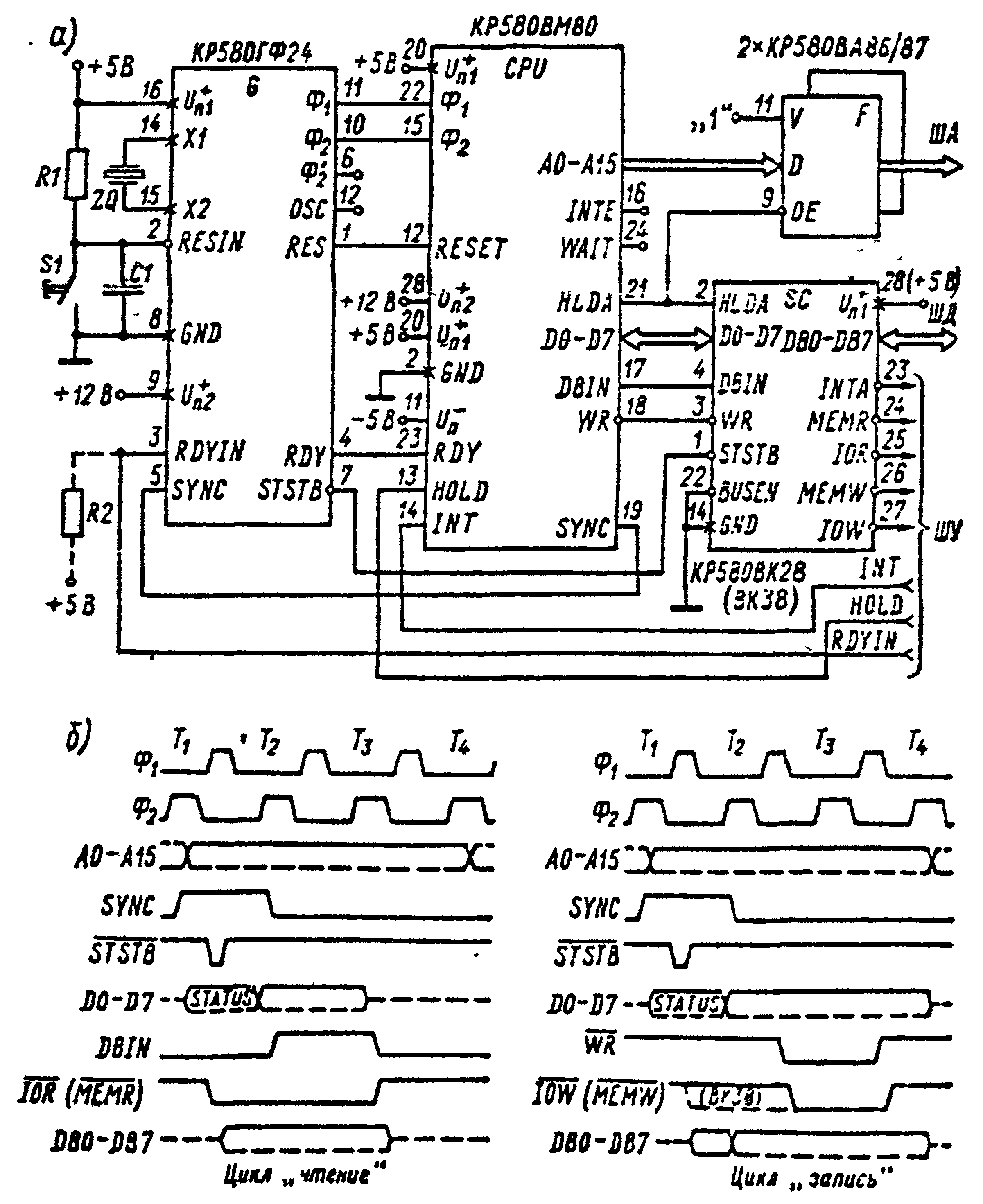

Рис. 7.3. Схема включения МП КР580ВМ80

}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}}

2) схемы подключения ЗУ

Как

правило, управляющие микропроцессорные

системы требуют значительный объем ПЗУ

и ОЗУ, которые используются для хранения

программ и записи результатов. Увеличение

числа подключенных микросхем памяти к

модулю МП достигается введением

дешифратора, на входы которого подаются

старшие адреса адресной шины. Выходы

дешифратора подключаются кА входам

выбора микросхем ( ).

Таким образом можно считать, что

физический адрес конкретной микросхемы

в микропроцессорной системе определяется

теми разрядами шины адреса, которые

обеспечивают появление сигнала

низкого уровня на соответствующем

выводе дополнительного адресного

дешифратора. При таком способе подключения

микросхем памяти к вычислительной

системе информация считывается из

запоминающего устройства на шину данных

сразу после установки микропроцессором

адреса этой микросхемы, что может

привести к конфликтным ситуациям на

шине данных. Этот дефект можно устранить

разными способами. Например, подают на

стробируемый код дешифратора сигнал

чтения MEMR

системного контроллера для ПЗУ или

сигнал записи для ОЗУ MEMW.

При этом сигнал выбор кристалла (

)

на соответствующем выходе дешифратора

будет сформирован в те моменты, когда

совпадает физический адрес выбираемой

микросхемы и сигнал чтения. В случае,

если в применяемом дешифраторе отсутствует

вход стробирования, формирование

сигналов может быть произведено с

помощью дополнительных элементов «ИЛИ».

).

Таким образом можно считать, что

физический адрес конкретной микросхемы

в микропроцессорной системе определяется

теми разрядами шины адреса, которые

обеспечивают появление сигнала

низкого уровня на соответствующем

выводе дополнительного адресного

дешифратора. При таком способе подключения

микросхем памяти к вычислительной

системе информация считывается из

запоминающего устройства на шину данных

сразу после установки микропроцессором

адреса этой микросхемы, что может

привести к конфликтным ситуациям на

шине данных. Этот дефект можно устранить

разными способами. Например, подают на

стробируемый код дешифратора сигнал

чтения MEMR

системного контроллера для ПЗУ или

сигнал записи для ОЗУ MEMW.

При этом сигнал выбор кристалла (

)

на соответствующем выходе дешифратора

будет сформирован в те моменты, когда

совпадает физический адрес выбираемой

микросхемы и сигнал чтения. В случае,

если в применяемом дешифраторе отсутствует

вход стробирования, формирование

сигналов может быть произведено с

помощью дополнительных элементов «ИЛИ».

Оперативная

память микропроцессорных систем строится

на основе запоминающих устройств с

произвольной выборкой. Микросхемы ОЗУ

подразделяются на статические и

динамические. В динамических

микросхемах ОЗУ периодически

необходимо обеспечить режим регенерации

памяти (подзаряд конденсатора элементарной

ячейки памяти). Это усложняет подключение

динамических запоминающих устройств

к микропроцессорной системе. Статические

ОЗУ

в свою очередь делятся на ЗУ с раздельным

входом и выходом и ЗУ с совмещенным

входом и выходом. Управление режимом

работы ЗУ с произвольной выборкой

происходит по входам R/ .

Высокий логический уровень на этом

входе означает, что данные будут

считываться, низкий - данные будут

записываться.

.

Высокий логический уровень на этом

входе означает, что данные будут

считываться, низкий - данные будут

записываться.

Выходы

микросхем ОЗУ не могут быть непосредственно

подключены к шине данных, т.к. управляющий

сигнал запись

,

определяющий режим работы микросхемы,

формируется системным контроллером

после того, как на магистрали адреса

появляется адрес к данной микросхеме

ОЗУ. Для предотвращения возможного

конфликта на шине данных между выходами

микросхемы и выходами микросхемы и

шиной данных включаются элементы с

тремя состояниями.

,

определяющий режим работы микросхемы,

формируется системным контроллером

после того, как на магистрали адреса

появляется адрес к данной микросхеме

ОЗУ. Для предотвращения возможного

конфликта на шине данных между выходами

микросхемы и выходами микросхемы и

шиной данных включаются элементы с

тремя состояниями.

Для

наращивания объема ОЗУ применяют

дополнительный адресный дешифратор.

Для статических ЗУ с произвольной

выборкой и совмещенными входами и

выходами используют дополнительный

входной сигнал

,

который обеспечивает подключение

внутренней шины данных к системе (с

помощью элементов «И», на входы которых

подаются сигналы

и

).

и

).

При построении модуля памяти возникает задача наращивания информационной емкости. При наращивании происходит:

расширение разрядности путем параллельного включения БИС. Микросхемы памяти объединяются по всем выводам, кроме информационных, которые в совокупности образуют расширенную информационную шину;

объединение по информационным входам/выходам. Еще объединяются все остальные входы за исключением входа выбор кристалла . Сигналы на этих входах определяют, какой из микросхем нужно включаться в работу (используется дешифратор адреса).

В случае, если используется микросхемы памяти имеющие n+1 адресных входов AN-A0, то для получения непрерывного поля физических адресов на дешифратор адреса должны быть поданы старшие адреса, начиная с адреса AN+1. Рассмотрим схему на рис. 2.19, а.

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

||

стробы DC |

позиционный код DC |

ПЗУ |

|||||||||||||||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

||

0 |

0 |

0 |

0 |

||||||||||||||

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

||

0 |

7 |

F |

F |

||||||||||||||

Таким образом, диапазон адресов ПЗУ 0000÷07FF.

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

||

стробы DC |

позиционный код DC |

ОЗУ |

|||||||||||||||

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

||

0 |

8 |

0 |

0 |

||||||||||||||

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

||

0 |

F |

F |

F |

||||||||||||||

Таким образом, диапазон адресов ПЗУ 0800÷0FFF.

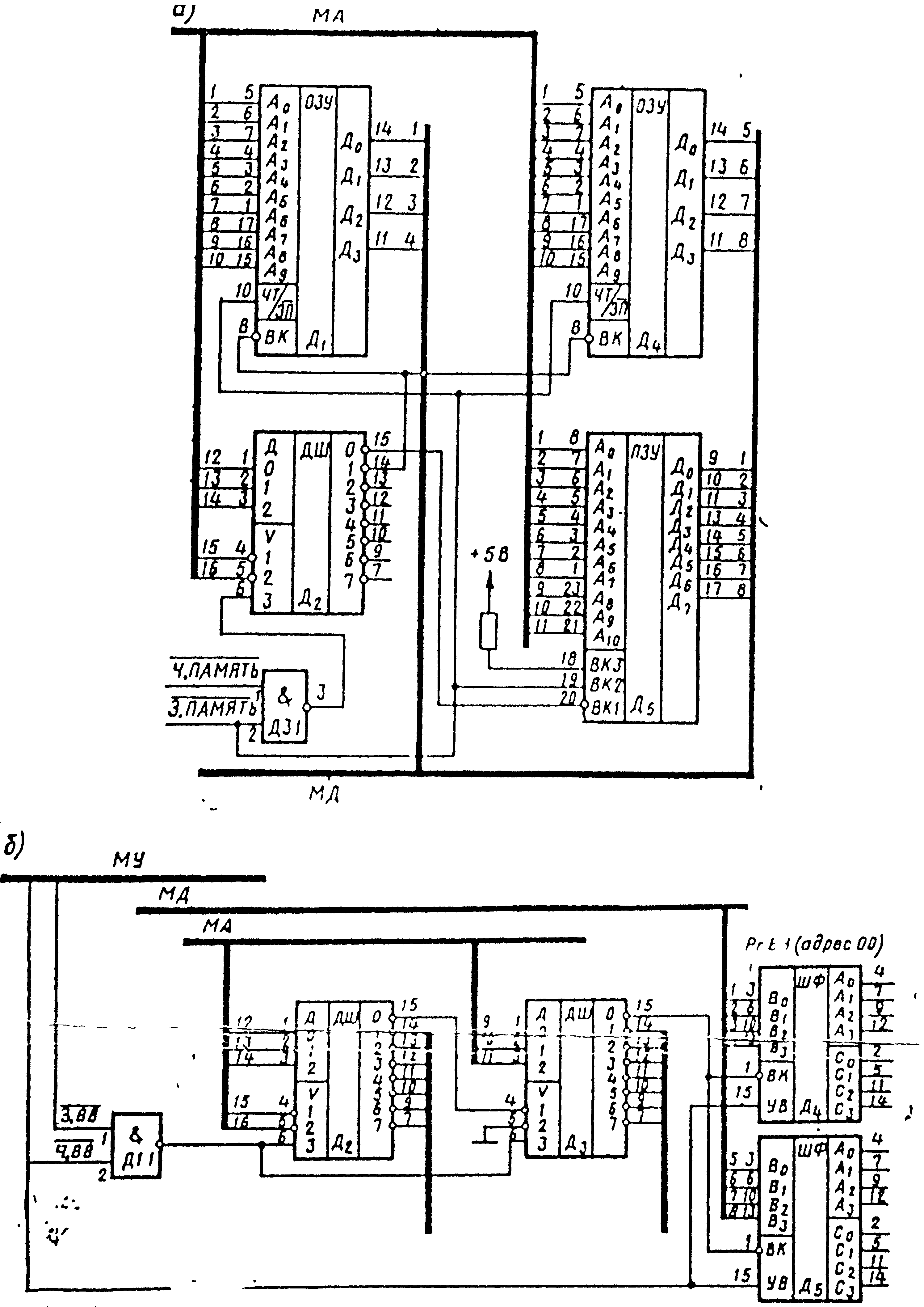

Рис. 2.19. Схема подключения памяти (а) и внешних устройств (б) к магистрали микроЭВМ

На рис. 2.19,а показан пример подключения микросхем ОЗУ и ПЗУ к магистралям ЭВМ. Дешифратор Д2 (К555ИД7) стробируется сигналом чтения памяти и запись в память и служит для выбора восьми областей памяти емкостью по 2 Кбайт и лежащих в диапазоне 0000÷3FFFH. Первую область(0000÷07FFH) занимает микросхема ПЗУ (Д5) емкостью 2 Кбайт, вторую (0800÷0FFFH) - микросхема ОЗУ (Д4) емкостью 1 Кбайт. К другим областям памяти микросхемы ОЗУ и ПЗУ подключаются аналогично.