- •Содержание

- •Переслать X байт по адресу y из порта z

- •Переслать X байт по адресу y в адрес z

- •Переслать X байт по адресу/в порт y из/в порт/память z

- •Организовать пдп пересылку X байт

- •Пример программы процессора со стековой организацией:

- •Пример программы процессора с аккумулятором:

- •Всякая каша

- •Лера скинула Билет 1

- •Билет 2

- •Билет 3

- •Билет 4

- •Билет 5

- •Билет 6

- •Билет 7

- •Билет 8

- •Билет 9

- •Билет 10

- •Сопроцессор

Пример программы процессора со стековой организацией:

FILD DWORD PTR[_d4_] ;загрузка целого. 4байт числа

FLD DWORD PTR[_d3_] ;загрузка веществ. 4байт числа

FLD QWORD PTR[_d2_] ;загрузка веществ. 8байт числа

FLD TWORD PTR[_d1_] ;загрузка веществ. 10байт числа

; ST0 = _d1_, ST1=_d2_, ST2=_d3_, ST3=_d4_

FADDP ST1,ST0 ;ST1=ST1+ST0, ST0 – выбрасывается из стека

; ST0 = _d1_+_d2_ , ST1=_d3_, ST2=_d4_

FSUB ST2,ST1 ;ST2=ST2-ST1

; ST0 = _d1_+_d2_ , ST1=_d3_, ST2=_d4_-_d3_

FMULP ST2,ST0 ;ST2=ST2*ST0, ST0 – выбрасывается из стека

; ST0=_d3_, ST1=(_d4_-_d3_)*(_d1_+_d2_)

FXCH ST1 ;ST1óST0

; ST0=(_d4_-_d3_)*(_d1_+_d2_) ,ST1=_d3_

FSCALE ;ST0=ST0^ST1

; ST0=((_d4_-_d3_)*(_d1_+_d2_))^_d3_ ,ST1=_d3_

FDIVP ST1,ST0 ;ST1=ST1/ST0, ST0 – выбрасывается из стека

; ST0=_d3_/(((_d4_-_d3_)*(_d1_+_d2_))^_d3_)

FSTP DWORD PTR[_res_] ;выгрузка веществ. 4байт числа

Пример программы процессора с аккумулятором:

MOV R0,#Y ;установить указатель памяти на адрес Y

MOV R1,#X ;кол-во пересылаемых байт

NEXT:

MOV A,P0 ;считать из порта 0 в аккумулятор

MOV @R0,A ;записать в память по адресу R0

INC R0 ;R0=R0+1

DJNZ R1,NEXT

Кому не лень скиньте в содержание

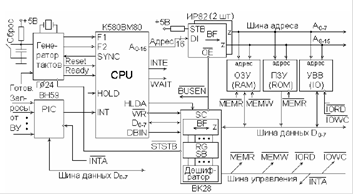

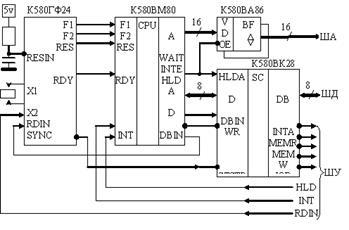

Всякая каша

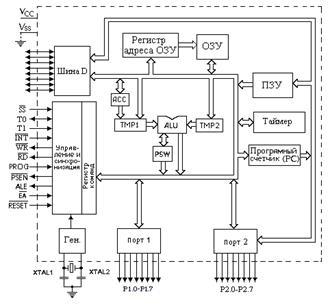

К580 -шина данных – 8 разрядов; - шина адресов – 12 разрядов; - адресное пространство – 212 = 4 кбайта; - внутреннее ПЗУ – 1 кбайт; - расширение ПЗУ – до 3 кбайт; - внутреннее ОЗУ – 64 байта; - внешнее ОЗУ – 256 байт (4 страницы по 64 байта); - команды - 1 или 2 байта; - тактовая частота fт - 6МГц; - прерывания - 2 уровня; - ввод-вывод данных – 3 порта. К580ГФ24 – генератор тактовых импульсов. К580ИР82 – буферный регистр. К580ВА86 – двунаправленный шинный формирователь. К580ВК28 – системный контроллер. К580ВК38 – системный контроллер. К580ВВ55 – программируемый параллельный интерфейс. К580ВВ51 – программируемый последовательный интерфейс. К580ВИ53 – программируемый таймер. К580ВИ54 – программируемый таймер. К580ВН59 – программируемые контроллеры прерываний. К580ВН59А – программируемые контроллеры прерываний. К580ВТ57 – программируемые контроллеры прямого доступа к памяти. К580ВТ37 – программируемые контроллеры прямого доступа к памяти. К580ВВ79 – программируемый контроллер клавиатуры и индикации. К580ВК91– приемопередатчики шины IEEE-488. К580ВК92 – контроллер шины IEEE-488.

|

|

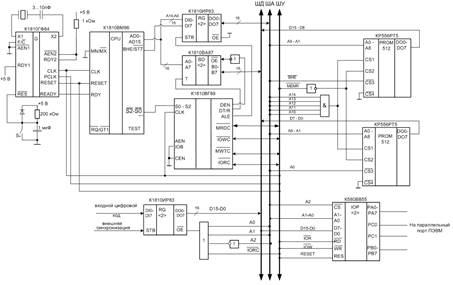

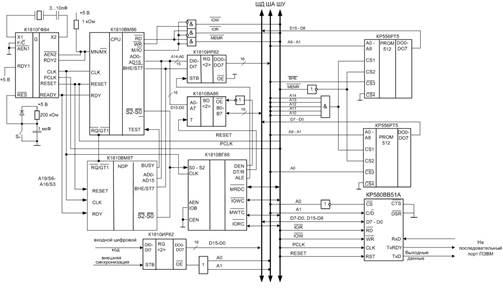

1810 Тактовая частота – 5МГц Разрядность– 16 Диапазон адресации – до 1 Мб для памяти, 64 Кб для устройств ввода-вывода Передача и адреса – по одной физической линии с мультиплексированием по времени (данные после адреса). В минимальном режиме микропроцессор формирует управляющие сигналы для памяти и устройств ввода-вывода, обеспечивая однопроцессорный режим работы. В максимальном режиме сигналы управления памятью и устройствами ввода-вывода формируются контроллером КР1810ВГ88 на основании информации о состоянии микропроцессора(S2-S0) Линии, используемые в минимальном режиме для управления памятью и устройствами ввода-вывода, в максимальном режиме обеспечивают аппаратную реализацию многопроцессорного режима работы. Сопроцессор i8087 представляет собой 40 –контактную БИС и предназначен для выполнения арифметических операций с плавающей запятой. При его отсутствии они выполняются программное Тактовый генератор К1810ГФ84 предназначен для формирования сигналов частотой 5 МГц, синхронизирующих работу микропроцессора К1810ВМ86, кроме того, формирует сигналы СБРОС и ГОТОВНОСТЬ. Буферные 8 разрядные регистры КР580ИР82 и ИР83 используются при демультиплексирования магистрали адреса– данных микропроцессора К1810ВМ86. Формирователи магистрали 8 – разрядные КР580ВА86 и ВА87 предназначены для обеспечения необходимой мощности интерфейсных сигналов, выходящих за пределы платы, они представляют собой биполярные приемопередатчики с трех стабильными выходами. Контроллер магистрали КР1810ВГ88 предназначен для декодирования байта состояния микропроцессора КМ1810ВМ89 или ВМ86 (в максимальном режиме), осуществляет генерацию во времени команд и управляющих сигналов для системной магистрали. Он также выдает сигнал стробирования адреса в буферные регистры ИР82 и ИР83 во время демультиплексирования адреса – данных от микропроцессора К1810ВМ86.

|

|

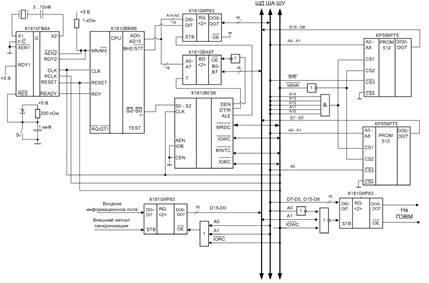

1816 шина данных – 8 разрядов; - шина адресов – 12 разрядов; - адресное пространство – 212 = 4 кбайта; - внутреннее ПЗУ – 1 кбайт; - расширение ПЗУ – до 3 кбайт; - внутреннее ОЗУ – 64 байта; - внешнее ОЗУ – 256 байт (4 страницы по 64 байта); - команды - 1 или 2 байта; - тактовая частота fт - 6МГц; - прерывания - 2 уровня; - ввод-вывод данных – 3 порта.

|

|

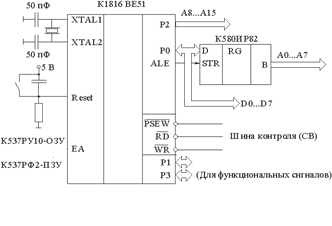

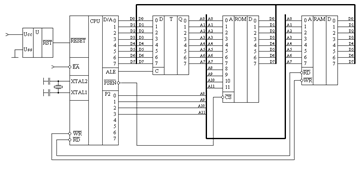

MCS48 Клон интел 8048 Подключение памяти |

|

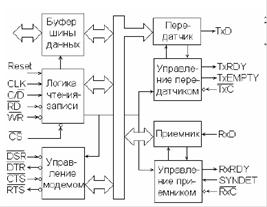

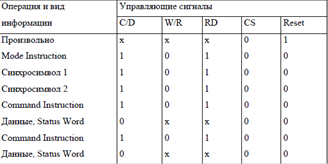

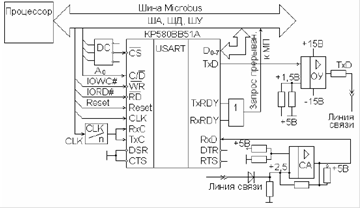

к580вв51А (псоледоваетльный порт) Универсальный синхронно-асинхронный приемо-передатчик В состав ВВ51 входят передатчик, приемник, буфер шины данных и схемы управления передатчиком, приемником, модемом. Основу передатчика составляет 13-разрядный сдвиговый регистр, хранящий очередной код передаваемого символа. Разряды 12 и 11 регистра используются для формирования стоп-битов, 10 – для записи контрольного бита, разряды 9 – 2 – для хранения данных, 1 – для формирования старт-битов, последний разряд 0 используется как выходной буфер. Схема управления передатчиком отслеживает прием новых данных, добавляет к ним контрольный бит, старт-бит, стоповый бит и синхронизирует вывод из регистра сдвига в линию TxD(Transm Data) Приемник состоит из входного формирователя, двух 9-разрядных регистров сдвига, двух регистров для хранения синхросимволов, схемы управления и схемы синхронизации. Информация со входа RxD (Resiver Data) последовательно поступает через входной буфер и далее в регистры сдвига. Управление записью входной информации осуществляется схемой управления приемником, содержащей логику формирования синхроимпуьсов приема, счетчик числа принятых битов, схему контроля четности, триггер ошибки четности РЕ, триггер ошибки кадра FE и триггер ошибки переполнения ОЕ Буфер шины данных представляет собой 8-разрядный трехстабильный двунаправленный буфер, обеспечивает связь УСАПП с МПС. Логика чтения записи содержит регистр режима и регистр команд. Регистр режима служит для хранения управляющего слова выбора режима MI, а регистр команд для приема командной инструкции CI. Схема управления модемом служит для обмена с ПУ управляющими сигналами: DSR (Data Set Ready). Готовность приемника модема проверяется программно. DTR (Data Terminal Ready). Запрос готовности приемника модема. Управляется программно. RTS (Reguest To Send). Запрос готовности передатчика модема.Управляется программно. CTS (Clear To Send). Готовность передатчика модема. Разрешает УСАПП передачу данных. Входные сигналы WR и RD определяют направление потока информации, передаваемой шине данных из ЦП в УСАПП и обратно. Логический уровень на входе С/D=1 – запись или считывание управляющих слов, а при С/D=0 запись или считывание данных. Все операции по обмену информацией возможны только при CS=0, т. е. когда микросхема выбрана. Перед началом работы УСАПП необходимо установить в исходное состояние системным сигналом Reset либо программным способом с помощью команды IR=1 (бит D6 в командной инструкции CI). Дальнейшее управление работой УСАПП осуществляется двумя управляющими словами: MI (Mode Instruction) и CI (Command Instruction) в соответствии с таблицей |

|

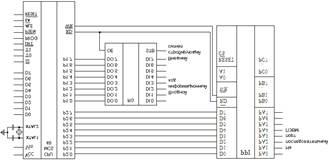

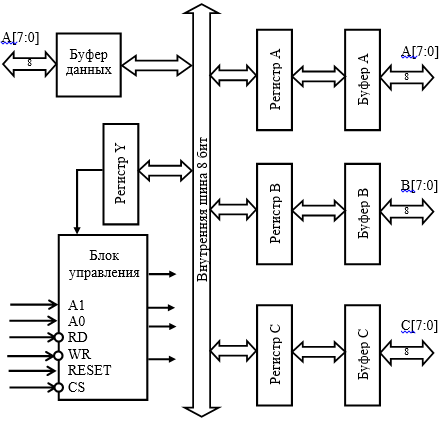

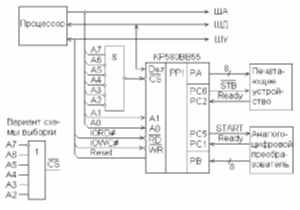

к580вв55 Периферийный для параллельного обмена информацией входят три двунаправленных 8-разрядных порта, разделенных на две группы, два устройства управления группами портов, и периферийная логика для согласования с системной шиной. Обмен информацией между МП и внутренними регистрами ВВ55 осуществляется через двунаправленный шинный формирователь и управляется сигналами CS, A0, A1, RD, WR)

Можно запрограммировать на следующие режимы работы ее портов: режим 0 – однонаправленный ВВ без квитирования (применим к любому из портов); режим 1 – однонаправленный ввод-вывод с квитированием (применим к портам А и В); режим 2 – двунаправленный ВВ (только для порта А). В режиме 0 осуществляется прямой однонаправленный обмен через любой из трех портов без сигналов сопровождения. В данном режиме порты А и В можно представить, как две параллельные шины размером в один байт, а порт С– как две 4-разрядные параллельные шины. При этом каждую из указанных шин можно устанавливать на ввод или вывод независимо от других. Входные данные в микросхеме ВВ55 не запоминаются и читаются при низком уровне сигнала на входе RD Режим 1 обеспечивает однонаправленный обмен данными с квитированием через порты А и В. Входные и выходные данные фиксируются во внутренних регистрах портов А и В. Управление вводом осуществляется сигналами: STB (Strobe). Строб записи данных во входной регистр-защелку. Запись осуществляется по фронту STB. IBF (Input Buffer Full). Подтверждение загрузки данных. INT (Interrupt). Запрос на прерывание OBF (Output Buffer Full). Строб вывода новых данных АСК (АСКnowledge). Подтверждение приема выходных данных со стороны ВУ. В режиме 2 линии РА7-РАО исполняют роль двунаправленной трех стабильной шины, управляемой сигналами STB, IBF, OBF, ACK и INT. Сигналы IBF или OBF информируют ВУ о готовности принять или передать данные. В соответствии с состоянием IBF или OBF внешнее ПУ либо генерирует очередные данные, сопровождая их стробом STB, либо формирует сигнал подтверждения приема АСК, готовясь к приему данных. Низкий уровень сигнала АСК открывает выходные буферы порта А, разрешая выдачу данных на шину. В остальных случаях шина порта А находится в Z-состоянии.

|

|

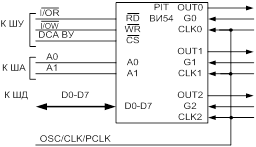

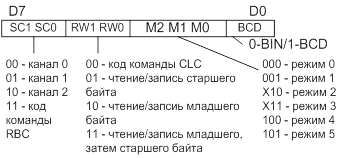

К1810ВИ54 Программируемый таймер Тактовая частота до 8 Мгц Содержит три независимых канала, каждый из которых может быть запрограммирован на работу в одном из шести режимов для двоичного или двоично-десятичного счета. содержит: буфер шины данных (BD) и логические схемы управления чтени- ем/записью; дешифратор DS, с помощью которого выбирается один из трех ка- налов либо формируется признак загрузки управляющих слов или команд; три идентичных канала COUNT2-COUNT0, реализующих запро- граммированную функцию. Каждый канал содержит: 16-разрядный буферный регистр OL, служащий для запоминания и хранения мгновенного значения счетчика CE, которое в любое время может быть записано командой Защелка или Чтение состояния канала. После выполнения этих команд содержимое OL может быть считано в ЦП без остановки дальнейшего счета в регистре CE; 16-разрядный счетчик/таймер CE, работающий в режиме вычитания. Изменение содержимого CE осуществляется по срезу сигнала CLK при GATE=1; 16-разрядный регистр констант пересчета CR, служащий для хранения констант пересчета. Содержимое CR загружается в CE для счета в зависимости от запрограммированного режима; 8-разрядный регистр состояния канала RS, содержимое которого можно считывать в ЦП с помощью команды RBC – Чтение состояния канала. Содер- жимое этого регистра является словом состояния канала 8-разрядный регистр управляющего слова RSW, предназначенный для его хранения. Слово загружается в RCW командой OUT с адресом, формирующим на входах А0, А11 код 11. Выбор конкретного канала осуществляется с помощью двух старших разрядов самого управляющего слова. Схема управляющей логики канала CL осуществляет управление входом/выходом счетчика/таймера в зависимости от запрограммированного режима. |

|

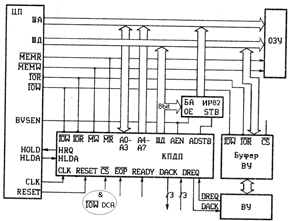

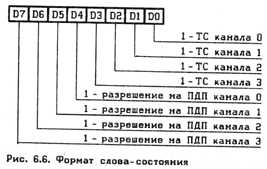

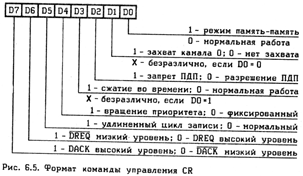

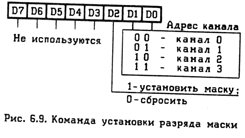

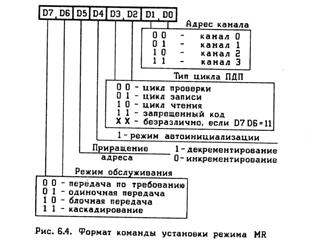

Контроллер Прямой доступ в память Режим ПДП является самым скоростным способом обмена, который реализуется с помощью специальных аппаратных средств – контроллеров ПДП без использования программного обеспечения. Для осуществления режима ПДП контроллер должен выполнить ряд последовательных операций 1) принять запрос DREQ на ПДП от ВУ; 2) сформировать запрос HRQ на захват шин для ЦП; 3) принять сигнал HLDA, подтверждающий этот факт после того, как ЦП вой- дет в состояние захвата (ШД, ША, ШУ в z-состояние); 4) сформировать сигнал DACK, сообщающий ВУ о начале выполнения циклов ПДП; 5) сформировать на ША адрес ячейки памяти, предназначенный для обмена; 6) выработать сигналы MR, IOW и MW, IOR, обеспечивающие управление обменом; 7) по окончании цикла ПДП либо повторить цикл ПДП, изменив адрес, либо прекратить ПДП, снятием запроса на ПДП. Циклы ПДП выполняются с последовательно расположенными ячейками памяти, поэтому контроллер ПДП должен иметь счетчик адреса ОЗУ. Число циклов ПДП определяется специальным счетчиком. Управление обменом осуществляется специальной логической схемой, формирующей в зависимости от типа обмена пары управляющих сигналов: MR, IOW (циклы чтения), MW, IOR (циклы записи). Из изложенного следует, что контроллер ПДП по запросу должен взять на себя управление системными шинами и выполнять совмещенные циклы чтения/вывода или записи/ввода до тех пор, пока содержимое счетчика циклов ПДП не будет равно нулю. Структура КПДП Контроллер включает четыре канала, каждый из которых состоит из четырех 16-разрядных регистров. Регистр текущего адреса CAR хранит текущий адрес ячейки памяти при выполнении цикла ПДП. После выполнения цикла ПДП содержимое этого регистра увеличивается или уменьшается на единицу. Оно может быть прочитано или загружено с помощью двух команд ввода/вывода. Содержимое CAR может быть обновлено по сигналу EOP, если запрограммирован режим авто инициализации. Регистр циклов ПДП CWR хранит число слов, предназначенных для передачи. При загрузке этого регистра необходимо помнить, что загружаемая константа должна быть на единицу больше числа слов, необходимых для пере- дачи. При выполнении циклов ПДП регистр работает в режиме вычитающего счетчика. Разряд TC регистра состояния устанавливается в единицу при пере- ходе из нулевого состояния в состояние FFFFH. Чтение и запись содержимого регистра осуществляется двумя последовательно выполняемыми командами ввода – вывода. Содержимое CWR может быть обновлено при авто инициализации по сигналу EOP либо в регистре сохраняется значение FFFFH. Регистр хранения базового адреса BAR и регистр хранения базового числа циклов ПДП WCR хранят базовые значения адреса и числа циклов ПДП, участвуют в авто инициализации. При начальной загрузке контроллера ПДП исходными параметрами происходит одновременная запись в регистры CAR, BAR, CWR и WCR. В процессе выполнения циклов ПДП содержимое BAR и WCR не изменяется. Прочитать состояние этих регистров невозможно. Кроме того, каждый канал имеет 6-разрядный регистр режима MR, определяющий режим его работы. При загрузке этого регистра в младших разрядах D1, D0 указывается код номера канала.

Назначение выводов КПДП. CLK – вход для подключения тактового генератора FCLK=3 МГц. CS – выбор кристалла. CS = 0 разрешает работу КПДП. RESET – сброс. Сигнал высокого уровня переводит КПДП в исходное состояние, устанавливая в нуль регистры команд, условий, временного хранения, а также устанавливая в единицу все разряды маски. READY – готовность. Входной сигнал, используемый для синхронизации работы КПДП с медленнодействующими устройствами. HLDA – подтверждение захвата. Входной сигнал, используемый ЦП для сооб- щения КПДП о возможности выполнения циклов ПДП DREQ3 – DREQ0 – входы запросов на ПДП от внешних устройств. Полярность запросов задается программно. Сигналы на этих входах должны удерживаться до прихода сигнала DACK. В исходном состоянии приоритет запросов естест- венный , DREQ0 имеет наивысший приоритет. DB7 – DB0 – двунаправленная шина данных с буфером, имеющим z-состояние. В циклах ПДП на эти линии выдается восемь старших разрядов адресного кода, которые необходимо «защелкнуть» на внешнем регистре сигналом ADSTB. В режиме работы с ЦП по этим линиям осуществляется прием/передача данных. IOR – чтение; как вход используется ЦП для чтения содержимого внутренних регистров КПДП; как выход в режиме ПДП разрешает выдачу данных из внеш- них устройств. IOW – запись; как вход используется ЦП для загрузки данных в регистры КПДП; как выход в режиме ПДП разрешает запись данных в регистры внешних устройств. EOP – окончание процесса. Вход/выход, используемый для указания окончания процесса передачи данных в режиме ПДП. А3 – А0 – адресные входы/выходы. Используются как входные в режиме рабо- ты с ЦП и для адресации к каналам и регистрам каналов КПДП. В режиме ПДП являются выходами, по которым передаются четыре младших разряда адреса ОЗУ. А7 – А4 – адресные выходы, на которые в режиме ПДП передаются соответст- вующие разряды адреса ОЗУ. В режиме работы с ЦП переходят в z-состояние. HRQ – выход запроса захвата шин. Запрос к ЦП для перехода в режим ПДП. DACK3 – DACK0 – подтверждение ПДП. Выходные линии, на которые выда- ются сообщения для ВУ о возможности выполнения циклов ПДП. Полярность сигнала задается программно. После сигнала RESET на выходах DACK уста- навливается нуль. AEN – разрешение адреса. AEN=1 устанавливается на время выдачи восьми старших разрядов адреса ОЗУ на линии DB7 – DB0. ADSTB – строб адреса. Выход, на котором формируется импульс (строб), осу- ществляющий запись старших разрядов (А15 – А8) адреса ОЗУ с шин DB7 – DB0 во внешний буферный регистр. MEMR – чтение из памяти. Выход, используемый в режиме ПДП для управле- ния операцией чтения из памяти. MEMW – запись в память. Выход, используемый в режиме ПДП для управле- ния операцией записи в память. Ucc – шина питания (+5 В). |

|

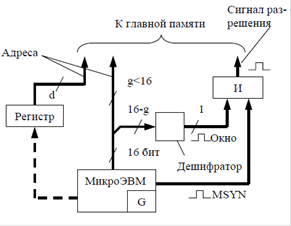

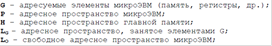

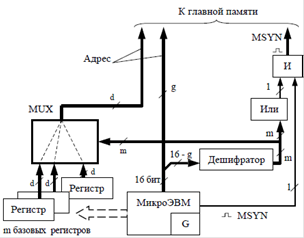

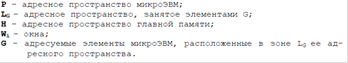

расшир.адр.пространства. Метод Окна Отображении на большом отрезке лишь части малого отрезка. Ёмкость главной памяти V = 2^d+g называется окном. Пример, d = 8, g = 12, то V = 2^20 = 1М ячеек Память можно рассматривать как состоящую из 2d (число проекций окна) страниц, каждая из которых имеет размер 2g ячеек, совпадающий с размером окна Адресная шина расщепляется на две части: одна поступает в главную память, а другая “поглощается” дешифратором. 1.Процессор загружает программно-доступный регистр старших разрядов адреса с шины данных, задавая положение проекции окна в адресном пространстве главной памяти 2. Процессор обращается по некоторому адресу, лежащему внутри окна. 3. Дешифратор опознает принадлежность текущего адреса фиксированному окну и разрешает передачу в главную память сигналов сопровождения адреса MSYN. В главную память выдается полный адрес (d+g бит), определяющий одну из ее ячеек. 4. Выбранная ячейка главной памяти выдает, или принимает информацию в зависимости от сигнала на линии управления режимом работы и посылает сигнал по линии передачи ответа. Недостатком такого метода является то, что при нем теряется часть оперативной памяти. Таким образом, в качестве оперативной памяти можно использовать только часть LG. Поскольку окно выбрано в зоне неиспользуемых адресов внутреннего адресного пространства микроЭВМ, то конфликты, связанные с одновре менным выбором двух адресуемых элементов, исключаются. |

|

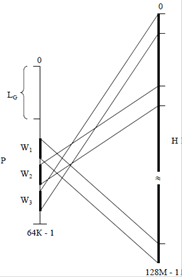

расшир.адр.пространства. Метод базовых регистров Базовые регистры – это регистры старших разрядов. Метод базовых регистров является обобщением метода окон. В адресном пространстве выделяется не одно, а несколько окон. При каждом обращении в главную память используется лишь одно окно. Проекции окон на “ось” главной памяти могут лежать в произвольных местах этой оси и, в частности, могут совпадать. Положение окон в адресном пространстве задается жестко с помощью дешифратора. Углы наклона лучей задаются содержимым базовых регистров. Размеры окон для простоты считают одинаковыми. 1.Процессор загружает программно-доступный регистр старших разрядов адреса с шины данных, задавая положение проекции окна в адресном пространстве главной памяти 2. Процессор обращается по некоторому адресу, лежащему внутри окна. 3. Дешифратор опознает принадлежность текущего адреса фиксированному окну и разрешает передачу в главную память сигналов сопровождения адреса MSYN. В главную память выдается полный адрес (d+g бит), определяющий одну из ее ячеек. 4. Выбранная ячейка главной памяти выдает, или принимает информацию в зависимости от сигнала на линии управления режимом работы и посылает сигнал по линии передачи ответа. Достоинство Метод базовых регистров позволяет переносить в адресное пространство одновременно несколько различных страниц главной памяти. В данном методе существенно то, что определен многозадачный режим работы, т.е. возможна организация, когда одна задача принимает данные, другая – обрабатывает и т.д. При обращении в главную память через одно из m окон дешифратор формирует сигнал выдачи старших разрядов с соответствующего базового регистра через мультиплексор. Недостаток Старшие разряды адреса из внешнего регистра “подстыковываются” к младшим, выдаваемымнепосредственно с части16-разрядной адресной шины. При такой “подстыковке” проекции окон в адресном пространстве главной памяти могут перемещаться с шагом, равным размеру окна. Для более плавного перемещения проекций вместо под- стыковки используется аппаратное арифметическое суммирование содержи мого базового регистра с кодом, выдаваемым в адресную шину. Старшие разряды кода, выдаваемого в 16-разрядную адресную шину, как и примерах, “поглощаются” дешифратором и не участвуют в формировании арифметической суммы. Увеличение разрядности полного физического адреса с увеличением n, однако, сопровождается уменьшением плавности перемещения проекций при отображении адресных пространств. Так, при n = 0 суммирование затрагивает все разряды обоих кодов, в том числе и самые младшие. Поэтому, изменяя на единицу младшего разряда содержимое сегментного регистра, можно перемещать отображаемый массив с дискретного в одну ячейку. При n = 1 суммирование в самых младших разрядах не произво- дится, поэтому перемещение кода из счетчика адреса команды в расши- ренное адресное пространство возможно только по четным или нечетным адресам. Аналогично при n = 2 дискретность перемещения составляет 4 ячейки, при n = 3 – 8 ячеек и т.д. |

|

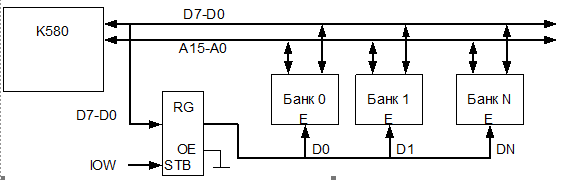

расшир.адр.пространства. Метод Банков Под термином банк подразумевается отдельный блок памяти, содержащий, возможно, как оперативную, так и постоянную части. Помимо обычных магистральных входов-выходов такой блок может иметь допол- нительный управляющий вход E разрешения работы. В процессе работы такой системы процессор микроЭВМ через программно-доступный регистр открывает нужный банк и использует информацию, которая в нем содержится. Остальные банки логически отключены от магистрали. Достоинства В данном методе существенно то, что микроЭВМ может вообще не содержать оперативной памяти. Она может вставлять в свое адресное пространство емкостью, например, 64К банки емкостью 56К, оставляя последние 8К ячеек для собственных нужд, в частности для адресации регистра. Такая подстановка оказывается удобной для быстрого переключения микроЭВМ с решения одной задачи на решение другой. Каждой задаче может соответствовать свой банк. Недостатки При этом, однако, в каж- дом банке должны храниться одни и те же резидентные программы операционной системы, что снижает эффективность использования памяти в целом. разрывность памяти, собранной из отдельных банков, невозможность одновременной работы с несколькими банками (с целью, например, быстрой переписи информации с одного банка на другой), а также сложность доступа к этой памяти со стороны каналов прямого доступа в память. Достоинства Если банки выполнены в виде ПЗУ, то адрес регистра (доступного только по записи) может совпадать с адресом одной из ячеек области адресного пространства, отведенного для размещения в ней банков. Например, если банки ПЗУ “вставляются” в область 8000-BFFF адресного пространства микроЭВМ, то регистру можно присвоить адрес 8000. Этот адрес будет соответствовать двум разным элементам – регистру и ячейкеПЗУ. При выполнении операции считывания по адресу 8000 информация будет выдана на шину данных только из ячейки ПЗУ, так как схема выдачи информации в эту шину из регистра не предусмотрена. При выполнении операции записи по этому адресу информация загружается в регистр, а ПЗУ остается в пассивном состоянии, так как оно не срабатывает при наличии сигнала Запись. Этот прием может быть полезным и в иных случаях, когда необходимо экономить адресное пространство. Например, адреса портов ввода (дос- тупных только по чтению) и вывода (доступных только по записи) можно выбрать одинаковыми. При этом сигнал на управляющей линии “Запись” служит как бы дополнительным разрядом адреса, выбирающим тот или иной порт.

|

|

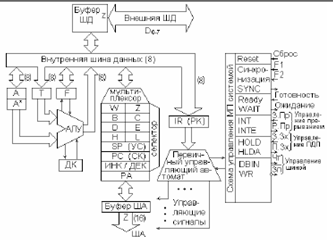

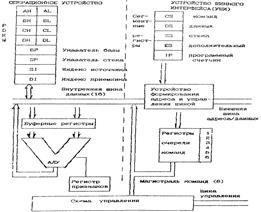

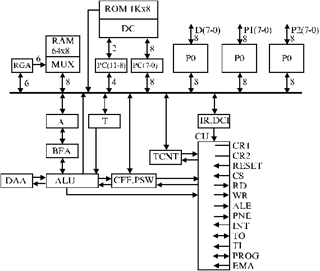

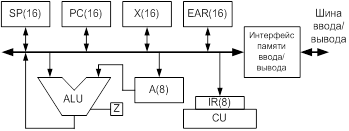

Типовые структуры процессора С аккумулятором Обращение к памяти 216 = 65536 байт Длина адреса 2 байта. Команды процессора 1,2 или 3 байта. Регистр команд IR 8 разрядный, в нем хранится 1-ый байт выполняемой команды. Регистр исполнительного адреса EAR 16-ти разрядный, содержащий адрес памяти, по которому во время выполнения команды процессор считывает из памяти или записывает в память операнд. Счетчик команды РС - 16-ти разрядный регистр, где находится адрес следующей, подлежащей к выполнению команды. Аккумулятор А - 8-ми разрядный регистр, в котором размещены данные, подлежащие обработке. Индексный регистр Х - 16-ти разрядный регистр, содержащий адрес или 16-ти битовые данные, которые используются программой. Указатель стека SP 16-ти разрядный регистр, содержащий адрес верхушки стека адресов возврата, организованного в памяти. Регистр нуля Z - одноразрядный регистр (триггер), который при выполнении любой команды оперирующей данными устанавливается процессором в 1, если команда приводит к получению нуля или записывается 0, если результат не 0. АЛУ производит операции над 2-мя 8-ми разрядными величинами, с целью получения 8-ми разрядного результата. команды непосредственно оперируют только регистрами PC, A, X, и Z содержимое которых имеет существенное значение после выполнения каждой команды. Указанные регистры определяют состояние процессора и используются при программировании, только они доступны программисту.

|

|

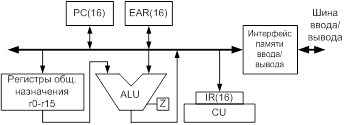

Типовые структуры процессора С регистрами общего назначения В таких процессорах арифметические и логические операции, передача данных, производится с использованием наборов регистров общего назначения. Любой из этих регистров можно использовать для хранения данных, необходимых для выполнения команды или для задания данных. Обычно процессоры имеют 8 или 16 РОНов, длина которых от 16 до 32 разрядов Длина IR 16 разрядов. Отсутствует указатель стека и индексный регистр. Вместо аккумулятора имеется 16 16-ти разрядных РОНов R0-R15. В этом процессоре функцию указателя стека реализует регистр R15 Т.к. длина адресного слова = 16-ти разрядам, то объем адресуемой памяти = 64 К. Арифметические и логические операции, а так же передача данных могут выполняться над словами с использованием 16-ти разрядного регистра, и над байтами с использование половины регистра. При операциях над байтами первые 8 16-ти разрядных регистров служат в качестве 16-ти 8-ми разрядных регистров. В то время как последние восемь 16-ти разрядных регистров остаются не использованными при операциях над байтами. Преимущества: более высокое быстродействие, чем у процессора с аккумулятором за счет уменьшения количества пересылок в память.

|

|

Типовые структуры процессора Со стековой организацией В процессорах со стековой организацией нет ни регистров общего назначения, ни аккумуляторов. А имеется указатель стека, который задает стек, организованный в памяти. Все команды в таком процессоре выполняются с участием стека. Арифметические сопроцессоры имеют стековую организацию. Большинство процессоров, как с аккумуляторами, так и с регистрами общего назначения, имеют хотя бы несколько команд работы со стеком. Для программирования используются регистры X, SP, PC, Z Регистр temp не доступен программисту, он служит для временного хранения операнда при выполнении каждой команды. ЭВМ имеет память с побайтовой адресацией емкостью 64К. Меньшие адреса используются для программы данных, старшие для стека. Начальное положение указателя стека FFFE. Рассматриваемые далее команды служат для выполнения операций только над 16-ти разрядными данными. Индексный регистр Х обычно содержит адрес ячейки памяти, находящийся внутри стека. Область памяти рядом с этой ячейкой называется кадром стека, поэтому индексный регистр можно называть указателем кадра стека, который обозначается SP. Преимущества: простота функциональной организации, дешевизна. В данной структуре могут быть: загрузка регистров, однооперандные команды преобразования аккумулятора, арифметические и логические операции между памятью и регистром, условный и безусловный переход, установка флага Z в 0 или1, команда вызова подпрограмм и возвращение в основную программу. Главный недостаток: большое количество пересылок процессов в память, что снижает быстродействие. Эту проблему устраняют регистры общего назначения.

|

|

Типовые способы адресации Однокомпонентные способы Исполнительный адрес задается единственным значением в команде или регистре. Многокомпонентные способы адресации Для полученья компонент адреса комбинируют значения, указанные в команде, с содержимым одного или нескольких регистров.

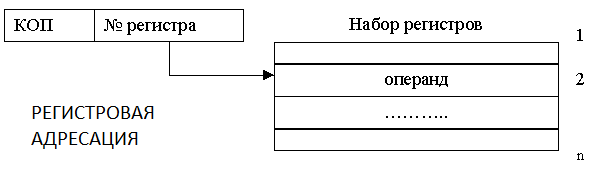

Регистровая адресация. Операнд хранится в одном из регистров процессора.

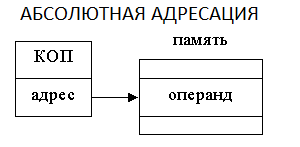

Абсолютная адресация. Для указания полного адреса является производят включение его в качестве составной части команды. Она обеспечивает гибкость работы, позволяет указывать любую ячейку памяти в адресном пространстве ЭВМ. Используются много разрядов в коде команды. Для сокращения числа разрядов в некоторых ЭВМ используется короткая абсолютная адресация, позволяющая осуществить прямой доступ к ограниченной части адресного пространства ЭВМ

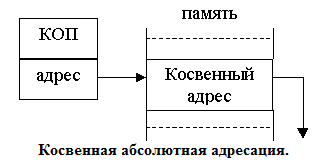

Косвенная абсолютная адресация. При этом способе адресации в качестве исполнительного адреса используется содержимое ячейки памяти, заданной абсолютным адресом.

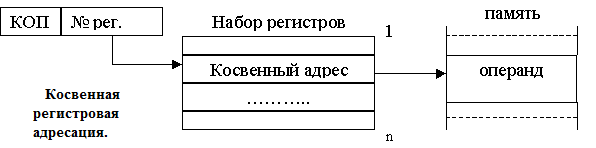

Косвенная регистровая адресация. Регистр или пара регистров содержат исполнительный адрес операнда. Дает возможность вычислять адреса памяти во время выполнения программы, а не запоминать их при трансляции. Вычисление адреса требуется для выполнения общих операций, таких как передача параметров определенного типа в подпрограмму и обращение к произвольным данным в массивах, списках, очередях, связанных списках и структурах.

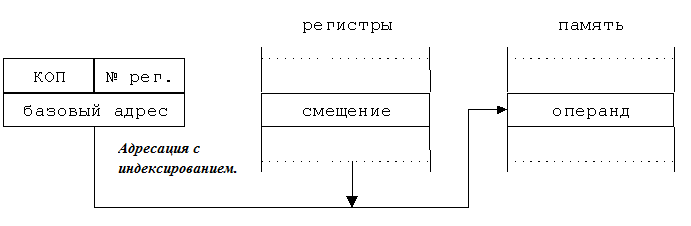

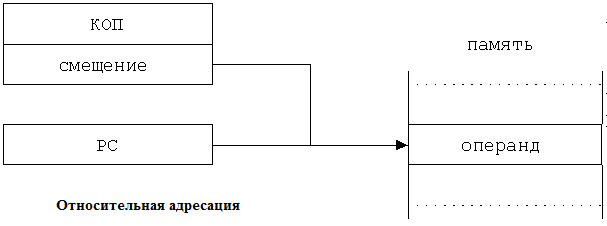

Адресация с индексированием. При этом способе адресации с индексированием 2 компонента объединяются путем сложения. Этот способ является удобным средством организации доступа к массивам и таблицам. Составной частью команды является фиксированный базовый адрес, затем указанное в адресном регистре смещение или индекс прибавляется к базовому адресу, чтобы формировать требуемый исполнительный адрес. Относительная адресация Адресация, при организации которой исполнительный адрес вычисляется как сумма фиксированного смещения в команде и текущего значения счетчика команд. При короткой относительной адресации используются смещения небольшой величины для указания адреса команд, находящихся недалеко от текущей команды. На рисунке показана короткая относительная адресация. Когда выполняется сложение с содержимым РС, последний уже указывает очередную команду. При короткой относительной адресации в команде перехода можно указывать адрес использующей меньшее количество разрядов. Данный способ дает возможность создавать позиционно-независимую программу.

|

|