- •69. Универсальный счетчик ис к155ие5. Выходы. Режимы работы

- •75. Триггеры. Общие понятия. Назначение выводов.

- •76. Синхронный rs-триггер.Клс.Работа

- •77. Определение частоты и периода периодического сигнала. Пример

- •84. Регистры сдвига. Общие понятия. Пример цифровой схемы с использованием регистра сдвига.

- •85.Запоминающие устройства. Общие понятия. Операции считывания и записи в зу.

- •86.Параллельный регистр сдвига. Работа.

- •2. Пзу, основанные на оптическом принципе хранения информации.

- •3. Пзу, основанные на электрическом принципе хранения информации.

- •97. Интегральный шифратор к555ив3. Назначение выводов. Режимы работы

- •1 10. Ис к155ру2. Процедура чтения из памяти. Пример

- •111. Типы зупв сравнительная характеристика.

- •112 Организация пзу. Типы пзу и их сравнительная характеристика.

- •113 Запоминающие устройства с последовательной выборкой. Ответ есть в 111

2. Пзу, основанные на оптическом принципе хранения информации.

Принцип работы этих устройств основан на изменении оптических свойств участка носителя, например, за счет изменения степени прозрачности или коэффициента отражения. Примером ПЗУ, основанном на оптическом принципе хранения информации, могут служит CD -, DVD-, BluRay - диски.

Основное достоинство данного типа ПЗУ – низкая стоимость носителя, удобство транспортирования и возможность тиражирования. Недостатки – низкая скорость чтения/записи, ограниченное количество перезаписей, потребность в считывающем устройстве.

3. Пзу, основанные на электрическом принципе хранения информации.

Принцип работы этих устройств основан на пороговых эффектах в полупроводниковых структурах – возможности хранения и регистрации наличия заряда в изолированной области.

Этот принцип используется в твердотельной памяти – памяти, не требующей использование подвижных частей для чтения/записи данных. Примером ПЗУ, основанном на электрическом принципе хранения информации, может служить flash – память.

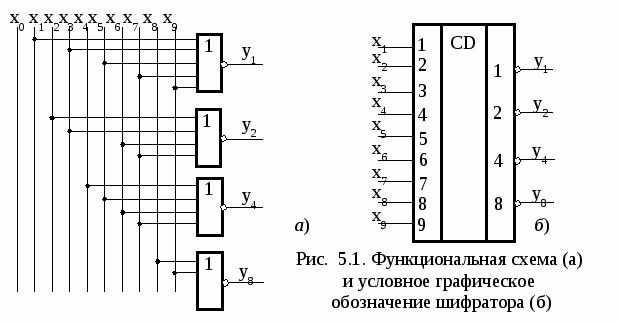

97. Интегральный шифратор к555ив3. Назначение выводов. Режимы работы

Шифратор К555ИВ3- шифратор. Он принимает напряжение логических уровней по девяти входам и генерирует выходной двоично-десятичный код на выходах . когда на один из входов подано напряжение низкого уровня, то на выходах(A0-A3) появляется соответствующий двоичный код (активные уровни- низкие). Входы(I1-I9) - приоритетные. Наибольший приоритет у входа I9. Шифратор имеет только 9 входов данных, входа для нуля нет, нуль кодируется на выходе, если на все девять входов поступили только напряжения высокого уровня. выходы инверсные

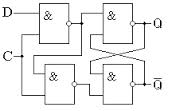

96. D-триггер. Схема. УГО. Работа

D -триггер наиболее распространенный вид триггера, его также называют, триггерами задержки. (от англ. Delay) запоминает состояние входа и выдает его на выход. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

Схема:

УГО:

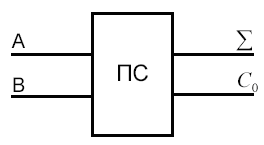

102. Полусумматор предназначен для сложения двух одноразрядных чисел. Результатами сложения являются двоичный разряд результата и разряд переноса, следующий значащий бит. Полусумматор работает в соответствии со следующей таблицей истинности:

103. а) двоичное вычитаемое записать в форме поразрядного доп 1 ед (инверсия)

Б) получ результат складываем с уменьшаемым

В)последний перенос влево(КЦП) запис под младшим разрядом промежуточной суммы

Г) получ результат складывается, получаем ответ (разность исходных чисел)

10 1010 1010

10 1010 1010

6 0110 1001

6 0110 1001

410 01002 10011

410 01002 10011

1

100

104.

105.

106.

Упр код служит для гашения индикации при лог 0 и отображения индикации при лог 1.

107. ЗУПВ (Запоминающее Устройство с Произвольной Выборкой). Микросхемы статических ЗУВП (СЗУПВ) имеют меньшее время доступа и не требуют циклов регенерации. Микросхемы динамических ЗУПВ (ДЗУПВ) характеризуются большей емкостью и меньшей стоимостью, но требуют схем регенерации и имеют значительно большее время доступа. С целью увеличения производительности все современные микросхемы памяти обеспечивают возможность подачи сигналов синхронизации, которые позволяют выполнять последовательные обращения к буферу без дополнительного времени обращения к строке. Имеются три способа подобной оптимизации:

блочный режим (nibblemode) - ДЗУВП может обеспечить выдачу четырех последовательных ячеек для каждого сигнала RAS.

страничный режим (pagemode) - Буфер работает как статическое ЗУПВ; при изменении адреса столбца возможен доступ к произвольным битам в буфере до тех пор, пока не поступит новое обращение к строке или не наступит время регенерации.

режим статического столбца (staticcolumn) - Очень похож на страничный режим за исключением того, что не обязательно переключать строб адреса столбца каждый раз для изменения адреса столбца.

В адресных ЗУ обращение к элементам памяти производится в соответствии с их адресом, задаваемым двоичным кодом. Большинство ЗУ являются адресными.

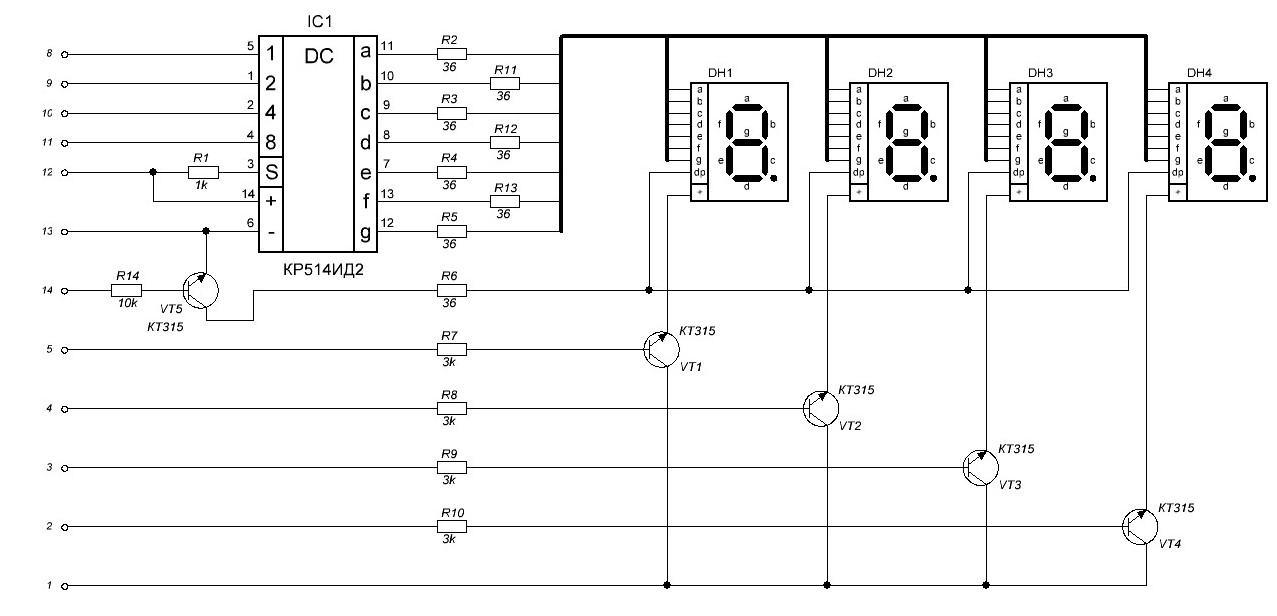

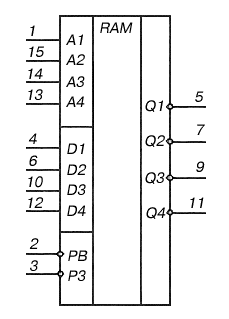

108. Микросхема К155РУ2 — это статическое ОЗУ с открытым коллекторным выходом — выполнена на основе ТТЛ-структур емкостью 64 бит. Имеет структуру 16 х 4, т. е. может хранить 16 слов длиной 4 разряда каждое.

А— адресные входы, D — информационные входы, РВ-— сигнал разрешения, РЗ— разрешение записи/считывания,

109.

Запись микропрограмм в ОЗУ происходит

в режиме ЗАГРУЗКА. МК заносится в память

109.

Запись микропрограмм в ОЗУ происходит

в режиме ЗАГРУЗКА. МК заносится в память

ОЗУ сегментами по 4 бита (тетрада). Адрес загружаемой МК набирается с помощью

переключателя АДРЕС, номер поля МК - переключателем МУЛЬТИПЛЕКСОР,

содержимое поля МК – переключателем ДАННЫЕ.Возможны два варианта загрузки: «по горизонтали» и «по вертикали». Загрузка по

горизонтали выполняется в следующей последовательности:

1. Переключатель ЗАГРУЗКА/РАБОТА установить в положение ЗАГРУЗКА.

2. С помощью переключателя АДРЕС набрать адрес загружаемой МК.

1. Переключателем МУЛЬТИПЛЕКСОР установить номер загружаемой тетрады.

2. Набрать с помощью переключателя ДАННЫЕ требуемый двоичный набор

(записываемую тетраду).

3. Нажать клавишу ЗАГРУЗКА, при этом происходит запись данных.

1. Проверить на индикаторе ПАМЯТЬ правильную загрузку тетрады в память ОЗУ.

2. Повторить шаги 3-6 для всех восьми комбинаций переключателей

МУЛЬТИПЛЕКСОР, что соответствует загрузке всех тетрад МК.

3. Повторить шаги 2-7 для загрузки всех возможных МК (максимальное число

микрокоманд равно 16). При программировании любые безразличные состояния полей

МК можно опускать.

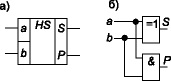

114. Полусумматор имеет два входа a и b для двух слагаемых и два выхода: S — сумма, P — перенос. Обозначением полусумматора служат буквы HS (half sum — полусумма). Работу его отражает таблица истинности

a |

b |

P |

S |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |