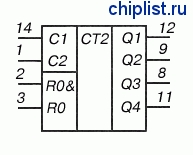

- •69. Универсальный счетчик ис к155ие5. Выходы. Режимы работы

- •75. Триггеры. Общие понятия. Назначение выводов.

- •76. Синхронный rs-триггер.Клс.Работа

- •77. Определение частоты и периода периодического сигнала. Пример

- •84. Регистры сдвига. Общие понятия. Пример цифровой схемы с использованием регистра сдвига.

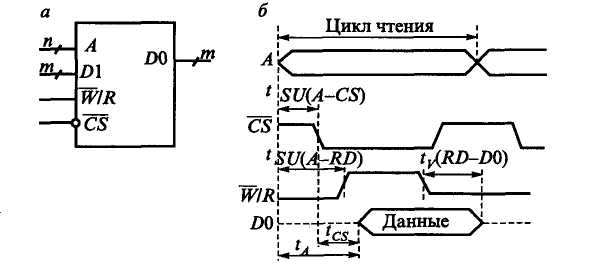

- •85.Запоминающие устройства. Общие понятия. Операции считывания и записи в зу.

- •86.Параллельный регистр сдвига. Работа.

- •2. Пзу, основанные на оптическом принципе хранения информации.

- •3. Пзу, основанные на электрическом принципе хранения информации.

- •97. Интегральный шифратор к555ив3. Назначение выводов. Режимы работы

- •1 10. Ис к155ру2. Процедура чтения из памяти. Пример

- •111. Типы зупв сравнительная характеристика.

- •112 Организация пзу. Типы пзу и их сравнительная характеристика.

- •113 Запоминающие устройства с последовательной выборкой. Ответ есть в 111

Цифровой сигнал. Получение ЦС. Основные параметры ЦС.Цифровой сигнал – прерывистая функция(решетчатая) присутствует точка разрыва 2 рода. Имеет всего 2 значения: +5 В - высокий уровень (лог. 1 [В]), 0 В – низкий уровень (лог. 0 [Н]) Получение: чтобы представить аналоговый сигнал последовательностью чисел конечной разрядности, его следует сначала превратить в дискретный сигнал, а затем подвергнуть квантованию. Квантование - частный случай дискретизации, когда дискретизация происходит по одинаковой величине, называемой квантом. В результате сигнал будет представлен таким образом, что на каждом заданном промежутке времени известно приближённое (квантованное) значение сигнала, которое можно записать целым числом. Последовательность таких чисел и будет являться цифровым сигналом.Основными параметрами сигналов являются длительность сигнала Tc, динамический диапазон Dc и ширина спектра ∆Fc.

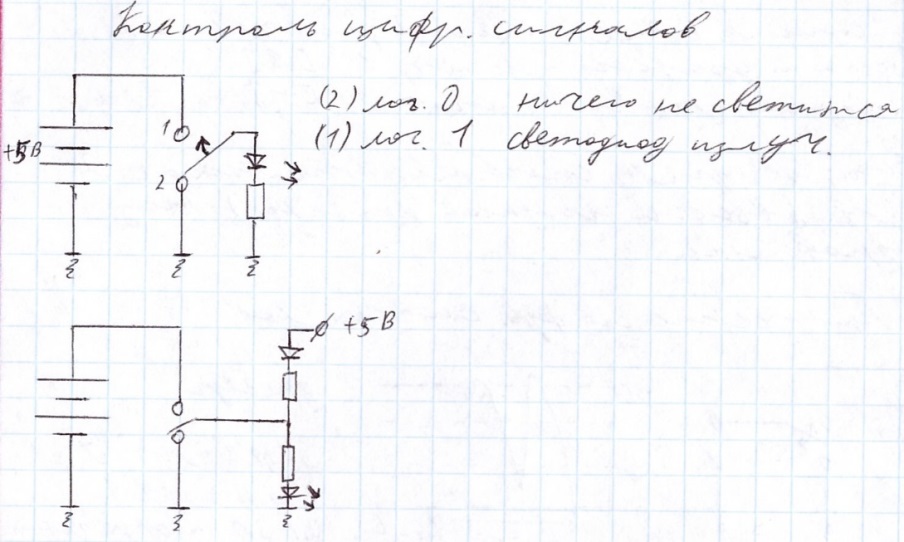

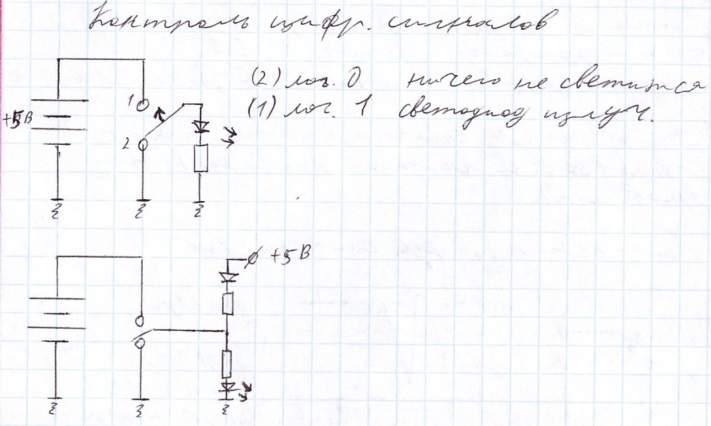

Контроль цифровых сигналов с помощью двух светодиодов.

Система счисления. Понятие веса разряда.Система счисления – код, в котором используется специальные символы для обозначения количества каких-либо объектов. Вес разряда – число, равное основанию системы счисления в степени номера разряда. Вес следующего разряда = весу предыдущего разряда, умноженному (·) на основание системы счисления.

Преобразование двоичного числа в десятичное и обратно. Пример 1 Пусть двоичное число 11111010002 необходимо преобразовать в десятичное. Решение представлено ниже: 11111010002 = 512·1+256·1+128·1+64·1+32·1+16·0+8·1+4·0+2·0+1·0 = 100010. Пример 2 37:2 = 18 остаток 1 18:2 = 9 остаток 0 9 : 2 = 4 остаток 1 4 : 2 = 2 остаток 0 2 : 2 = 1 остаток 0 1 : 2 = 0 остаток 1 Отсюда 3410 = 1001012. Деление заканчивается в тот момент, когда имеем частное равное 0.

Преобразование двоичного числа в шестнадцатеричное и обратно. Пример 3 Пусть мы хотим перейти от шестнадцатиричного числа С 316 к его двоичному эквиваленту. Для этого необходимо по таблице 3 найти тетраду для цифры С16, затем по той же таблице найти тетраду для цифры 316 и после этого записать найденные тетрады в том порядке в каком стояли цифры С16 и 316 в исходном шестнадцатиричном числе. С16 - 11002 316 - 00112

С316 = 110000112 Пример 4 Этот переход производится по той же таблице 3, только предварительно необходимо: разбить исходное двоичное число на тетрады начиная с крайнего правого разряда. После этого тетрады в исходном числе заменяют соответствующими шестнадцатиричными символами. Например: 111010102 = Х16. 11102 = Е16. 10102 = А16. Поэтому 111010102 = ЕА16.

Двоично-десятичный код (BCD). Двоично-десятичный код (англ. binary-coded decimal), BCD, 8421-BCD — форма записи рациональных чисел, когда каждый десятичный разряд числа записывается в виде его четырёхбитного двоичного кода.

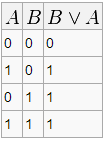

Логический элемент ИЛИ Дизъюнкция (логическое сложение). Операция ИЛИ

Мнемоническое

правило для дизъюнкции с любым количеством

входов звучит так: На выходе будет: «1»

тогда и только тогда, когда хотя

бы на одном входе

действует «1», «0» тогда и только тогда,

когда на всех входах

действуют «0»

Мнемоническое

правило для дизъюнкции с любым количеством

входов звучит так: На выходе будет: «1»

тогда и только тогда, когда хотя

бы на одном входе

действует «1», «0» тогда и только тогда,

когда на всех входах

действуют «0»

Логический элемент НЕ.

Мнемоническое

правило для отрицания звучит так: На

выходе будет: «1» тогда и только тогда,

когда на входе «0», «0» тогда и только

тогда, когда на входе «1»

Мнемоническое

правило для отрицания звучит так: На

выходе будет: «1» тогда и только тогда,

когда на входе «0», «0» тогда и только

тогда, когда на входе «1»

Логический элемент ИЛИ-НЕ.

Мнемоническое

правило для ИЛИ-НЕ с любым количеством

входов звучит так: На выходе будет: «1»

тогда и только тогда, когда на всех входах

действуют «0», «0» тогда и только тогда,

когда хотя

бы на одном входе

действует «1»

Мнемоническое

правило для ИЛИ-НЕ с любым количеством

входов звучит так: На выходе будет: «1»

тогда и только тогда, когда на всех входах

действуют «0», «0» тогда и только тогда,

когда хотя

бы на одном входе

действует «1»

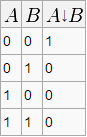

Логический элемент И-НЕ.

Мнемоническое

правило для И-НЕ с любым количеством

входов звучит так: На выходе будет: «1»

тогда и только тогда, когда хотя

бы на одном входе

действует «0», «0» тогда и только тогда,

когда на всех входах

действуют «1»

Мнемоническое

правило для И-НЕ с любым количеством

входов звучит так: На выходе будет: «1»

тогда и только тогда, когда хотя

бы на одном входе

действует «0», «0» тогда и только тогда,

когда на всех входах

действуют «1»

Логический элемент ИСКЛЮЧАЮЩЕЕ-ИЛИ.

Мнемоническое

правило для суммы по модулю 2 с любым

количеством входов звучит так: На выходе

будет: «1» тогда и только тогда, когда

на входе действует нечётное количество,

«0» тогда и только тогда, когда на входе

действует чётное количество

Мнемоническое

правило для суммы по модулю 2 с любым

количеством входов звучит так: На выходе

будет: «1» тогда и только тогда, когда

на входе действует нечётное количество,

«0» тогда и только тогда, когда на входе

действует чётное количество

Словесное описание: "истина на выходе - только при истине на входе1, либо только при истине на входе 2"..

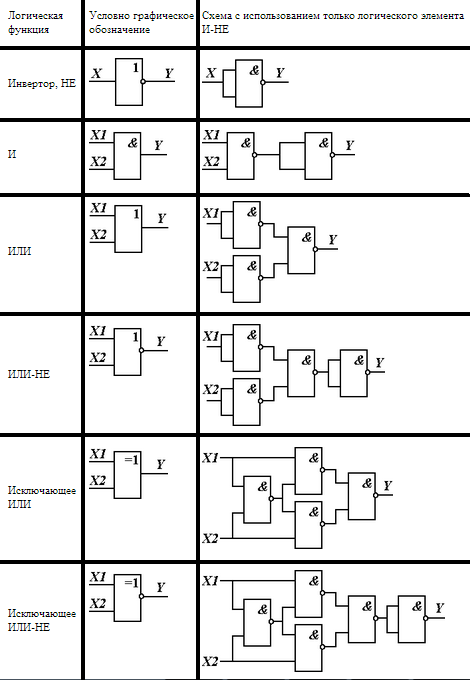

Универсальный характер логического элемента И-НЕ. С помощью достаточного количества логических элементов И-НЕ можно реализовать любую логическую функцию.

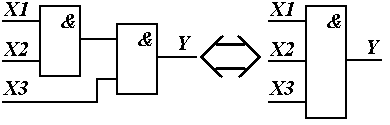

Логические элементы с числом входов больше двух. Пример. Помимо двухвходовых логических элементов широко применяются логические элементы с числом входов больше 2. Рассмотрим трехвходовый элемент И (3И).

Нетрудно

получить булево выражение для трехвходового

элемента У=Х1·Х2·Х3

Нетрудно

получить булево выражение для трехвходового

элемента У=Х1·Х2·Х3

X1 |

X2 |

X3 |

Y |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

Преобразование шестнадцатеричного числа в десятичное. Переход от шестнадцатиричной системы к двоичной осуществляется по тому же алгоритму, что и переход от двоичной системы к десятичной. Разница состоит в том, что вес разряда в шестнадцатиричной системе представляет собой натуральную степень числа 16, так как 16 в данном случае является основанием системы счисления. Пример 7 2DB16=X10 2DB16=2·162+D·161+B·160 = 2·256 + 13(D16)·16 + 11(B16)·1= 73110. Пример 8 2C6E16=2·163+C·162+6·161+E·160=2·4096+12·256+6·16+14·1=1137410.

Преобразование десятичного числа в шестнадцатеричное. Переход в этом случае осуществляется делением исходного числа , на основание системы счисления в которую мы переходим, в целых числах с выписыванием остатков деления, по схеме, которую мы уже использовали в пункте 2 настоящей главы. Пример 9 4710=X16. 4710 : 16 = 2 остаток 15 - F разряд весом 1. (160) 210 : 16 = 0 остаток 2 - 2 разряд весом 16. (161) Поэтому 4710=2F16. Остатки представленные в шестнадцатиричном виде с учетом веса разряда и дают искомое шестнадцатиричное число.

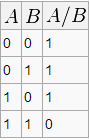

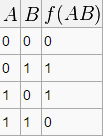

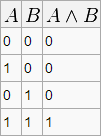

Логический элемент И

Логический

элемент, реализующий функцию конъюнкции,

называется схемой совпадения. Мнемоническое

правило для конъюнкции с любым количеством

входов звучит так: На выходе будет: «1»

тогда и только тогда, когда на всех входах

действуют «1», «0» тогда и только тогда,

когда хотя

бы на одном входе

действует «0». Словесно эту операцию

можно выразить следующим выражением:

"Истина на выходе может быть при

истине на входе 1 И истине

на входе 2".

Логический

элемент, реализующий функцию конъюнкции,

называется схемой совпадения. Мнемоническое

правило для конъюнкции с любым количеством

входов звучит так: На выходе будет: «1»

тогда и только тогда, когда на всех входах

действуют «1», «0» тогда и только тогда,

когда хотя

бы на одном входе

действует «0». Словесно эту операцию

можно выразить следующим выражением:

"Истина на выходе может быть при

истине на входе 1 И истине

на входе 2".

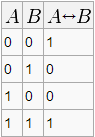

Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ.

Мнемоническое

правило эквивалентности с любым

количеством входов звучит так: На выходе

будет: «1» тогда и только тогда, когда

на входе действует четное количество,

«0» тогда и только тогда, когда на входе

действует нечетное количество

Словесная запись: "истина на выходе

при истине на входе 1 и входе

2 или при

лжи на входе 1 и входе

2".

Мнемоническое

правило эквивалентности с любым

количеством входов звучит так: На выходе

будет: «1» тогда и только тогда, когда

на входе действует четное количество,

«0» тогда и только тогда, когда на входе

действует нечетное количество

Словесная запись: "истина на выходе

при истине на входе 1 и входе

2 или при

лжи на входе 1 и входе

2".

Цифровой сигнал. Определение. Общие понятия. Цифровой сигнал — сигнал данных, у которого каждый из представляющих параметров описывается функцией дискретного времени и конечным множеством возможных значений. В отличие от аналоговых, цифровые сигналы, имеющие всего два разрешенных значения, защищены от действия шумов, наводок и помех гораздо лучше. Цифровые сигналы допускают гораздо более сложную и многоступенчатую обработку, гораздо более длительное хранение без потерь и гораздо более качественную передачу. Цифровые устройства гораздо меньше подвержены старению, так как небольшое изменение их параметров никак не отражается на их функционировании. Кроме того, цифровые устройства проще проектировать и отлаживать.

Контроль цифровых сигналов с помощью одного светодиода.

Комбинационная и последовательностная логические схемы Комбинационная логическая схема(КЛС) – схема, собранная из базовых логических элементов или их производных. В КЛС состояние выхода схемы заданным образом зависит от текущей составляющей ее входа. Схемы могут строится с использование одних лишь логических элементов. Последовательностная логическая схема – схема, в которой состояние выхода определяется как состояние входа в текущее время, так и предыдущее состоянии. Схемы этого типа требуют наличия памяти в какой-либо форме. Для использования в электронных схемах выпускается широкий набор различных комбинационных схем в виде микросхем: различные логические элементы, шифраторы и дешифраторы, мультиплексоры и другие схемы, а также последовательностные схемы: триггеры, счетчики, регистры.

Селектор данных. Определение. Назначение. Мультиплексор – логическая схема, производящая выбор одного из нескольких информационных входов, в соответствии с выбранным адресом и коммутацию выбранного информационного входа с информационным выходом. Мультиплексор (селектор данных) осуществляет операцию передачи сигнала с выбранного входа на выход. Номер входа равен адресу - двоичному числу, определяемому состоянием адресных входов. Мультиплексоры - селекторы данных предназначены для коммутации данных на магистрали согласно управляющим сигналам с автоматическим формированием контрольного разряда по четности выдаваемой информации.

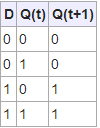

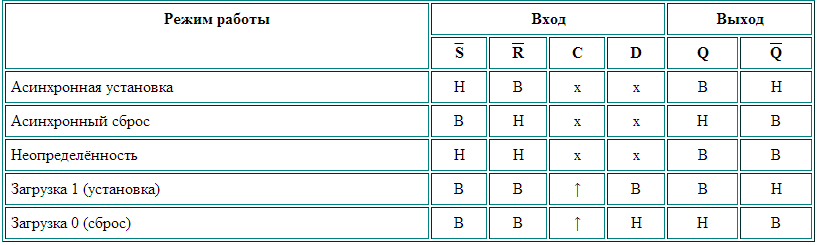

D-триггер. Обозначение таблица истинности.

Код с избытком 3.

Десятичное число |

8 |

4 |

2 |

1(+3) |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

2 |

0 |

1 |

0 |

1 |

3 |

0 |

1 |

1 |

0 |

4 |

0 |

1 |

1 |

1 |

5 |

1 |

0 |

0 |

0 |

6 |

1 |

0 |

0 |

1 |

7 |

1 |

0 |

1 |

0 |

8 |

1 |

0 |

1 |

1 |

9 |

1 |

1 |

0 |

0 |

Регулярный и нерегулярный коды, примеры. Код Эйкена.

Десятичное число |

2 |

4 |

2 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

1 |

1 |

4 |

0 |

1 |

0 |

0 |

5 |

1 |

0 |

1 |

1 |

6 |

1 |

1 |

0 |

0 |

7 |

1 |

1 |

0 |

1 |

8 |

1 |

1 |

1 |

0 |

9 |

1 |

1 |

1 |

1 |

Код Эйкена

Код Грея.

Десятичное число |

Код Грея |

|||

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

1 |

1 |

3 |

0 |

0 |

1 |

0 |

4 |

0 |

1 |

1 |

0 |

5 |

0 |

1 |

1 |

1 |

6 |

0 |

1 |

0 |

1 |

7 |

0 |

1 |

0 |

0 |

8 |

1 |

1 |

0 |

0 |

9 |

1 |

1 |

0 |

1 |

10 |

1 |

1 |

1 |

1 |

11 |

1 |

1 |

1 |

0 |

12 |

1 |

0 |

1 |

0 |

13 |

1 |

0 |

1 |

1 |

14 |

1 |

0 |

0 |

1 |

15 |

1 |

0 |

0 |

0 |

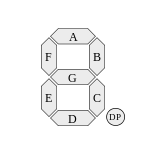

Семисегментный код.

Десятичное число |

a |

b |

c |

d |

e |

f |

g |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

2 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

3 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

4 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

5 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

6 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

7 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

8 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

9 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

Шифратор. Применение. Пример. Шифратор – функциональный узел, осуществляющий преобразование сигнала на одном из входов в код на его выходах.

Шифратор К555ИВ3. УГО. Назначение.

К555ИВ3

– шифратор. Принимает напряжения

логических уровней по девяти входам и

генерирует выходной двоично-десятичный

код на выходах.

К555ИВ3

– шифратор. Принимает напряжения

логических уровней по девяти входам и

генерирует выходной двоично-десятичный

код на выходах.

Семисегментный

индикатор. Устройство. Типы. Семисегме́нтный

индика́тор —

устройство отображения цифровой

информации. Сегменты обозначаются буквами от A до

G; восьмой сегмент — десятичная

точка (decimal

point,

DP),

предназначенная для отображения дробных

чисел. Типы: жидкокристаллические,

газоразрядные, вакуумно-люминесцентные

и др.

Сегменты обозначаются буквами от A до

G; восьмой сегмент — десятичная

точка (decimal

point,

DP),

предназначенная для отображения дробных

чисел. Типы: жидкокристаллические,

газоразрядные, вакуумно-люминесцентные

и др.

Семисегментный светодиодный индикатор. Устройство.

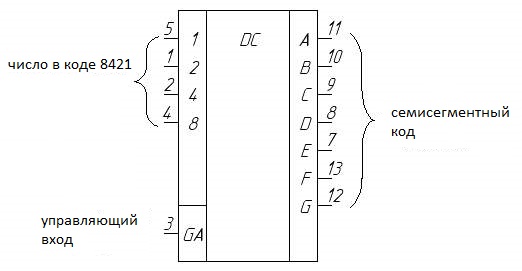

Семисегментный дешифратор К514ИД2.

Схема включения К514ИД2 с семисегментным светодиодным индикатором.

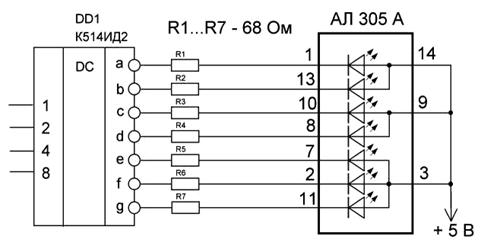

Схема цифрового табло с использованием К514ИД2.

Асинхронный RS-триггер. Входы. Обозначение. Таблица истинности.

S

– set

S

– set

R – reset

Режим |

S |

R |

Q |

Q— |

Запрещен. |

0 |

0 |

1 |

1 |

Установка 1 |

0 |

1 |

1 |

0 |

Установка 0 |

1 |

0 |

0 |

1 |

Хранение |

1 |

1 |

Q |

Q— |

КЛС RS-триггера. Временные диаграммы.

КЛС

Временная

диаграмма

Синхронный RS-триггер. Обозначение. Таблица истинности.

C

– Вход синхронизации

C

– Вход синхронизации

Режим |

C |

S |

R |

Q |

Q— |

Хранения |

|

0 |

0 |

Q |

Q— |

Установка 0 |

|

0 |

1 |

0 |

1 |

Установка 1 |

|

1 |

0 |

1 |

0 |

Запрещенное состояние |

|

1 |

1 |

1 |

1 |

Принцип действия самоостанавливающегося счетчика. Пример.

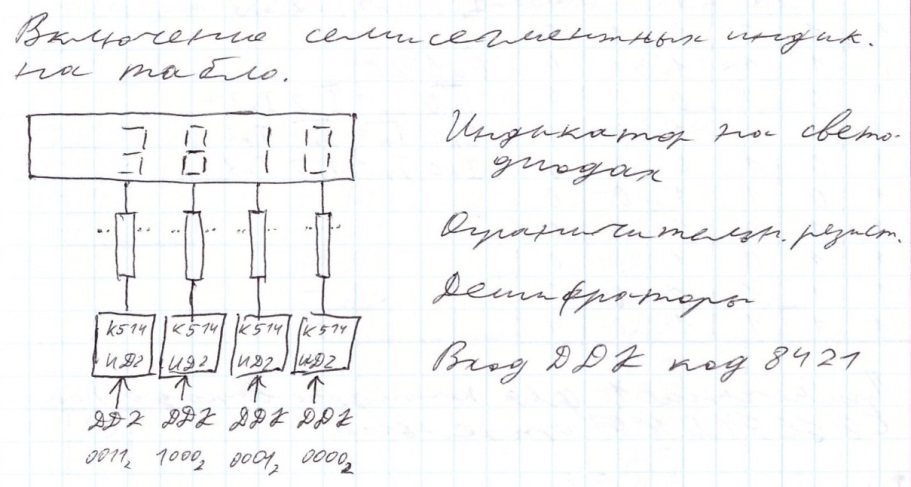

Статическое и динамическое управление триггерами.

Статическое управление – управление, что в продолжении времени действия тактового импульса смена сигналов на информационных входах вызывает новое срабатывание устройства.

Динамическое управление – управление, что в зависимости от схемы реагирует на перепад напряжения либо от 0 к 1, либо от 1 к 0.

Динамическое управление триггерами. Обозначение динамических входов на принципиальных схемах.

D-триггер с динамическим управлением. ИС К155ТМ2. Режимы работы

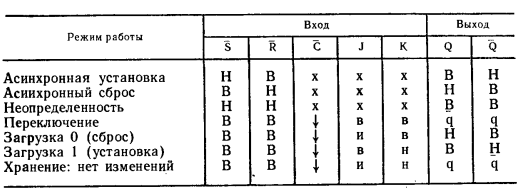

JK-триггер. Обозначение Режимы работы.

|

Входы |

Выходы |

|||

Режим |

C |

J |

K |

Q |

Q— |

Хранение |

|

0 |

0 |

Без изменений |

|

Установка 0 |

|

0 |

1 |

0 |

1 |

Установка 1 |

|

1 |

0 |

1 |

0 |

Переключательный |

|

1 |

1 |

Изменение состояния на противоположное |

|

КЛС JK-триггера

JK-триггер с динамическим управлением. УГО. Режимы работы ИС К555ТВ9.

Запуск

триггеров с динамическим управлением.

Временные диаграммы. Примеры обозначения

на принципиальных схемах. В

триггерах с динамическим управлением

передача сигнала с информационных

входов на выходы осуществляется по

фронту или по спаду синхронизирующего

импульса.

б) временная диаграмма чтения.

Rs-триггер

принципиальная схема

Rs-триггер

принципиальная схема

D-триггер

D-триггер

Двухступенчатые

триггеры. Обозначение. Работа.

Двухступенчатый

RS - триггер. Для устойчивой работы

триггера необходимо, чтобы сигналы Q(t)

и Q(t)(c инверсией)изменялись только после

прекращения действия входного сигнала

S(t) или R(t). Это требование выполняется

в двухступенчатых триггерах. Двухступенчатый

триггер состоит из двух секций (ступеней),

соединенных каскадно, как показано на

рис. 3.6 а

Счетчики общие понятия. Счетчики представляют собой последовательностые цифровые устройства и предназначены для выполнения операций счета и хранения кода числа подсчитанных импульсов. В суммирующих счетчиках код последующего состояния имеет большее значение, чем код предыдущего состояния, а в вычитающих – меньшее значение. Реверсивные счетчики могут работать как в режиме суммирования, так и в режиме вычитания.

Асинхронный счетчик по модулю 10. Рассмотрим принцип работы данной схемы, что за числом 1001 следует 1010 (10 в десятичной системе). При подаче логической1, содержащейся в разрядах двоек и восьмерок двоичного числа 1010, на входы элемента И‑НЕ, этот элемент подаст логический 0 на входы R четырех триггеров. Таким образом, все триггеры установятся в состояние 0 и счетчик снова начинает считать от 0000 до 1010. Подобное использование логического элемента И‑НЕ позволяет создать счетчики с некоторыми другими значениями модуля. Счетчик, называют также декадным (десятичным) счетчиком.

Асинхронные

счётчики по модулю 10tc

"13.3. Асинхронные счётчики по модулю

10"

Счётчик по

модулю 10 считает

от 0000 до 1001 (от 0 до 9 в

десятичной системе), т.е. до черты в

табл.13.1. Для построения такого счётчика

трёх триггеров недостаточно (10>23),

поэтому он содержит 4 триггера,

но имеет обратные связи, останавливающие

счёт при коде 9=1001.

На рис.13.3 показана схема счётчика по

модулю 10,

в которую кроме 4 триггеров

включён логический элемент И‑НЕ, для

установки всех триггеров в нулевое

состояние (очистки счетчика) с приходом

десятого импульса.

Рис.13.3.

Схема асинхронного счетчика по

модулю 10

Рассмотрим

принцип работы данной схемы (рис.13.3). Из

табл.13.1 видно, что за числом 1001 следует 1010 (10 в

десятичной системе). При подаче

логической1,

содержащейся в разрядах двоек и восьмерок

двоичного числа 1010,

на входы элемента И‑НЕ, этот элемент

подаст логический 0 на

входы R четырех

триггеров. Таким образом,

все триггеры установятся

в состояние 0 и

счетчик снова начинает считать

от 0000 до 1010.

Подобное использование логического

элемента И‑НЕ позволяет создать счетчики с

некоторыми другими значениями модуля.

Счетчик, изображенный на рис.13.3 называют

также декадным (десятичным) счетчиком.

Рис.13.3.

Схема асинхронного счетчика по

модулю 10

Рассмотрим

принцип работы данной схемы (рис.13.3). Из

табл.13.1 видно, что за числом 1001 следует 1010 (10 в

десятичной системе). При подаче

логической1,

содержащейся в разрядах двоек и восьмерок

двоичного числа 1010,

на входы элемента И‑НЕ, этот элемент

подаст логический 0 на

входы R четырех

триггеров. Таким образом,

все триггеры установятся

в состояние 0 и

счетчик снова начинает считать

от 0000 до 1010.

Подобное использование логического

элемента И‑НЕ позволяет создать счетчики с

некоторыми другими значениями модуля.

Счетчик, изображенный на рис.13.3 называют

также декадным (десятичным) счетчиком.

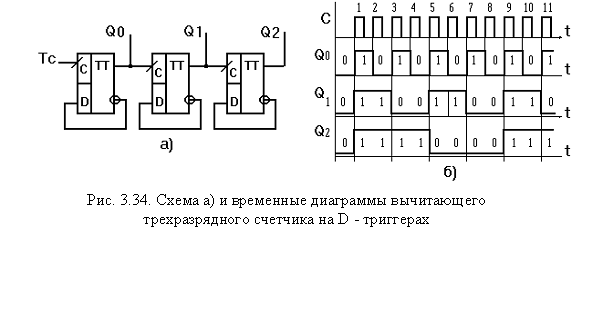

63.На

рис. 3.34 приведена схема асинхронного

трехразрядного двоичного вычитающего

счетчика, построенного на базе D-триггеров.

Отметим, что условия для изменения

состояний триггеров вычитающих счетчиков

аналогичны условиям для суммирующих

счетчиков с той лишь разницей, что они

должны “опираться” на значения

инверсных, а не прямых выходов триггеров.

Следовательно, рассмотренный выше

счетчик можно превратить в вычитающий,

просто переключив входы “С” триггеров

с выходов Q на выходы . Когда в качестве

разрядных триггеров используются

D-триггеры, синхронизируемые передним

фронтом синхроимпульсов, для получения

вычитающего счетчика (асинхронного)

входы “С” последующих тригеров

соединяются с прямыми выходами предыдущих,

также как в счетчике прямого счета,

построенного на JK-триггерах.

Работа

вычитающего счетчика на D-триггерах

наглядно иллюстрирована на рис. 3.34, (б).

Из рис. 3.34 следует, что после нулевого

состояния всех триггеров, с приходом

первого синхроимпульса они устанавливаются

в состояние “1”. Поступление второго

синхроимпульса приводит к уменьшению

этого числа на одну единицу и т.д. После

поступления восьмого импульса, снова,

все триггеры обнуляются и цикл счета

повторяется, что соответствует модулю

М=8.

64.Последовательный регистр сдвига, с работой которого мы познакомились в предыдущем разделе, обладает двумя недостатками: он позволяет вводить только по одному биту информации на каждом тактовом импульсе и, кроме того, каждый раз при сдвиге информации в регистре вправо теряется крайний правый информационный бит.

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, то есть цепи управления.

65. Самоостанавливающийся счетчик по модулю 3.-сегодня на консультации разбирали.ктописал может скинуть

^ Ми кросхемы

К155ИЕ2 и К155ИЕ4 также

содержат 4 триггера, причем первый из

них отделен от остальных, как в К155ИЕ5,

а три оставшихся соединены так, что

образуют трехразрядные счетчики с

модулем счета 5 в К155ИЕ2 и с модулем счета

6 в К155ИЕ4.

Рассмотрим

трехразрядный вычитающий счетчик с

последовательным переносом, схема и

временные диаграммы работы которого

приведены на рис. 3.18.

В

кросхемы

К155ИЕ2 и К155ИЕ4 также

содержат 4 триггера, причем первый из

них отделен от остальных, как в К155ИЕ5,

а три оставшихся соединены так, что

образуют трехразрядные счетчики с

модулем счета 5 в К155ИЕ2 и с модулем счета

6 в К155ИЕ4.

Рассмотрим

трехразрядный вычитающий счетчик с

последовательным переносом, схема и

временные диаграммы работы которого

приведены на рис. 3.18.

В ![]() счетчике

используются три JК-триггера, каждый из

которых работает в режиме T-триггера

(триггера со счетным входом).

На

входы J и К каждого триггера поданы

логические 1, поэтому по приходу

заднего фронта импульса, подаваемого

на его вход синхронизации С, каждый

триггер изменяет предыдущее состояние.

Вначале сигналы на выходах всех

триггеров равны 1. Это соответствует

хранению в счетчике двоичного числа

111 или десятичного числа 7.

После

окончания первого импульса F первый

триггер изменяет состояние: сигнал

Q1 станет

равным 0, a Q1—

1. Остальные триггеры при этом свое

состояние не изменяют. После окончания

второго импульса синхронизации первый

триггер вновь изменяет свое состояние,

переходя в состояние 1 (Q1 =

0).

Это

обеспечивает изменение состояния

второго триггера (второй триггер изменяет

состояние с некоторой задержкой по

отношению к окончанию второго импульса

синхронизации, так как для его

опрокидывания необходимо время,

соответствующее времени срабатывания

его самого и первого триггера). После

первого импульса F счетчик хранит

состояние 110. Дальнейшее изменение

состояния счетчика происходит аналогично

изложенному выше. После состояния 000

счетчик вновь переходит в состояние

111.

счетчике

используются три JК-триггера, каждый из

которых работает в режиме T-триггера

(триггера со счетным входом).

На

входы J и К каждого триггера поданы

логические 1, поэтому по приходу

заднего фронта импульса, подаваемого

на его вход синхронизации С, каждый

триггер изменяет предыдущее состояние.

Вначале сигналы на выходах всех

триггеров равны 1. Это соответствует

хранению в счетчике двоичного числа

111 или десятичного числа 7.

После

окончания первого импульса F первый

триггер изменяет состояние: сигнал

Q1 станет

равным 0, a Q1—

1. Остальные триггеры при этом свое

состояние не изменяют. После окончания

второго импульса синхронизации первый

триггер вновь изменяет свое состояние,

переходя в состояние 1 (Q1 =

0).

Это

обеспечивает изменение состояния

второго триггера (второй триггер изменяет

состояние с некоторой задержкой по

отношению к окончанию второго импульса

синхронизации, так как для его

опрокидывания необходимо время,

соответствующее времени срабатывания

его самого и первого триггера). После

первого импульса F счетчик хранит

состояние 110. Дальнейшее изменение

состояния счетчика происходит аналогично

изложенному выше. После состояния 000

счетчик вновь переходит в состояние

111.

67)

![]() Самоостанавливающийся

счетчик по

модулю 6.

Самоостанавливающийся

счетчик по

модулю 6.

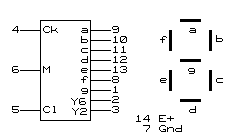

Микросхема ИЕ3 представляет собой двоичный счетчик по модулю 6 с дешифратором в 7-сегментный код. Исходное состояние схемы устанавливается подачей сигнала H на вход Cl (5). Входная частота подается на вход Ck (4), а выходная частота (в 6 раз меньше) появляется на выводе Y6 (2). После каждого второго входного импульса на выводе Y2 (3) формируется сигнал, который используется для выработки команды сброс в разрядах индикатора "Часы". В случаях использования жидкокристаллических индикаторов, в схеме предусмотрено получение на выходе прямого и инверсного кода (относительно входа Ck) путем подачи на вывод 6 (M) сигнала с частотой 32 или 64 Гц. При применении индикаторов, не требующих знакопеременного питающего напряжения, на вывод M подается постоянное напряжение L.

68)

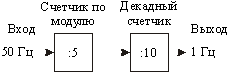

по модулю 5(счетчик‑делитель

на 5)

получим схему, осуществляющую деления

частоты на 50.

Структура такой схемы показана на

рис.13.10. Последовательность прямоугольных

импульсов с частотой 50 Гц

поступает на вход счетчика - делителя

на 5,

а с его выхода с частотой 10 Гц

подается на вход счетчика‑делителя

на 10.

На выходе схемы получим сигнал с

частотой 1 Гц.

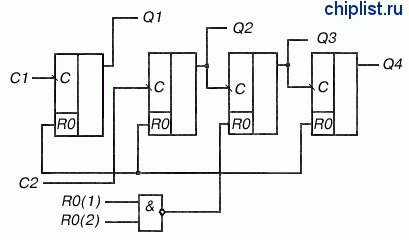

69. Универсальный счетчик ис к155ие5. Выходы. Режимы работы

Микросхемы

представляет собой двоичный счетчик.

Каждая ИС состоит из четырех

JK-триггеров,образуя счетчик делитель

на 2 и 8. Установочные входы обеспечивают

прекращение счета и одновременно

возвращают все триггеры в состояние

низкого уровня (на входы R0(1) и R0(2) подается

высокий уровень). Выход Q1 не соединен с

последующими триггерами. Если ИС

используется как четырехразрядный

двоичный счетчик, то счетные импульсы

подаются на С1, а если как трехразрядный

- то на вход С2.

Условное

графическое обозначение

1

- вход счетный С2;

2

- вход установки 0 R0(1); 3 - вход установки

0 R0(2);

4,6,7,13

- свободные; 5 - напряжение питания +Uп;

8

- выход Q3; 9 - выход Q2;

10

- общий; 11 - выход Q4;

12

- выход Q1; 14 - вход счетный C1;

Функциональная

схема

1

- вход счетный С2;

2

- вход установки 0 R0(1); 3 - вход установки

0 R0(2);

4,6,7,13

- свободные; 5 - напряжение питания +Uп;

8

- выход Q3; 9 - выход Q2;

10

- общий; 11 - выход Q4;

12

- выход Q1; 14 - вход счетный C1;

Функциональная

схема

Электрические

параметры

Электрические

параметры

1 |

Номинальное напряжение питания |

5

В |

2 |

Выходное напряжение низкого уровня при Uп=4,75 В |

не более 0,4 В |

3 |

Выходное напряжение высокого уровня при Uп=4,75 В |

не менее 2,4 В |

4 |

Напряжение на антизвонном диоде при Uп=4,75 В |

не менее 1,5 В |

5 |

Входной ток низкого уровня по входам установки в 0 при Uп=5,25 В |

не более -1,6 мА |

6 |

Входной ток низкого уровня по счетным входам С1 и С2 при Uп=5,25 В |

не более -3,2 мА |

7 |

Входной ток высокого уровня по входам установки в 0 при Uп=5,25 В |

не более -0,04 мА |

8 |

Входной ток высокого уровня по счетным входам С1 и С2 при Uп=5,25 В |

не более 0,08 мА |

9 |

Ток входного пробивного напряжения по входам установки в 0 и счетным входам С1 и С2 |

не более 1 мА |

10 |

Ток потребления |

не более 53 мА |

11 |

Время задержки распространения при включении по счетному входу С1 при Uп=5 В |

не более 135 нс |

12 |

Время задержки распространения при выключении по счетному входу С1 при Uп=5 В |

не более 135 нс |

13 |

Ток короткого замыкания приUп=5,25 В |

-18...57 мА |

Предельно допустимые режимы эксплуатации

1 |

Напряжение питания |

не более 6 В |

2 |

Минимальное напряжение на входе |

-0,4 В |

3 |

Максимальное напряжение на входе |

5,5 В |

4 |

Минимальное напряжение на выходе |

-0,3 В |

5 |

Максимальное напряжение на выходе закрытой ИС |

5,25 В |

6 |

Температура окружающей среды К155ИЕ5 КМ155ИЕ5 |

-10...+70 ° C -45...+85 ° C |

70.Включение ИСК155ИЕ5 как счетчика по модулю 8

71.Включение ИСК155ИЕ5 как счетчика по модулю 3