- •Исследование, разработка и применение параметризованных аналоговых элементов в составе библиотеки аналоговых базовых и сложно-функциональных блоков.

- •210100 «Электроника и наноэлектроника»

- •Глава 1. Литературный обзор. 7

- •Глава 2. Исследование и разработка оптимальных параметризованных элементов второго уровня под выбранный класс задач. 30

- •Глава 3. Применение спроектированных параметризованных аналоговых ячеек второго уровня в составе базовых блоков. 81

- •Введение.

- •Положения, выносимые на защиту.

- •Основная часть. Глава 1. Литературный обзор.

- •Автоматизация проектирования аналоговых микросхем. Обзор существующих решений.

- •Pcell – определение, способы реализации и применение.

- •Аналоговые ячейки второго уровня. Их применение.

- •Специфика физического проектирования.

- •Причины рассогласования элементов и способы их устранения.

- •Построение согласованных элементов.

- •Размещение согласуемых элементов с общим центром.

- •Уменьшение технологического влияния соседних структур для лучшего согласования элементов.

- •Рекомендации по согласованию моп-транзисторов.

- •Рекомендации по согласованию конденсаторов.

- •Методы защиты от включения тиристорной защелки.

- •Язык skill. Краткие сведения.

- •Выводы.

- •Глава 2. Исследование и разработка оптимальных параметризованных элементов второго уровня под выбранный класс задач.

- •Введение.

- •Построение элементарных параметризованных ячеек.

- •Определение изменяемых параметров.

- •Создание топологических эскизов.

- •Построение ячейки транзистора на языке skill.

- •Оптимизация программного кода.

- •Построение параметризованных аналоговых ячеек второго уровня.

- •Способы применения элементарных ячеек в составе проектируемых аналоговых ячеек второго уровня.

- •Согласование элементов на примере построения матрицы согласованных конденсаторов с соотношением элементов 1:1.

- •Построение разводки.

- •Использование элементов защиты.

- •Способы задания изменяемых параметров и их ограничений.

- •Оптимизация ячеек.

- •Методика проектирования высокоточных параметризованных аналоговых ячеек второго уровня на языке skill.

- •Глава 3. Применение спроектированных параметризованных аналоговых ячеек второго уровня в составе базовых блоков.

- •Компаратор.

- •Операционный усилитель.

- •Устройство выборки и хранения (увх).

- •Преимущества и недостатки использования спроектированных параметризованных аналоговых ячеек второго уровня.

- •Заключение.

- •Список литературы.

- •Приложение.

Уменьшение технологического влияния соседних структур для лучшего согласования элементов.

При изготовлении ИМС на довольно протяжённом технологическом маршруте возникает множество технологических факторов, вызывающих отклонения параметров элементов СФ-блоков. Например, фактические скорости травления поликремневых и диффузионных областей в локальных областях кристалла зависят от взаимного расположения элементов. В результате такой зависимости может возникнуть рассогласование в эффективных ширинах и длинах каналов согласованных МОП-транзисторов.

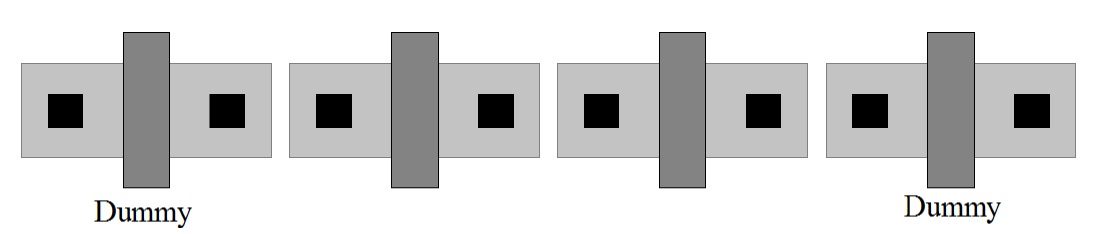

Использование транзисторы с длиной канала больше минимальной и фиктивных элементов (dummy-элементы) гарантирует однородное травление (Рис 1.13). Отсутствие фиктивных элементов может привести к рассогласованию по току 1% или более.

Рис. 1.13. Пример топология с использованием dummy-транзисторов по обе стороны от активных транзисторов.

Расстояние между фиктивными и рабочими затворами должно точно соответствовать расстоянию между рабочими затворами. При этом не допускается размещение контактов над рабочими затворами МОП-транзисторов.

На фиктивные сегменты желательно подавать напряжение земли/питания, чтобы предотвратить на них накопление плавающих потенциалов.

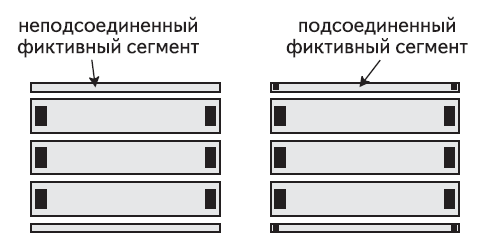

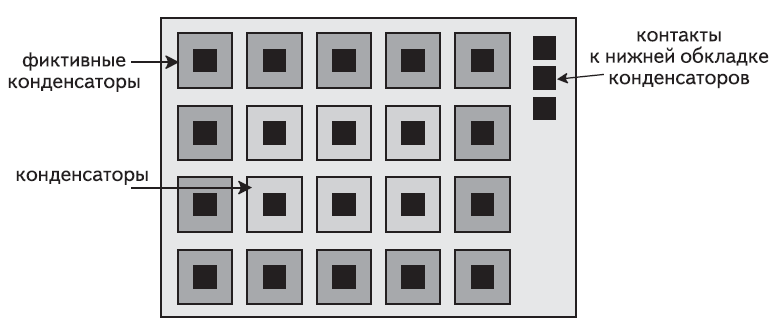

На рис. 1.14, 1.15 приводятся примеры построения фиктивных элементов при построении согласованных резисторов (с подключением к основному телу резистора и без него) и конденсаторов.

Рис. 1.14. Примеры построения фиктивных сегментов для согласованных резисторов.

Рис. 1.15. Пример построения фиктивных сегментов для согласованных конденсаторов.

Рекомендации по согласованию моп-транзисторов.

N-канальные транзисторы, как правило, обеспечивают более высокую степень согласования, чем p-канальные транзисторы при прочих равных условиях. Это явление наблюдается в ряде различных процессов, включая варианты и с p-карманом, и с n-карманом. P-канальные транзисторы показывают от 30 до 50% большее рассогласование по крутизне, чем аналогичные n-канальные.

Согласуемые МОП-транзисторы разделяются на сегменты, или пальцы, позволяющие построить компактный массив. Самый простой тип массива — размещение многих пальцев транзистора параллельно. При этом допускается объединение общих истоков и/или стоков. На рис. 1.16 показан пример пары согласованных МОП-транзисторов с общим центром и фиктивными элементами.

Рис. 1.16. Пример топологии пары согласованных транзисторов (common-centroid).

На рис. 1.17 показан пример пары согласованных МОП-транзисторов с перекрестными связями и фиктивными элементами.

Рис. 1.17. Пример топологии пары согласованных транзисторов с использованием перекрестных связей (cross-coupled).

Для достижения наибольшего согласования желательно выбирать максимально возможную для данного применения площадь затворов транзистора.

Следующие рекомендации суммируют наиболее важные принципы построения согласованных МОП-транзисторов:

использовать идентичную конфигурацию пальцев;

использовать большие по площади рабочие области;

ориентировать транзисторы в одинаковом направлении;

размещать транзисторы, по возможности, вблизи друг от друга;

использовать компактное размещение согласованных транзисторов;

применять размещение с общим центром или с перекрестными связями сегментов;

применять фиктивные элементы на краях массива пальцев транзисторов;

размещать транзисторы в областях с низким градиентом механического напряжения;

размещать транзисторы вдали от мощных элементов схемы;

не размещать контакты над рабочими затворами;

не проводить металлические шины через рабочие затворы;

размещать рабочие затворы вдали ото всех переходов с глубокой диффузией;

размещать точно согласованные транзисторы по осям симметрии кристалла;

не позволять краям скрытого слоя пересекать область рабочего затвора;

соединять затворы, набранные из пальцев, используя металлические связи.