- •Исследование, разработка и применение параметризованных аналоговых элементов в составе библиотеки аналоговых базовых и сложно-функциональных блоков.

- •210100 «Электроника и наноэлектроника»

- •Глава 1. Литературный обзор. 7

- •Глава 2. Исследование и разработка оптимальных параметризованных элементов второго уровня под выбранный класс задач. 30

- •Глава 3. Применение спроектированных параметризованных аналоговых ячеек второго уровня в составе базовых блоков. 81

- •Введение.

- •Положения, выносимые на защиту.

- •Основная часть. Глава 1. Литературный обзор.

- •Автоматизация проектирования аналоговых микросхем. Обзор существующих решений.

- •Pcell – определение, способы реализации и применение.

- •Аналоговые ячейки второго уровня. Их применение.

- •Специфика физического проектирования.

- •Причины рассогласования элементов и способы их устранения.

- •Построение согласованных элементов.

- •Размещение согласуемых элементов с общим центром.

- •Уменьшение технологического влияния соседних структур для лучшего согласования элементов.

- •Рекомендации по согласованию моп-транзисторов.

- •Рекомендации по согласованию конденсаторов.

- •Методы защиты от включения тиристорной защелки.

- •Язык skill. Краткие сведения.

- •Выводы.

- •Глава 2. Исследование и разработка оптимальных параметризованных элементов второго уровня под выбранный класс задач.

- •Введение.

- •Построение элементарных параметризованных ячеек.

- •Определение изменяемых параметров.

- •Создание топологических эскизов.

- •Построение ячейки транзистора на языке skill.

- •Оптимизация программного кода.

- •Построение параметризованных аналоговых ячеек второго уровня.

- •Способы применения элементарных ячеек в составе проектируемых аналоговых ячеек второго уровня.

- •Согласование элементов на примере построения матрицы согласованных конденсаторов с соотношением элементов 1:1.

- •Построение разводки.

- •Использование элементов защиты.

- •Способы задания изменяемых параметров и их ограничений.

- •Оптимизация ячеек.

- •Методика проектирования высокоточных параметризованных аналоговых ячеек второго уровня на языке skill.

- •Глава 3. Применение спроектированных параметризованных аналоговых ячеек второго уровня в составе базовых блоков.

- •Компаратор.

- •Операционный усилитель.

- •Устройство выборки и хранения (увх).

- •Преимущества и недостатки использования спроектированных параметризованных аналоговых ячеек второго уровня.

- •Заключение.

- •Список литературы.

- •Приложение.

Оптимизация ячеек.

По ходу разработки параметризованных ячеек производилась оптимизация их топологических представлений для получения высокоточных аналоговых схем. А также применялся ряд улучшений для удобства их использования.

Оценка топологических представлений. Выбор оптимального решения.

На рисунке 2.23 приведен первоначальный вариант топологии аналогового ключа. Но этот вариант не отвечает всем требованиям надежности. В нем не предусмотрены элементы защиты от антенного эффекта. При использовании такого варианта в ячейках с большими количеством транзисторов неизбежно падение напряжения и проявление эффекта электромиграции, так как шины имеют минимальные размеры. Если сделать ширину шин параметризованной, то при больших значениях заданной ширины охранные кольца будут располагаться на достаточно большом расстоянии от активных элементов, что влечет за собой опасность возникновения паразитного тиристора.

Рисунок 2.23. Первоначальный вариант топологии аналогового ключа.

Была проведена оптимизация ячейки. Нами были выбраны следующие критерии оптимизации:

Симметричность. Для согласованных элементов.

Надежность.

Защищенность от паразитных эффектов.

Высокая точность воспроизведения параметров.

Удобство использования.

Минимальная площадь.

Рисунок 2.24. Топология аналогового ключа после оптимизации.

В качестве оптимальной была выбрана конструкция, представленная на рисунке 2.24. Она симметрична. Вторая конструкция более удобна для использования. Так как мы создаем библиотеку для многократного использования, то этот критерий является очень важным. Вторая конструкция более надежна. Чем ближе находятся охранные кольца к активной области, тем лучше защита ячейки от паразитного тиристора и помех по подложке. Во второй конструкции предусмотрена защита от эффекта электромиграции и падения напряжения, так как возможно увеличение шин разводки и соответственно контактов к ним, что повышает надежность работы схемы. Единственным недостатком является увеличение площади ячейки.

Нам необходимо спроектировать комплементарные ключи, поэтому второй вариант ячейки более удобен для объединения n- и p- канальных ключей. Так как линии разводки выведены за пределы аналогового ключа у обеих ячеек, их можно будет объединить, что значительно сократит площадь. На рисунке 2.25 и 2.26 показаны топологии комплементарных ячеек до оптимизации и после соответсвтенно.

Рисунок.2.25. Первоначальный вариант топологии комплементарного аналогового ключа.

Рисунок.2.26. Топология комплементарного аналогового ключа после оптимизации.

На рисунках 2.27 приведен топологический эскиз матрицы согласованных конденсаторов, который был выбран за основу при проектировании ячейки. Он также удовлетворяет установленным требованиям.

Рисунок 2.27. Топологический эскиз матрицы согласованных конденсаторов.

Пользовательские улучшения.

На основе проведенных исследований было предложено использовать следующие улучшения ячеек второго уровня для удобства их использования. Для избежания эффекта электромиграции и критических значений падения напряжения предусмотрен параметр, который отвечает за ширину шин разводки. Для матрицы согласованных конденсаторов он один. Изменения топологии матрицы согласованных конденсаторов показано на рисунках 2.28 и 2.29.

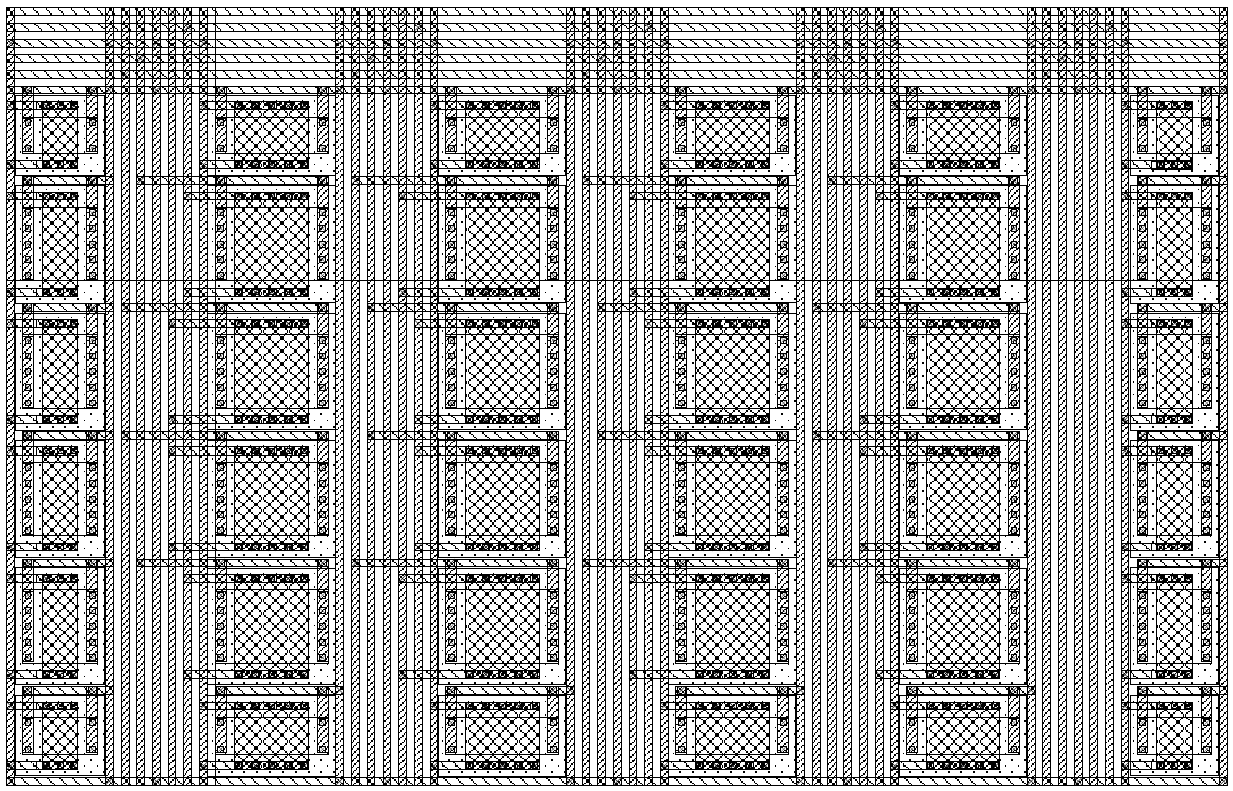

Рисунок. 2.28. Матрица согласованных конденсаторов с шириной шин разводки w = 0.32 мкм.

Рисунок. 2.29. Матрица согласованных конденсаторов с шириной шин разводки w = 2 мкм.

Для аналоговых ключей предусмотрено два параметра. Первый – для разводки затворов, второй – для разводки стока/истока. На рисунке 2.30 показаны варианты разводки при разных значениях ширины шин.

а)

б)

б)

Рисунок 2.30. Зависимость ширины шин от выставляемых параметра для аналоговых ключей: (а) – wшины стока/истока = 2u, wшины затвора = 1u, (б) – минимальная ширина шин разводки.

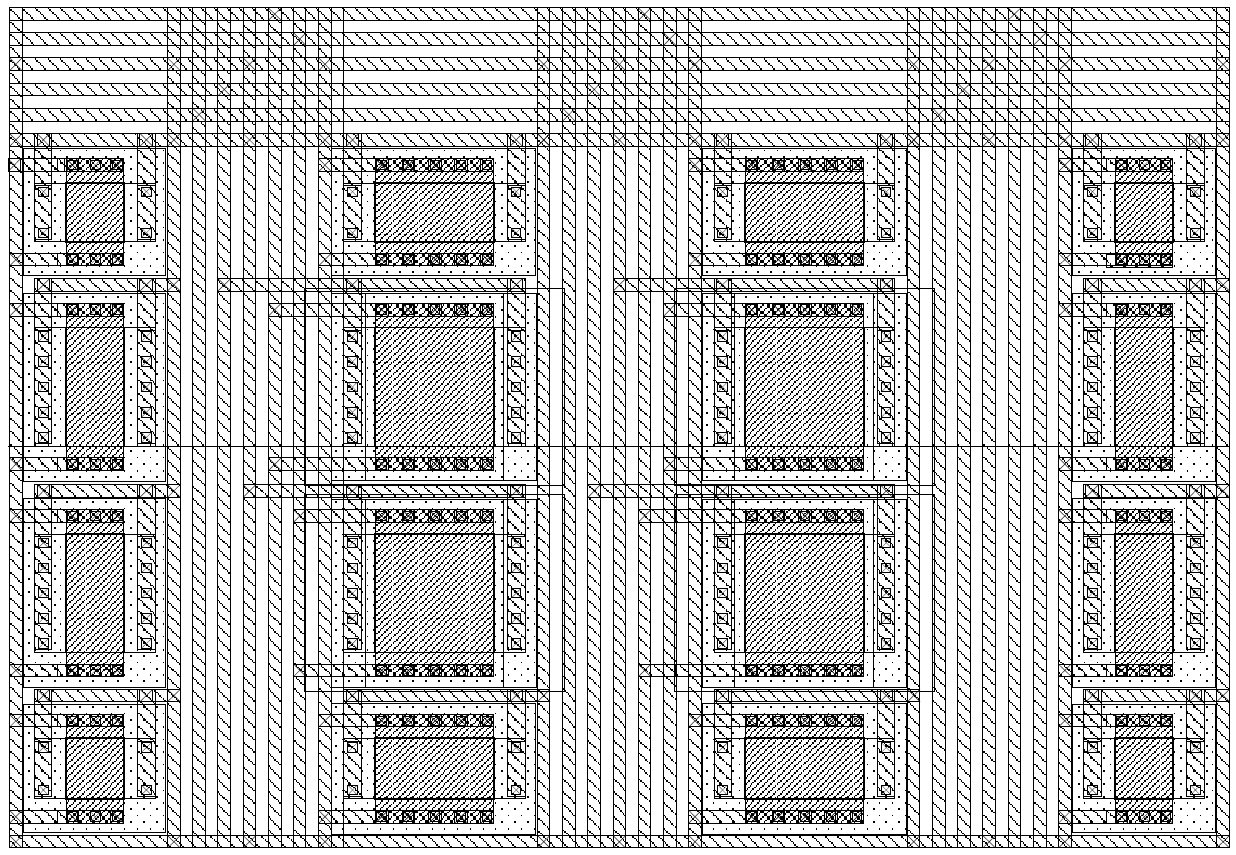

Для матрицы согласованных конденсаторов предусмотрен параметр, отвечающий за расположение разводки (Рис.2.29). На рисунках 2.31 и 2.32 показаны варианты расположения разводки, в зависимости от данного параметра.

Рисунок 2.31. Первый вариант расположения разводки в матрице согласованных конденсаторов.

Рисунок 2.32. Второй вариант расположения разводки в матрице согласованных конденсаторов.

Для различной конфигурации фиктивных элементов в матрице согласованных конденсаторов также предусмотрен параметр. На рисунках 2.33 и 2.34 показаны конфигурация топологии в зависимости от размеров фиктивных элементов.

Рисунок 2.33 Топология матрицы согласованных конденсаторов с размерами фиктивных элементов в 2 раза меньше рабочих конденсаторов.

Рисунок 2.34 Топология матрицы согласованных конденсаторов с размерами фиктивных элементов равными размерам рабочих конденсаторов.