- •1. Принципы Фон Неймана

- •2. Методы соединения устройств

- •4. Сложение и вычитание в прямом, обратном и дополнительном кодах

- •7.Устройства хранения данных

- •4.Накопитель на гибких магнитных дисках

- •8. Спец регистры Урок 2. Регистры микроконтроллера. Порты ввода/вывода

- •9. Шины данных

- •10. Преобразователи кодов. Виды индикаторов

- •11. Виды логики микросхем Микросхемы ттл

- •Микросхемы кмоп

- •12. Виды чисел ( Системы счисления)

- •Содержание

- •Позиционные системы счисления Введение

- •Зависимость плотности записи информации от основания системы счисления

- •Преобразование чисел

- •Шестидесятеричная система счисления

- •Двоичная система счисления

- •Троичная система счисления

- •Четверичная система счисления

- •Восьмеричная и шестнадцатеричная системы счислений

- •Десятичная система счисления

4. Сложение и вычитание в прямом, обратном и дополнительном кодах

Сложение в прямом коде чисел, имеющих одинаковые знаки, выполняется достаточно просто. Мантиссы складываются и сумме присваивается код знака слагаемых. Значительно более сложной является операция алгебраического сложения в прямом коде чисел с раз-

личными знаками. В этом случае приходится определять большое по модулю число, производить вычитание мантисс и присваивать разности знак большего (по модулю) числа. Таким образом, если положительные и отрицательные числа представлены в прямом коде, операции над кодами знаков и мантиссами выполняются раздельно.

Операция вычитания (алгебраического сложения) сводится к операции простого арифметического сложения при помощи обратного и дополнительного кодов, используемых для представления отрицательных чисел в машине. При этом операция сложения распространяется и на разряды знаков, рассматриваемых как разряды целой части числа.

Чтобы представить двоичное отрицательное число (1а) в обратном коде, нужно поставить в знаковый разряд единицу, а во всех других разрядах заменить единицы нулями, а нули — единицами:

(G-) обр = 1, σ1, σ 2, … , σ n (3)

σi = 1 при γi = 0 и σi = 0 при γi = 1.

При записи отрицательного числа в дополнительном коде ставят единицу в разряд знака, а цифровую часть числа заменяют дополнением модуля числа до целой единицы.

Отрицательное число G- = - 0, γ1, γ2, … , γn в дополнительном коде имеет вид:

(G-) доп = 1, ε1, ε 2, … , ε n (4)

где

0, ε1, ε 2, … , ε n = 1 - 0, γ1, γ2, … , γn (4a)

Установим связь между самим отрицательным числом G- и числами (G-)обр и (G-)доп , представляющими его обратный и дополнительный коды.

Вычитая (1а) из (3), имеем:

(G-) обр - G- = 1, σ1, σ 2, … , σ n – ( - 0, γ1, γ2, … , γn) = 1,11…1 = 2 – 2-n (так как σi + γi = 1)

Следовательно,

(G-) обр = G- + 2 - 2-n (4b)

Вычитая (1a) из (4), имеем:

(G-) доп - G- = 1, ε1, ε 2, … , ε n - ( - 0, γ1, γ2, … , γn) (5)

Учитывая (4a), получаем:

(G-) доп = G- + 2 (5а)

Из (5) и (5а) следует:

(G-) доп = (G-) обр + 2-n

где n — число разрядов в числе. Таким образом, дополнительный код может быть получен из обратного путем добавления к нему единицы младшего разряда.

Рассмотрим представление нуля. В процессе вычислений могут возникнуть «положительный» и «отрицательный» нули:

+ 0,00…0 ; - 0,00…0

Представление «положительного» нуля одинаково для прямого, обратного и дополнительного кодов:

(+ 0) пр = 0,00…0

Отрицательный нуль изображается: в прямом коде

(- 0) пр = 0,00…0

в обратном коде

(- 0) обр = 1,11…1

в дополнительном коде

(- 0) доп = 1,11…1 + 2-n = 0,00…0

так как перенос из разряда знака теряется.

Используя обратный или дополнительный код, можно операции вычитания и сложения чисел различных знаков свести к арифметическому сложению кодов чисел.

Рассмотрим использование обратного кода при алгебраическом сложении двух двоичных чисел G и Q, когда одно из них или оба числа отрицательны. Для этого случая может быть сформулировано следующее правило (предполагаем, что модуль алгебраической суммы меньше единицы).

При алгебраическом сложении двух двоичных чисел с использованием обратного кода положительные слагаемые представляются в прямом коде, а отрицательные - в обратном и производится арифметическое суммирование этих кодов, включая разряды знаков, которые при этом рассматриваются как разряды целых единиц. При возникновении переноса из разряда знака единица переноса прибавляется к младшему разряду суммы кодов (такой перенос называется круговым или циклическим). В результате получается алгебраическая сумма в прямом коде, если эта сумма положительна, и в обратном коде, если она отрицательна.

Рассмотрим теперь использование дополнительного кода для алгебраического сложения. Приведем соответствующее правило (полагаем, что модуль алгебраической суммы меньше единицы).

При алгебраическом сложении двух двоичных чисел с использованием дополнительного кода положительные слагаемые представляются в прямом коде, а отрицательные — в дополнительном и производится арифметическое суммирование этих кодов, включая разряды знаков, которые при этом рассматриваются как разряды целых единиц. При возникновении переноса из разряда знака единица переноса отбрасывается. В результате получается алгебраическая сумма в прямом коде, если эта сумма положительна, и в дополнительном коде, если эта сумма отрицательна.

В самом деле, если G- < 0 и Q- < 0 , то согласно (4b):

(G-) доп + (Q-) доп = G- + 2 + G- + 2 = 2 + (G- + Q- + 2)

Так как -1 < G- + Q- < 0, то величина, стоящая в скобках, меньше двух, но больше единицы. Двойка, стоящая вне скобки, образует перенос из разряда знака, который будет отброшен. В результате получаем:

(G-) доп + (Q-) доп = (G- + Q-) + 2 = (G- + Q-) доп

G+ > 0, а Q- < 0, то

(G+) пр + (Q-) доп = (G+ + Q-) + 2

Если при этом 0 < G+ + Q- < 1, то стоящая вне скобки двойка дает единицу переноса из разряда знака, которая отбрасывается. При этом получаем:

(G+) пр + (Q-) доп = (G+ + Q-) пр

(G+ + Q- > 0)

Если же -1 < G+ + Q- < 0, то (G+ + Q- ) + 2 < 2 и переноса из разряда знака не возникает. В этом случае:

(G+) пр + (Q-) доп = (G+ + Q-) доп

(G+ + Q- < 0).

Применение дополнительного или обратного кода для представления отрицательных чисел упрощает операцию алгебраического сложения. Алгебраическое сложение чисел с разными знаками заменяется арифметическим сложением кодов, при этом автоматически получается код знака результата. Однако остается нерешенным вопрос о выработке признака переполнения разрядной сетки.

При сложении кодов теряется единица переноса из разряда целых единиц и результат ошибочно воспринимается как положительное число, меньшее единицы.

Отметим, что при алгебраическом сложении двух чисел G и Q, каждое из которых по модулю меньше единицы, может возникнуть переполнение разрядной сетки, но при этом модуль получаемой суммы всегда меньше двух. Это обстоятельство облегчает построение кодов, по виду которых можно судить о переполнении разрядной сетки.

Для получения признака переполнения разрядной сетки применяют модифицированные прямой, дополнительный и обратный коды. Эти коды отличаются от ранее рассмотренных кодов тем, что для представления знака используются два разряда.

При этом знак плюс обозначается 00, а знак минус — 11. При алгебраическом сложении чисел знаковые разряды рассматриваются как разряды целой части числа.

При возникновении переноса единицы из старшего разряда знака эта единица отбрасывается, если отрицательные числа представляются модифицированным дополнительным кодом, или производится циклический перенос в младший разряд мантиссы, если отрицательные числа изображаются модифицированным обратным кодом.

При алгебраическом сложении на переполнение разрядной сетки (модуль алгебраической суммы больше единицы) указывает несовпадение цифр в знаковых разрядах. Комбинации 01 в знаковых разрядах соответствует положительное число, а комбинации 10 — отрицательное число.

В этих случаях модуль суммы:

1 ≤ |x| < 2

Отметим также особенности нормализации и выполнения сдвига для отрицательных чисел, представленных в дополнительном (обратном) коде.

У нормализованного положительного или отрицательного числа с мантиссой, изображаемой в прямом коде, цифра в старшем S-ичном разряде мантиссы должна быть отлична от нуля. Для отрицательных мантисс, представленных в обратном или дополнительном коде, условие нормализации |q| ≥ 1/S выполняется, если цифра в старшем S-ичном разряде мантиссы есть нуль.

В случае чисел с плавающей запятой комбинации 01 и 10 в знаковых разрядах мантиссы указывают на нарушение нормализации влево, а комбинации цифр 00 и 1 σs1 (σs1 ≠ 0) в младшем знаковом разряде и старшем S-ичном цифровом разряде мантиссы сигнализируют о нарушении нормализации вправо. Для восстановления нормализации производится сдвиг мантиссы вправо (или влево) на нужное число разрядов, при этом порядок увеличивается (уменьшается) на соответствующее число единиц,

Если отрицательные числа представляются в дополнительном (обратном) коде, сдвиг производится по особым правилам («модифицированный сдвиг»), с тем чтобы в результате сдвига дополнительного (обратного) кода числа х на m S-ичных разрядов получился дополнительный (обратный) код числа Smx или S-mх соответственно для сдвига влево или вправо.

При модифицированном сдвиге дополнительного (обратного) кода вправо в освобождающиеся старшие разряды мантиссы записываются единицы, а при сдвиге влево единицы записываются в освобождающиеся младшие разряды.

5. ОЗУ

Запоминающие устройства (ЗУ) служат для приема, хранения и выдачи информации. Запоминающие устройства по выполняемым функциям делятся на оперативные и постоянные. Оперативные запоминающие устройства (ОЗУ) осуществляют запись, хранение и считывание информации и работают только при включенном питании, т. е. ОЗУ являются энергозависимыми. Постоянные запоминающие устройства (ПЗУ) хранят информацию при отключении питания, т. е. ПЗУ являются энергонезависимыми.

ОЗУ по виду хранения информации разделяются на статические и динамические. В статическом ОЗУ в качестве элемента памяти используется триггер, в динамическом - конденсатор. По-буржуйски ОЗУ называется RAM (random access memory - память с произвольным доступом). Статическое ОЗУ соответственно SRAM, динамическое DRAM.

Статическое ОЗУ

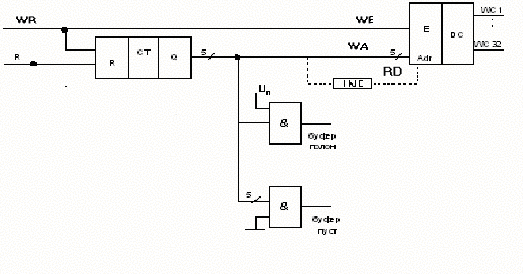

На рисунке 1 показана структура статического запоминающего устройства.

Рис. 1 - Структура статического ОЗУ

ЭП - это элемент памяти. Еще его называют запоминающим элементом (ЗЭ). Все эти элементы памяти заключены в матрице накопителя. Число элементов равно 2n, где n - целое число. Каждый конкретный ЭП хранит один бит информации и имеет свой адрес, задаваемый n-разрядным двоичным кодом. Для удобства адрес разбивают на две части (обычно одинаковые) - адрес строки и адрес столбца. В итоге получается прямоугольная матрица, содержащая 2k строк и 2m столбцов. Всего элементов памяти будет 2k+m. Поскольку число строк и число столбцов значительно больше, чем разрядность двоичного числа, между адресными входами и матрицей элементов памяти ставят дешифраторы, на рисунке обозначенные как дешифратор строк и дешифратор столбцов. Иногда в структуре микросхем ОЗУ между дешифратором столбцов и матрицей накопителя изображают ключи выбора столбцов.

Рассмотрим один из вариантов исполнения элемента памяти статического ОЗУ. Вот схемка:

Рис. 2 - Элемент памяти статического ОЗУ

Собственно элементом памяти является D-триггер, находящийся на пересечении i-й строки и j-го столбца. Для уменьшения количества выводов микросхем ОЗУ совмещают входы и выходы в них. Поэтому на схеме введен еще и электронный ключ SW. При уровнях лог. 1 на линиях i и j и при подаче сигнала разрешения записи WR=1 (от буржуйского write - записывать), в триггер записывается информация, которая поступает на вход D. При этом шина Вх./Вых. оказывается подключенной к D входу триггера через электронный ключ SW и выполняет функции входа, при снятии сигнала WR ключ подключает к шине Вх./Вых. выход триггера, и эта шина выполняет функции выхода.

Если оператива одноразрядная, то шина Вх./Вых. будет общей для всех элементов памяти. Но чаще оперативы многоразрядные и в этом случае на каждой паре линий строка-столбец располагается по n триггеров и n ключей, где n-число разрядов, а элемент "И" при этом остается один. Естественно, что каждый из ключей подключается к своей шине Вх./Вых.

Помимо режимов записи и считывания, которые определяются потенциалом на входе WR, существует режим хранения данных, в котором запись и считывание запрещены. Режим хранения имеет двоякий смысл. Во-первых, если в устройстве много микросхем ОЗУ, что характерно, то запись или считывание ведется по одной микросхеме, остальные в этом случае должны быть отключены. Во-вторых, в режиме хранения данных энергопотребление намного меньше, чем в режиме записи и считывания (рабочий режим). Для перевода оперативы в режим хранения используется сигнал CS, по-буржуйски crystal selection - выбор кристалла. Обычно для перевода в режим хранения на вход CS подается уровень лог. 1, для перевода в рабочий режим - лог. 0.

Динамическое ОЗУ

Как говорилось ранее, в динамическом ОЗУ функции элемента памяти выполняет кондер. Информация представляется электрическим зарядом, к примеру, если есть заряд на кондере, значит в элемент памяти записана лог. 1, нет заряда - лог. 0. Ну а поскольку время сохранения на кондере заряда ограничено (вследствие утечки), необходимо периодически восстанавливать записанную информацию. Этот процесс красиво зовется регенерацией. Помимо этого, для динамического ОЗУ требуется синхронизация, обеспечивающая последовательность включений функциональных узлов.

Для реализации элемента памяти динамического ОЗУ широко применяется схема, показанная на рисунке 3.

Рис. 3 - Элемент памяти динамического ОЗУ

Выбор элемента памяти производится сигналом лог. 1 на шине строки. Транзистор VT2 открывается и соединяет кондер С1 с шиной столбца. РШ - разрядная шина. Предварительно через транзистор VT1, который открывается сигналом "Такт (С)", заряжается емкость Сш до напряжения U0. Емкость Сш должна значительно превышать емкость С1.

Элемент памяти динамического ОЗУ проще, чем статического, поэтому объем памяти в динамических ОЗУ выше, чем в статических. Соответственно, при большой разрядности адреса его делят на две части. Первая называется RAS, что по-буржуйски означает row access signal - сигнал выборки строки, вторая - CAS, на буржуйском означающая column access signal - сигнал выборки столбца. Сигналы RAS и CAS сдвинуты друг относительно друга во времени, сигнал разрешения записи WR должен появляться при введении обеих частей адреса. Одновременно с WR вводится информационный сигнал. В режиме считывания информационный сигнал появляется на выходе с некоторой задержкой, относительно сигнала CAS.

На последок табличка с обозначением сигналов микросхем памяти:

Сигнал |

Обозначение |

Адрес |

А |

Тактовый сигнал |

С |

Строб адреса столбца |

CAS |

Строб адреса строки |

RAS |

Выбор микросхемы |

CS |

Разрешение |

CE |

Запись |

WR |

Считывание |

RD |

Запись-считывание |

W/R |

Разрешение записи |

WE |

Разрешение по выходу |

OE |

Данные (информация) |

D |

Входные данные |

DI |

Выходные данные |

DO |

Адрес, данные; вход, выход |

ADIO |

Данные вход, выход |

DIO |

Регенерация |

REF |

Программирование |

PR |

Стирание |

ER |

Напряжение питания |

Ucc |

Напряжение программирования |

UPR |

Общий вывод |

OV |

Оперативная память (также оперативное запоминающее устройство, ОЗУ) — в информатике — память, часть системы памяти ЭВМ, в которую процессор может обратиться за одну операцию (jump, move и т. п.). Предназначена для временного хранения данных и команд, необходимых процессору для выполнения им операций. Оперативная память передаёт процессору данные непосредственно, либо через кеш-память. Каждая ячейка оперативной памяти имеет свой индивидуальный адрес. ОЗУ может изготавливаться как отдельный блок, или входить в конструкцию однокристальной ЭВМ или микроконтроллера.

Запоминающее

устройство с произвольным доступом

— ЗУПВ (или Запоминающее устройство

произвольной выборки — ЗУПВ) (от англ.

Random

Access Memory)

— один из видов памяти, позволяющий в

любой момент времени получить доступ

к любой ячейке по её адресу на чтение

или запись.

ЗУПВ используются в

качестве оперативной памяти персонального

компьютера.

Предназначены для

записи, хранения и считывания информации

в процессе её обработки. Подразделяются

на статические и динамические. В

статических ОЗУ запоминающий элемент

представляет собой триггер, изготовленные

по той или иной технологии (ТТЛ, ЭСЛ,

КМОП и др.), что позволяет считывание

информации без её потери. В динамических

ОЗУ элементом памяти является ёмкость

(например, входная ёмкость полевого

транзистора), что требует восстановления

записанной информации в процессе её

хранения и использования. Это усложняет

применение ОЗУ динамического типа, но

позволяет реализовать больший объём

памяти. В современных динамических ОЗУ

имеются встроенные системы синхронизации

и регенерации, поэтому по внешним

сигналам управления они не отличаются

от статических.

Виды

ЗУПВ:

Полупроводниковая

статическая

(SRAM)

— ячейки представляют собой

полупроводниковые триггеры. Достоинства

— небольшое энергопотребление, высокое

быстродействие. Отсутствие необходимости

производить «регенерацию». Недостатки

— малый объём, высокая стоимость. Сейчас

широко используется в качестве кеш-памяти

процессоров в компьютерах.

Полупроводниковая

динамическая

(DRAM)

— каждая ячейка представляет собой

конденсатор на основе перехода

КМОП-транзистора. Достоинства — низкая

стоимость, большой объём. Недостатки —

необходимость периодического считывания

и перезаписи каждой ячейки — т. н.

«регенерации», и, как следствие, понижение

быстродействия, большое энергопотребление.

Процесс регенерации реализуется

специальным контроллером, установленным

на материнской плате или в центральном

процессоре. DRAM обычно используется в

качестве оперативной памяти (ОЗУ)

компьютеров.

Ферромагнитная

— представляет собой матрицу из

проводников, на пересечении которых

находятся кольца или биаксы, изготовленные

из ферромагнитных материалов. Достоинства

— устойчивость к радиации, сохранение

информации при выключении питания;

недостатки — малая ёмкость, большой

вес, стирание информации при каждом

чтении. В настоящее время в таком,

собранном из дискретных компонентов

виде, не применяется. Однако к 2003 году

появилась магнитная память MRAM в

интегральном исполнении. Сочетая

скорость SRAM и возможность хранения

информации при отключённом питании,

MRAM является перспективной заменой

используемым ныне типам ROM и RAM. Однако

она на сегодняшний день (2006 год)

приблизительно вдвое дороже микросхем

SRAM (при той же ёмкости и габаритах).

На

сегодня наибольшее распространение

имеют два вида ОЗУ:

SRAM

(Static RAM)

ОЗУ,

собранное на триггерах, называется

статической памятью с произвольным

доступом, или просто статической памятью.

Достоинство этого вида памяти — скорость.

Поскольку триггеры собраны на вентилях,

а время задержки вентиля очень мало, то

и переключение состояния триггера

происходит очень быстро. Данный вид

памяти не лишён недостатков. Во-первых,

группа транзисторов, входящих в состав

триггера, обходится дороже, даже если

они вытравляются миллионами на одной

кремниевой подложке. Кроме того, группа

транзисторов занимает гораздо больше

места, поскольку между транзисторами,

которые образуют триггер, должны быть

вытравлены линии связи.

D

RAM

(Dynamic RAM)

Более

экономичной вид памяти. Для хранения

разряда (бита) используется схема,

состоящая из одного конденсатора и

одного транзистора (в некоторых вариациях

конденсаторов два). Такой вид памяти

решает, во-первых, проблему дороговизны

(один конденсатор и один транзистор

дешевле нескольких транзисторов) и,

во-вторых, компактности (там, где в SRAM

размещается один триггер, то есть один

бит, можно уместить восемь конденсаторов

и транзисторов). Есть и свои минусы.

Во-первых, память на основе конденсаторов

работает медленнее, поскольку если в

SRAM изменение напряжения на входе триггера

сразу же приводит к изменению его

состояния, то для того, чтобы установить

в 1 бит на основе конденсатора, этот

конденсатор нужно зарядить, а для того,

чтобы бит установить в 0, соответственно,

разрядить. А это гораздо более длительные

(в 10 и более раз) операции, чем переключение

триггера, даже если конденсатор имеет

весьма небольшие размеры. Второй

существенный минус — конденсаторы

склонны к «стеканию» заряда; проще

говоря, со временем конденсаторы

разряжаются. Причём разряжаются они

тем быстрее, чем меньше их ёмкость. В

связи с этим обстоятельством, дабы не

потерять содержимое битов, конденсаторы

необходимо регенерировать через

определённый интервал времени, чтобы

восстанавливать заряд. Регенерация

выполняется путем считывания заряда

(через транзистор). Контроллер памяти

периодически приостанавливает все

операции с памятью для регенерации её

содержимого, что значительно снижает

производительность данного вида ОЗУ.

Память на конденсаторах получила своё

название Dynamic RAM (динамическая память)

как раз за то, что разряды в ней хранятся

не статически, а «стекают» динамически

во времени.

Таким образом, DRAM

дешевле SRAM и её плотность выше, что

позволяет на том же пространстве

кремниевой подложки размещать больше

битов, но при этом её быстродействие

ниже. SRAM, наоборот, более быстрая память,

но зато и дороже. В связи с этим обычную

память строят на модулях DRAM, а SRAM

используется для построения, например,

кеш-памяти в микропроцессорах.

Статическая

оперативная память с произвольным

доступом

(SRAM

— Static

Random Access Memory)

— полупроводниковая оперативная память,

в которой каждый двоичный или троичный

разряд хранится в схеме с положительной

обратной связью, позволяющей поддерживать

состояние сигнала без постоянной

перезаписи, необходимой в динамической

памяти (DRAM). Произвольный доступ (RAM —

random access memory) — возможность выбирать для

записи/чтения любой из битов (тритов)

(чаще байтов (трайтов), зависит от

особенностей конструкции), в отличие

от памяти с последовательным доступом

(SAM — sequental access memory).

Типичная ячейка

статической двоичной памяти (двоичный

триггер) на КМОП-технологии состоит из

двух перекрёстно (кольцом) включенных

инверторов и ключевых транзисторов для

обеспечения доступа к ячейке (рис.1.).

Часто для увеличения плотности упаковки

элементов на кристалле в качестве

нагрузки применяют поликремниевые

резисторы. Недостатком такого решения

является рост статического

энергопотребления.

Линия WL (Word

Line) управляет двумя транзисторами

доступа. Линии BL и BL - битовые линии,

используются и для записи данных и для

чтения данных.

Преимущества:

·

Быстрый доступ. SRAM — это действительно

память произвольного доступа, доступ

к любой ячейке памяти в любой момент

занимает одно и то же время.

·

Простая схемотехника — SRAM не требуются

сложные контроллеры.

·

Возможны очень низкие частоты

синхронизации, вплоть до полной остановки

синхроимпульсов.

Недостатки

·

Высокое энергопотребление.

·

Невысокая плотность записи (шесть

элементов на бит, вместо двух у DRAM).

· Вследствие

чего — дороговизна килобайта памяти.

Тем

не менее, высокое энергопотребление не

является принципиальной особенностью

SRAM, оно обусловлено высокими скоростями

обмена с данным видом внутренней памяти

процессора. Энергия потребляется только

в момент изменения информации в ячейке

SRAM.

Применение:

SRAM применяется

в микроконтроллерах и ПЛИС, в которых

объём ОЗУ невелик (единицы килобайт),

зато нужны низкое энергопотребление

(за счёт отсутствия сложного контроллера

динамической памяти), предсказываемое

с точностью до такта время работы

подпрограмм и отладка прямо на

устройстве.

В устройствах с большим

объёмом ОЗУ рабочая память выполняется

как DRAM. SRAM’ом же делают регистры и

кэш-память.

DRAM

(Dynamic

Random Access Memory)

— один из видов компьютерной памяти с

произвольным доступом (RAM), наиболее

широко используемый в качестве ОЗУ

современных компьютеров.

Конструктивно

память DRAM состоит из «ячеек» размером

в 1 или 4 бит, в каждой из которых можно

хранить определённый объём данных.

Совокупность «ячеек» такой памяти

образуют условный «прямоугольник»,

состоящий из определённого количества

строк и столбцов. Один такой «прямоугольник»

называется страницей, а совокупность

страниц называется банком. Весь набор

«ячеек» условно делится на несколько

областей.

Принцип

действия

Физическое

представление:

В

современных компьютерах физически

DRAM-память представляет собой электрическую

плату — модуль, на котором расположены

микросхемы памяти и разъём, необходимый

для подключения модуля к материнской

плате. Роль «ячеек» играют конденсаторы

и транзисторы, расположенные внутри

микросхем памяти. Конденсаторы заряжаются

в случае, когда в «ячейку» заносится

единичный бит, либо разряжаются в случае,

когда в «ячейку» заносится нулевой бит.

Транзисторы необходимы для удержания

заряда внутри конденсатора. При отсутствии

подачи электроэнергии к оперативной

памяти, происходит разряд конденсаторов,

и память опустошается. Это динамическое

изменение заряда конденсатора является

основополагающим принципом работы

памяти типа DRAM. Элементом памяти этого

типа является чувствительный усилитель

(англ. sense amp), подключенный к каждому из

столбцов «прямоугольника». Он, реагируя

на слабый поток электронов, устремившихся

через открытые транзисторы с обкладок

конденсаторов, считывает всю страницу

целиком. Именно страница является

минимальной порцией обмена с динамической

памятью, потому что обмен данными с

отдельно взятой ячейкой

невозможен.

Характеристики

памяти DRAM:

Основными

характеристиками DRAM являются тайминги

и рабочая частота. Для обращения к ячейке

контроллер задаёт номер банка, номер

страницы в нём, номер строки и номер

столбца, на все запросы тратится время,

помимо этого довольно большой период

уходит на открытие и закрытие банка

после самой операции. На каждое действие

требуется время, называемое таймингом.

Основными таймингами DRAM являются:

задержка между подачей номера строки

и номера столбца, называемая временем

полного доступа (англ. RAS to CAS delay), задержка

между подачей номера столбца и получением

содержимого ячейки, называемая временем

рабочего цикла (англ. CAS delay), задержка

между чтением последней ячейки и подачей

номера новой строки (англ. RAS precharge).

Тайминги измеряются в наносекундах, и

чем меньше величина этих таймингов, тем

быстрее работает оперативная память.

Рабочая частота измеряется в мегагерцах,

и увеличение рабочей частоты памяти

приводит к увеличению её

быстродействия

Регенерация

В

отличие от статической памяти типа SRAM

(англ. static random access memory), которая является

конструктивно более сложным и более

дорогим типом памяти RAM и используется

в основном в кэш—памяти, память DRAM

изготавливается на основе конденсаторов

небольшой ёмкости, которые быстро теряют

заряд, поэтому информацию приходится

обновлять через определённые периоды

времени во избежание потерь данных.

Этот процесс называется регенерацией

памяти. Он реализуется специальным

контроллером, установленным на материнской

плате или на кристалле центрального

процессора. На протяжении времени,

называемого шагом регенерации, в DRAM

перезаписывается целая строка «ячеек»,

и через 8-64 мс обновляются все строки

памяти.

Процесс регенерации памяти

в классическом варианте существенно

«тормозит» работу системы, поскольку

в это время обмен данными с памятью

невозможен. Регенерация, основанная на

обычном переборе строк, не применяется

в современных типах DRAM. Существует

несколько более экономичных вариантов

этого процесса — расширенный, пакетный,

распределенный; наиболее экономичной

является скрытая регенерация.

Из

новых технологий регенерации можно

выделить тип регенерации PASR (англ.

Partial Array Self Refresh), применяемый компанией

Samsung в чипах памяти SDRAM с низким уровнем

энергопотребления. Регенерация «ячеек»

выполняется только в период ожидания

в тех банках памяти, в которых имеются

данные. Параллельно с этой технологией

реализуется метод TCSR (англ. Temperature

Compensated Self Refresh), который предназначен

для регулировки скорости процесса

регенерации в зависимости от рабочей

температуры.

Типы

DRAM

На

протяжении долгого времени разработчиками

создавались различные типы памяти. Они

обладали разными характеристиками, в

них были использованы разные технические

решения. Основной движущей силой развития

памяти было развитие ЭВМ и центральных

процессоров. Постоянно требовалось

увеличение быстродействия и объёма

оперативной памяти.

Страничная

память

Страничная

память (англ. page mode DRAM, PM DRAM) являлась

одним из первых типов выпускаемой

компьютерной оперативной памяти. Память

такого типа выпускалась в начале 90-х

годов, но с ростом производительности

центральных процессоров и ресурсоёмкости

приложений требовалось увеличивать не

только объём памяти, но и скорость её

работы.

Быстрая

страничная память

Быстрая

страничная память (англ. fast page mode DRAM, FPM

DRAM) появилась в 1995 году. Принципиально

новых изменений память не претерпела,

а увеличение скорости работы достигалось

путём повышенной нагрузки на аппаратную

часть памяти. Данный тип памяти в основном

применялся для компьютеров с процессорами

Intel 80486 или аналогичных процессоров

других фирм. Память могла работать на

частотах 25 МГц и 33 МГц с временем полного

доступа 70 нс и 60 нс и с временем рабочего

цикла 40 нс и 35 нс соответственно.

Память

с усовершенствованным выходом

C

появлением процессоров Intel Pentium память

FPM DRAM оказалась совершенно неэффективной.

Поэтому следующим шагом стала память

с усовершенствованным выходом (англ.

extended data out DRAM, EDO DRAM). Эта память появилась

на рынке в 1996 году и стала активно

использоваться на компьютерах с

процессорами Intel Pentium и выше. Её

производительность оказалась на 10—15

% выше по сравнению с памятью типа FPM

DRAM. Её рабочая частота была 40 МГц и 50

МГц, соответственно, время полного

доступа — 60 нс и 50 нс, а время рабочего

цикла — 25 нс и 20 нс. Эта память содержит

регистр-защелку (англ. data latch) выходных

данных, что обеспечивает некоторую

конвейеризацию работы для повышения

производительности при чтении.

Синхронная

DRAM

В

связи с выпуском новых процессоров и

постепенным увеличением частоты

системной шины, стабильность работы

памяти типа EDO DRAM стала заметно падать.

Ей на смену пришла синхронная память

(англ. synchronous DRAM, SDRAM). Новыми особенностями

этого типа памяти являлись использование

тактового генератора для синхронизации

всех сигналов и использование конвейерной

обработки информации. Также память

надёжно работала на более высоких

частотах системной шины (100 МГц и выше).

Недостатками данного типа памяти

являлась его высокая цена, а также его

несовместимость со многими чипсетами

и материнскими платами в силу своих

новых конструктивных особенностей.

Рабочие частоты этого типа памяти могли

равняться 66 МГц, 100 МГц или 133 МГц, время

полного доступа — 40 нс и 30 нс, а время

рабочего цикла — 10 нс и 7,5 нс.

Пакетная

EDO RAM

Пакетная

память EDO RAM (англ. burst extended data output DRAM, BEDO

DRAM) стала дешёвой альтернативой памяти

типа SDRAM. Основанная на памяти EDO DRAM, её

ключевой особенностью являлась технология

поблочного чтения данных (блок данных

читался за один такт), что сделало её

работу быстрее, чем у памяти типа SDRAM.

Однако невозможность работать на частоте

системной шины более 66 МГц не позволила

данному типу памяти стать популярным.

Video

RAM

Cпециальный

тип оперативной памяти Video RAM (VRAM) был

разработан на основе памяти типа SDRAM

для использования в видеоплатах. Он

позволял обеспечить непрерывный поток

данных в процессе обновления изображения,

что было необходимо для реализации

изображений высокого качества. На основе

памяти типа VRAM, появилась спецификация

памяти типа Windows RAM (WRAM), иногда её ошибочно

связывают с операционными системами

семейства Windows. Её производительность

стала на 25 % выше, чем у оригинальной

памяти типа SDRAM, благодаря некоторым

техническим изменениям.

DDR

SDRAM

По

сравнению с обычной памятью типа SDRAM, в

памяти SDRAM с удвоенной скоростью передачи

данных (англ. double data rate SDRAM, DDR SDRAM или

SDRAM II) была вдвое увеличена пропускная

способность. Первоначально память

такого типа применялась в видеоплатах,

но позднее появилась поддержка DDR SDRAM

со стороны чипсетов. Она работает на

частотах в 100 МГц и 133 МГц, её время полного

доступа — 30 нс и 22,5 нс, а время рабочего

цикла — 5 нс и 3,75 нс.

Direct

RDRAM, или Direct Rambus DRAM

Тип

памяти RDRAM является разработкой компании

Rambus. Высокое быстродействие этой памяти

достигается рядом особенностей, не

встречающихся в других типах памяти.

Первоначальная очень высокая стоимость

памяти RDRAM привела к тому, что производители

мощных компьютеров предпочли менее

производительную, зато более дешёвую

память DDR SDRAM. Рабочие частоты памяти —

400 МГц, 600 МГц и 800 МГц, время полного

доступа — до 30 нс, время рабочего цикла

— до 2,5 нс.

DDR2

SDRAM

Конструктивно

новый тип оперативной памяти DDR2 SDRAM был

выпущен в 2004 году. Основываясь на

технологии DDR SDRAM, этот тип памяти за

счёт технических изменений показывает

более высокое быстродействие и

предназначен для использования на

современных компьютерах. Память может

работать на частотах в 200 МГц, 266 МГц, 333

МГц и 400 МГц. Время полного доступа — 25

нс, 11,25 нс, 9 нс, 7,5 нс. Время рабочего цикла

— 5 нс, 3,75 нс, 3 нс, 3,5 нс.

Корпуса

Различные

корпуса DRAM. Сверху вниз: DIP, SIP, SIMM

(30-контактный), SIMM (72-контактный), DIMM

(168-контактный), DIMM (184-контактный,

DDR)Элементы памяти типа DRAM конструктивно

выполняют либо в виде отдельных микросхем

в корпусах типа DIP, либо в виде модулей

памяти типа: SIP (Single In-Line Package), SIMM (Single

In-line Memory Module), DIMM (Dual In-line Memory Module), RIMM

(Rambus In-line Memory Module). Микросхемы в корпусах

типа DIP выпускались до использования

модулей памяти. Эти микросхемы имеют

два ряда контактов, расположенных вдоль

длинных сторон чипа и загнутых вниз.

Модули

SIP

Модули

типа SIP представляют собой прямоугольные

платы с контактами в виде маленьких

штырьков. Этот тип памяти в настоящее

время практически не используется, так

как был вытеснен модулями памяти типа

SIMM.

Модули

SIMM

Модули

типа SIMM представляют собой прямоугольную

плату с контактной полосой вдоль одной

из сторон, модули фиксируются в разъёме

поворотом с помощью защёлок. Наиболее

распространены 30- и 72-контактные SIMM.

Широкое распространение нашли SIMM на 4,

8, 16, 32 и даже 64 Мбайт.

Модули

DIMM

Модули

типа DIMM наиболее распространены в виде

168-контактных модулей, устанавливаемых

в разъём вертикально и фиксируемых

защёлками. В портативных устройствах

широко применяются SO DIMM — разновидность

DIMM малого размера (англ. SO — small outline),

они предназначены в первую очередь для

портативных компьютеров. Наиболее часто

встречаются 72- и 144-контактные модули

типа SO DIMM. Память типа DDR SDRAM выпускается

в виде 184-контактных DIMM-модулей, а для

памяти типа DDR2 SDRAM выпускаются

240-контактные модули.

Модули

RIMM

Модули

типа RIMM менее распространены, в таких

модулях выпускается память типа Direct

RDRAM. Они представлены 168/184-контактными

прямоугольными платами, которые

обязательно должны устанавливаться

только в парах, а пустые разъёмы на

материнской плате занимаются специальными

заглушками. Это связано с особенностями

конструкции таких модулей. Так же

существуют модули 232-pin PC1066 RDRAM RIMM 4200, не

совместимые с 184-контактными разъёмами.

Запоминающее

устройство с произвольным доступом

— ЗУПВ (или Запоминающее устройство

произвольной выборки — ЗУПВ) (от англ.

Random

Access Memory)

— один из видов памяти, позволяющий в

любой момент времени получить доступ

к любой ячейке по её адресу на чтение

или запись.

ЗУПВ используются в

качестве оперативной памяти персонального

компьютера.

Предназначены для

записи, хранения и считывания информации

в процессе её обработки. Подразделяются

на статические и динамические. В

статических ОЗУ запоминающий элемент

представляет собой триггер, изготовленные

по той или иной технологии (ТТЛ, ЭСЛ,

КМОП и др.), что позволяет считывание

информации без её потери. В динамических

ОЗУ элементом памяти является ёмкость

(например, входная ёмкость полевого

транзистора), что требует восстановления

записанной информации в процессе её

хранения и использования. Это усложняет

применение ОЗУ динамического типа, но

позволяет реализовать больший объём

памяти. В современных динамических ОЗУ

имеются встроенные системы синхронизации

и регенерации, поэтому по внешним

сигналам управления они не отличаются

от статических.

Виды

ЗУПВ:

Полупроводниковая

статическая

(SRAM)

— ячейки представляют собой

полупроводниковые триггеры. Достоинства

— небольшое энергопотребление, высокое

быстродействие. Отсутствие необходимости

производить «регенерацию». Недостатки

— малый объём, высокая стоимость. Сейчас

широко используется в качестве кеш-памяти

процессоров в компьютерах.

Полупроводниковая

динамическая

(DRAM)

— каждая ячейка представляет собой

конденсатор на основе перехода

КМОП-транзистора. Достоинства — низкая

стоимость, большой объём. Недостатки —

необходимость периодического считывания

и перезаписи каждой ячейки — т. н.

«регенерации», и, как следствие, понижение

быстродействия, большое энергопотребление.

Процесс регенерации реализуется

специальным контроллером, установленным

на материнской плате или в центральном

процессоре. DRAM обычно используется в

качестве оперативной памяти (ОЗУ)

компьютеров.

Ферромагнитная

— представляет собой матрицу из

проводников, на пересечении которых

находятся кольца или биаксы, изготовленные

из ферромагнитных материалов. Достоинства

— устойчивость к радиации, сохранение

информации при выключении питания;

недостатки — малая ёмкость, большой

вес, стирание информации при каждом

чтении. В настоящее время в таком,

собранном из дискретных компонентов

виде, не применяется. Однако к 2003 году

появилась магнитная память MRAM в

интегральном исполнении. Сочетая

скорость SRAM и возможность хранения

информации при отключённом питании,

MRAM является перспективной заменой

используемым ныне типам ROM и RAM. Однако

она на сегодняшний день (2006 год)

приблизительно вдвое дороже микросхем

SRAM (при той же ёмкости и габаритах).

На

сегодня наибольшее распространение

имеют два вида ОЗУ:

SRAM

(Static RAM)

ОЗУ,

собранное на триггерах, называется

статической памятью с произвольным

доступом, или просто статической памятью.

Достоинство этого вида памяти — скорость.

Поскольку триггеры собраны на вентилях,

а время задержки вентиля очень мало, то

и переключение состояния триггера

происходит очень быстро. Данный вид

памяти не лишён недостатков. Во-первых,

группа транзисторов, входящих в состав

триггера, обходится дороже, даже если

они вытравляются миллионами на одной

кремниевой подложке. Кроме того, группа

транзисторов занимает гораздо больше

места, поскольку между транзисторами,

которые образуют триггер, должны быть

вытравлены линии связи.

D

RAM

(Dynamic RAM)

Более

экономичной вид памяти. Для хранения

разряда (бита) используется схема,

состоящая из одного конденсатора и

одного транзистора (в некоторых вариациях

конденсаторов два). Такой вид памяти

решает, во-первых, проблему дороговизны

(один конденсатор и один транзистор

дешевле нескольких транзисторов) и,

во-вторых, компактности (там, где в SRAM

размещается один триггер, то есть один

бит, можно уместить восемь конденсаторов

и транзисторов). Есть и свои минусы.

Во-первых, память на основе конденсаторов

работает медленнее, поскольку если в

SRAM изменение напряжения на входе триггера

сразу же приводит к изменению его

состояния, то для того, чтобы установить

в 1 бит на основе конденсатора, этот

конденсатор нужно зарядить, а для того,

чтобы бит установить в 0, соответственно,

разрядить. А это гораздо более длительные

(в 10 и более раз) операции, чем переключение

триггера, даже если конденсатор имеет

весьма небольшие размеры. Второй

существенный минус — конденсаторы

склонны к «стеканию» заряда; проще

говоря, со временем конденсаторы

разряжаются. Причём разряжаются они

тем быстрее, чем меньше их ёмкость. В

связи с этим обстоятельством, дабы не

потерять содержимое битов, конденсаторы

необходимо регенерировать через

определённый интервал времени, чтобы

восстанавливать заряд. Регенерация

выполняется путем считывания заряда

(через транзистор). Контроллер памяти

периодически приостанавливает все

операции с памятью для регенерации её

содержимого, что значительно снижает

производительность данного вида ОЗУ.

Память на конденсаторах получила своё

название Dynamic RAM (динамическая память)

как раз за то, что разряды в ней хранятся

не статически, а «стекают» динамически

во времени.

Таким образом, DRAM

дешевле SRAM и её плотность выше, что

позволяет на том же пространстве

кремниевой подложки размещать больше

битов, но при этом её быстродействие

ниже. SRAM, наоборот, более быстрая память,

но зато и дороже. В связи с этим обычную

память строят на модулях DRAM, а SRAM

используется для построения, например,

кеш-памяти в микропроцессорах.

Статическая

оперативная память с произвольным

доступом

(SRAM

— Static

Random Access Memory)

— полупроводниковая оперативная память,

в которой каждый двоичный или троичный

разряд хранится в схеме с положительной

обратной связью, позволяющей поддерживать

состояние сигнала без постоянной

перезаписи, необходимой в динамической

памяти (DRAM). Произвольный доступ (RAM —

random access memory) — возможность выбирать для

записи/чтения любой из битов (тритов)

(чаще байтов (трайтов), зависит от

особенностей конструкции), в отличие

от памяти с последовательным доступом

(SAM — sequental access memory).

Типичная ячейка

статической двоичной памяти (двоичный

триггер) на КМОП-технологии состоит из

двух перекрёстно (кольцом) включенных

инверторов и ключевых транзисторов для

обеспечения доступа к ячейке (рис.1.).

Часто для увеличения плотности упаковки

элементов на кристалле в качестве

нагрузки применяют поликремниевые

резисторы. Недостатком такого решения

является рост статического

энергопотребления.

Линия WL (Word

Line) управляет двумя транзисторами

доступа. Линии BL и BL - битовые линии,

используются и для записи данных и для

чтения данных.

Преимущества:

·

Быстрый доступ. SRAM — это действительно

память произвольного доступа, доступ

к любой ячейке памяти в любой момент

занимает одно и то же время.

·

Простая схемотехника — SRAM не требуются

сложные контроллеры.

·

Возможны очень низкие частоты

синхронизации, вплоть до полной остановки

синхроимпульсов.

Недостатки

·

Высокое энергопотребление.

·

Невысокая плотность записи (шесть

элементов на бит, вместо двух у DRAM).

· Вследствие

чего — дороговизна килобайта памяти.

Тем

не менее, высокое энергопотребление не

является принципиальной особенностью

SRAM, оно обусловлено высокими скоростями

обмена с данным видом внутренней памяти

процессора. Энергия потребляется только

в момент изменения информации в ячейке

SRAM.

Применение:

SRAM применяется

в микроконтроллерах и ПЛИС, в которых

объём ОЗУ невелик (единицы килобайт),

зато нужны низкое энергопотребление

(за счёт отсутствия сложного контроллера

динамической памяти), предсказываемое

с точностью до такта время работы

подпрограмм и отладка прямо на

устройстве.

В устройствах с большим

объёмом ОЗУ рабочая память выполняется

как DRAM. SRAM’ом же делают регистры и

кэш-память.

DRAM

(Dynamic

Random Access Memory)

— один из видов компьютерной памяти с

произвольным доступом (RAM), наиболее

широко используемый в качестве ОЗУ

современных компьютеров.

Конструктивно

память DRAM состоит из «ячеек» размером

в 1 или 4 бит, в каждой из которых можно

хранить определённый объём данных.

Совокупность «ячеек» такой памяти

образуют условный «прямоугольник»,

состоящий из определённого количества

строк и столбцов. Один такой «прямоугольник»

называется страницей, а совокупность

страниц называется банком. Весь набор

«ячеек» условно делится на несколько

областей.

Принцип

действия

Физическое

представление:

В

современных компьютерах физически

DRAM-память представляет собой электрическую

плату — модуль, на котором расположены

микросхемы памяти и разъём, необходимый

для подключения модуля к материнской

плате. Роль «ячеек» играют конденсаторы

и транзисторы, расположенные внутри

микросхем памяти. Конденсаторы заряжаются

в случае, когда в «ячейку» заносится

единичный бит, либо разряжаются в случае,

когда в «ячейку» заносится нулевой бит.

Транзисторы необходимы для удержания

заряда внутри конденсатора. При отсутствии

подачи электроэнергии к оперативной

памяти, происходит разряд конденсаторов,

и память опустошается. Это динамическое

изменение заряда конденсатора является

основополагающим принципом работы

памяти типа DRAM. Элементом памяти этого

типа является чувствительный усилитель

(англ. sense amp), подключенный к каждому из

столбцов «прямоугольника». Он, реагируя

на слабый поток электронов, устремившихся

через открытые транзисторы с обкладок

конденсаторов, считывает всю страницу

целиком. Именно страница является

минимальной порцией обмена с динамической

памятью, потому что обмен данными с

отдельно взятой ячейкой

невозможен.

Характеристики

памяти DRAM:

Основными

характеристиками DRAM являются тайминги

и рабочая частота. Для обращения к ячейке

контроллер задаёт номер банка, номер

страницы в нём, номер строки и номер

столбца, на все запросы тратится время,

помимо этого довольно большой период

уходит на открытие и закрытие банка

после самой операции. На каждое действие

требуется время, называемое таймингом.

Основными таймингами DRAM являются:

задержка между подачей номера строки

и номера столбца, называемая временем

полного доступа (англ. RAS to CAS delay), задержка

между подачей номера столбца и получением

содержимого ячейки, называемая временем

рабочего цикла (англ. CAS delay), задержка

между чтением последней ячейки и подачей

номера новой строки (англ. RAS precharge).

Тайминги измеряются в наносекундах, и

чем меньше величина этих таймингов, тем

быстрее работает оперативная память.

Рабочая частота измеряется в мегагерцах,

и увеличение рабочей частоты памяти

приводит к увеличению её

быстродействия

Регенерация

В

отличие от статической памяти типа SRAM

(англ. static random access memory), которая является

конструктивно более сложным и более

дорогим типом памяти RAM и используется

в основном в кэш—памяти, память DRAM

изготавливается на основе конденсаторов

небольшой ёмкости, которые быстро теряют

заряд, поэтому информацию приходится

обновлять через определённые периоды

времени во избежание потерь данных.

Этот процесс называется регенерацией

памяти. Он реализуется специальным

контроллером, установленным на материнской

плате или на кристалле центрального

процессора. На протяжении времени,

называемого шагом регенерации, в DRAM

перезаписывается целая строка «ячеек»,

и через 8-64 мс обновляются все строки

памяти.

Процесс регенерации памяти

в классическом варианте существенно

«тормозит» работу системы, поскольку

в это время обмен данными с памятью

невозможен. Регенерация, основанная на

обычном переборе строк, не применяется

в современных типах DRAM. Существует

несколько более экономичных вариантов

этого процесса — расширенный, пакетный,

распределенный; наиболее экономичной

является скрытая регенерация.

Из

новых технологий регенерации можно

выделить тип регенерации PASR (англ.

Partial Array Self Refresh), применяемый компанией

Samsung в чипах памяти SDRAM с низким уровнем

энергопотребления. Регенерация «ячеек»

выполняется только в период ожидания

в тех банках памяти, в которых имеются

данные. Параллельно с этой технологией

реализуется метод TCSR (англ. Temperature

Compensated Self Refresh), который предназначен

для регулировки скорости процесса

регенерации в зависимости от рабочей

температуры.

Типы

DRAM

На

протяжении долгого времени разработчиками

создавались различные типы памяти. Они

обладали разными характеристиками, в

них были использованы разные технические

решения. Основной движущей силой развития

памяти было развитие ЭВМ и центральных

процессоров. Постоянно требовалось

увеличение быстродействия и объёма

оперативной памяти.

Страничная

память

Страничная

память (англ. page mode DRAM, PM DRAM) являлась

одним из первых типов выпускаемой

компьютерной оперативной памяти. Память

такого типа выпускалась в начале 90-х

годов, но с ростом производительности

центральных процессоров и ресурсоёмкости

приложений требовалось увеличивать не

только объём памяти, но и скорость её

работы.

Быстрая

страничная память

Быстрая

страничная память (англ. fast page mode DRAM, FPM

DRAM) появилась в 1995 году. Принципиально

новых изменений память не претерпела,

а увеличение скорости работы достигалось

путём повышенной нагрузки на аппаратную

часть памяти. Данный тип памяти в основном

применялся для компьютеров с процессорами

Intel 80486 или аналогичных процессоров

других фирм. Память могла работать на

частотах 25 МГц и 33 МГц с временем полного

доступа 70 нс и 60 нс и с временем рабочего

цикла 40 нс и 35 нс соответственно.

Память

с усовершенствованным выходом

C

появлением процессоров Intel Pentium память

FPM DRAM оказалась совершенно неэффективной.

Поэтому следующим шагом стала память

с усовершенствованным выходом (англ.

extended data out DRAM, EDO DRAM). Эта память появилась

на рынке в 1996 году и стала активно

использоваться на компьютерах с

процессорами Intel Pentium и выше. Её

производительность оказалась на 10—15

% выше по сравнению с памятью типа FPM

DRAM. Её рабочая частота была 40 МГц и 50

МГц, соответственно, время полного

доступа — 60 нс и 50 нс, а время рабочего

цикла — 25 нс и 20 нс. Эта память содержит

регистр-защелку (англ. data latch) выходных

данных, что обеспечивает некоторую

конвейеризацию работы для повышения

производительности при чтении.

Синхронная

DRAM

В

связи с выпуском новых процессоров и

постепенным увеличением частоты

системной шины, стабильность работы

памяти типа EDO DRAM стала заметно падать.

Ей на смену пришла синхронная память

(англ. synchronous DRAM, SDRAM). Новыми особенностями

этого типа памяти являлись использование

тактового генератора для синхронизации

всех сигналов и использование конвейерной

обработки информации. Также память

надёжно работала на более высоких

частотах системной шины (100 МГц и выше).

Недостатками данного типа памяти

являлась его высокая цена, а также его

несовместимость со многими чипсетами

и материнскими платами в силу своих

новых конструктивных особенностей.

Рабочие частоты этого типа памяти могли

равняться 66 МГц, 100 МГц или 133 МГц, время

полного доступа — 40 нс и 30 нс, а время

рабочего цикла — 10 нс и 7,5 нс.

Пакетная

EDO RAM

Пакетная

память EDO RAM (англ. burst extended data output DRAM, BEDO

DRAM) стала дешёвой альтернативой памяти

типа SDRAM. Основанная на памяти EDO DRAM, её

ключевой особенностью являлась технология

поблочного чтения данных (блок данных

читался за один такт), что сделало её

работу быстрее, чем у памяти типа SDRAM.

Однако невозможность работать на частоте

системной шины более 66 МГц не позволила

данному типу памяти стать популярным.

Video

RAM

Cпециальный

тип оперативной памяти Video RAM (VRAM) был

разработан на основе памяти типа SDRAM

для использования в видеоплатах. Он

позволял обеспечить непрерывный поток

данных в процессе обновления изображения,

что было необходимо для реализации

изображений высокого качества. На основе

памяти типа VRAM, появилась спецификация

памяти типа Windows RAM (WRAM), иногда её ошибочно

связывают с операционными системами

семейства Windows. Её производительность

стала на 25 % выше, чем у оригинальной

памяти типа SDRAM, благодаря некоторым

техническим изменениям.

DDR

SDRAM

По

сравнению с обычной памятью типа SDRAM, в

памяти SDRAM с удвоенной скоростью передачи

данных (англ. double data rate SDRAM, DDR SDRAM или

SDRAM II) была вдвое увеличена пропускная

способность. Первоначально память

такого типа применялась в видеоплатах,

но позднее появилась поддержка DDR SDRAM

со стороны чипсетов. Она работает на

частотах в 100 МГц и 133 МГц, её время полного

доступа — 30 нс и 22,5 нс, а время рабочего

цикла — 5 нс и 3,75 нс.

Direct

RDRAM, или Direct Rambus DRAM

Тип

памяти RDRAM является разработкой компании

Rambus. Высокое быстродействие этой памяти

достигается рядом особенностей, не

встречающихся в других типах памяти.

Первоначальная очень высокая стоимость

памяти RDRAM привела к тому, что производители

мощных компьютеров предпочли менее

производительную, зато более дешёвую

память DDR SDRAM. Рабочие частоты памяти —

400 МГц, 600 МГц и 800 МГц, время полного

доступа — до 30 нс, время рабочего цикла

— до 2,5 нс.

DDR2

SDRAM

Конструктивно

новый тип оперативной памяти DDR2 SDRAM был

выпущен в 2004 году. Основываясь на

технологии DDR SDRAM, этот тип памяти за

счёт технических изменений показывает

более высокое быстродействие и

предназначен для использования на

современных компьютерах. Память может

работать на частотах в 200 МГц, 266 МГц, 333

МГц и 400 МГц. Время полного доступа — 25

нс, 11,25 нс, 9 нс, 7,5 нс. Время рабочего цикла

— 5 нс, 3,75 нс, 3 нс, 3,5 нс.

Корпуса

Различные

корпуса DRAM. Сверху вниз: DIP, SIP, SIMM

(30-контактный), SIMM (72-контактный), DIMM

(168-контактный), DIMM (184-контактный,

DDR)Элементы памяти типа DRAM конструктивно

выполняют либо в виде отдельных микросхем

в корпусах типа DIP, либо в виде модулей

памяти типа: SIP (Single In-Line Package), SIMM (Single

In-line Memory Module), DIMM (Dual In-line Memory Module), RIMM

(Rambus In-line Memory Module). Микросхемы в корпусах

типа DIP выпускались до использования

модулей памяти. Эти микросхемы имеют

два ряда контактов, расположенных вдоль

длинных сторон чипа и загнутых вниз.

Модули

SIP

Модули

типа SIP представляют собой прямоугольные

платы с контактами в виде маленьких

штырьков. Этот тип памяти в настоящее

время практически не используется, так

как был вытеснен модулями памяти типа

SIMM.

Модули

SIMM

Модули

типа SIMM представляют собой прямоугольную

плату с контактной полосой вдоль одной

из сторон, модули фиксируются в разъёме

поворотом с помощью защёлок. Наиболее

распространены 30- и 72-контактные SIMM.

Широкое распространение нашли SIMM на 4,

8, 16, 32 и даже 64 Мбайт.

Модули

DIMM

Модули

типа DIMM наиболее распространены в виде

168-контактных модулей, устанавливаемых

в разъём вертикально и фиксируемых

защёлками. В портативных устройствах

широко применяются SO DIMM — разновидность

DIMM малого размера (англ. SO — small outline),

они предназначены в первую очередь для

портативных компьютеров. Наиболее часто

встречаются 72- и 144-контактные модули

типа SO DIMM. Память типа DDR SDRAM выпускается

в виде 184-контактных DIMM-модулей, а для

памяти типа DDR2 SDRAM выпускаются

240-контактные модули.

Модули

RIMM

Модули

типа RIMM менее распространены, в таких

модулях выпускается память типа Direct

RDRAM. Они представлены 168/184-контактными

прямоугольными платами, которые

обязательно должны устанавливаться

только в парах, а пустые разъёмы на

материнской плате занимаются специальными

заглушками. Это связано с особенностями

конструкции таких модулей. Так же

существуют модули 232-pin PC1066 RDRAM RIMM 4200, не

совместимые с 184-контактными разъёмами.

Стековая память

Рассмотрим организацию стековой памяти, как памяти, образованной из связанных между собой ячеек памяти, в которых информация при записи в стек нового слова смещается вниз (Рис.2). Обмен информацией осуществляется только через верхнюю ячейку памяти. При считывании слов из стека, слово может удаляться из стековой памяти или сдвигаться по кольцу, в зависимости от организации стека. Режим чтения –последним вошел, первым вышел- называют LIFO (Last In First Out).

Рис.2.Организация

стековой памяти.

Рис.2.Организация

стековой памяти.

Аппаратная реализация такой памяти не всегда целесообразна и зачастую стековая память организуется в основной памяти компьютера программно, что позволяет изменять объем стека в зависимости от необходимости. При организации стека в основной памяти выделяется специальный адресный регистр – “указатель стека.”. В указателе стека находится адрес последнего записанного в стек слова. При записи слова в стек адрес вершины стека автоматически уменьшается, при чтении - автоматически увеличивается. Стековая память используется обычно для сохранения состояния текущей программы при обработке прерывания. После выполнения прерывающей программы состояние всех регистров, существовавшие в момент прерывания программы восстанавливается в последовательности, обратной последовательности записи. Можно сохранять в стеке и данные программы, это удобно тем, что при обращении к стеку не требуется указывать в программе адреса ячейки памяти, извлечение информации из стека так же происходит без указания адреса.

Регистровая память

В цифровой аппаратуре широко используются небольшие вспомогательные запоминающие устройства с неявно выраженной адресацией, служащие для хранения очередей и называемые иногда буферами данных. Часто их строят на основе регистровой памяти.

Часто используемым в цифровой технике буфером является буфер типа «магазин», или стек, или LIFO. В отличии от нормальной очереди здесь в качестве первого кандидата на обслуживание выбирается то слово, которое встало в очередь последним. По такому закону заряжается патронами и освобождается в процессе работы магазин автоматического оружия, откуда и произошло одно из названий. Стековые структуры данных возникают в цифровых устройствах, когда процесс выполнения менее срочного задания прерывается более срочным и все данные, связанные с прерванной работой, засылаются на временное хранение в буфер типа «магазин». Выполнение срочного задания может быть в свою очередь прервано поступлением сверхсрочного и т.д.- и в стеке по мере погружения туда (сверху) новых и новых данных формируется очередь слов, стековый порядок извлечения которых (тоже сверху) соответствует правильной по рангу срочности очередности их обработки.

3. Общий принцип работы памяти типа "очередь"

Рис. 1. Буфер типа "Магазин"

Счетчик должен быть реверсивным, т.е. уметь прибавлять 1, когда поступает команда «Заслать в стек» и вычитать 1 при команде «Извлечь из стека». При этом адрес, по которому производится засылка в стек, всегда на единицу больше адреса, по которому выполняется чтение из стека. Постоянный сдвиг на единицу адреса записи относительно адреса чтения выполняет инкрементор. Стек имеет два особых состояния: «буфер пуст» и «буфер полон». Обнаруживаются они непосредственно по нулевому и по максимальному возможному (все единицы) состоянием счетчика адреса. 4. Общая структурная схема

Структурная схема устройства регистровой памяти типа "магазин" представлена на рис. 2

Рис. 2. Структурная схема

Регистровая память типа "магазин" состоит из двух блоков. Блок управления предназначен для вычислений адресов записи и считывания, проверки буфера на переполнение, обнуления памяти и синхронизации с потоком данных. Входными сигналами для блока управления являются сигнал обнуления памяти, сигнал разрешения записи в память, сигнал разрешения чтения из памяти.

Блок управления в свою очередь состоит из блока формирования адреса, блока дешифрации адреса и блока проверки заполнения памяти.

Блок регистров представляет собой обыкновенный регистровый файл.

Принцип работы устройства заключается в следующем. Сигнал записи в память поступает в блок управления, по его приходу в блоке формирования адреса формируется адрес записи путем прибавления единицы к текущему адресу. Сформированный адрес поступает на вход блока дешифрации адреса. Далее по линии определяемой поступившим адресом посылается сигнал соответствующему регистру в блоке регистров о том, что на шине записи находятся данные, которые нужно записать. Данные записываются в регистр. Если при этом адрес записи становится равным максимальному адресу памяти, то выдается сигнал о том, что буфер полон.

Чтение из памяти осуществляется аналогичным методом. Сигнал чтения из памяти поступает в блок управления, по его приходу в блоке формирования адреса формируется адрес чтения. Сформированный адрес поступает на вход блока дешифрации адреса. Далее по линии определяемой поступившим адресом посылается сигнал соответствующему регистру в блоке регистров о том, что регистру пора выдать данные на шину чтения. Данные считываются из регистра. Если при этом адрес записи становится равным нулю, то выдается сигнал о том, что буфер пуст.

5. Функциональная схема блока управления

На рис. 3 представлена функциональная схема блока управления памятью

Рис. 3. Схема блока управления

Формирование адреса чтения показано пунктиром (то с использованием инкрементора).

Рассмотрим принадлежность элементов схемы структурным блокам

Адресная память

Адресная

память

При

адресной организации памяти размещение

и поиск информации в запоминающем

массиве основаны на использовании

адреса хранения слова. Адресом служит

номер ячейки массива, в которой это

слово размещается. При записи (или

считывании) слова в запоминающий массив,

инициирующая эту операцию команда

должна указывать адрес, по которому

производится запись считывание).

Типичная структура адресной

памяти содержит запоминающий массив

из n-разрядных ячеек (обычно n равно 1, 4,

8 или 16) и его аппаратурное обрамление,

включающее регистр адреса РгА, имеющий

k разрядов (k больше или равно логарифму

по основанию 2 от N), информационный

регистр РгИ, блок адресной выборки БАВ,

блок усилителей считывания БУС, блок

разрядных усилителей-формирователей

сигналов записи БУЗ и блок управления

памятью БУП.

По коду адреса в

регистре адреса блок адресной выборки

формирует в соответствующей ячейке

памяти сигналы, позволяющие произвести

считывание или запись слова в ячейку.

Проиллюстрируем адресную структуру

памяти на примере ЭВМ с 16-разрядной

шиной данных и 16-разрядными словами.

Понятно, что при обмене данными с памятью

по шине данных пересылаются двухбайтовые

слова.

15 8 7 0 15 8 7 0

1![]()

![]() 0 0 1

3

0 0 1

3![]() 2 2 3

5

4 4 5

2 2 3

5

4 4 5

![]()

![]() 65533

6

65533

6

![]() 5535

65534 65534 65535

«слева» «справа»

^

5535

65534 65534 65535

«слева» «справа»

^

Рис. 4.1 Адресная память

Такая структура организации памяти позволяет разрешить ряд проблем по хранению символов, закодированных в последовательных байтах (облегчается работа с текстами).

6. ПЗУ

Кроме оперативной памяти, под термином "память" мы будем подразумевать постоянную и CMOS - память.

К постоянной памяти относят постоянное запоминающее устройство, ПЗУ (в англоязычной литературе - Read Only Memory, ROM, что дословно перводится как "память только для чтения"), перепрограммируемое ПЗУ, ППЗУ (в англоязычной литературе – Programmable Read Only Memory, PROM), и флэш-память (flash memory). Название ПЗУ говорит само за себя. Информация в ПЗУ записывается на заводе-изготовителе микросхем памяти, и в дальнейшем изменить ее значение нельзя. В ПЗУ хранится критически важная для компьютера информация, которая не зависит от выбора операционной системы. Программируемое ПЗУ отличается от обычного тем, что информация на этой микросхеме может стираться специальными методами (например, лучами ультрафиолета), после чего пользователь может повторно записать на нее информацию. Эту информацию будетневозможно удалить до следующей операции стирания информации.

C.2. Флэш-память.

Особо следует рассказать о флэш-памяти. Flash по-английски – это "вспышка, проблеск". Флэш-память является энергонезависимой памятью, (как и ПЗУ и ППЗУ). При выключении компьютера ее содержимое сохраняется. Однако содержимое flash-памяти можнр многократно перезаписывать, не вынимая ее из компьютера (в отличие от ППЗУ). Запись происходит медленнее, чем считывание, и осуществляется импульсами повышенного напряжения. Вследcтвие этого, а также из-за ее стоимости, флэш память не заменит микросхемы ОЗУ.

C.3. CMOS-память.

CMOS-память – энергозависимая, перезаписываемая память, которая при своей работе , однако, почти не потребляет энергии. CMOS переводится как complementary metal oxode semiconductor – "комплиментарный металл - оксид - полупроводниковый". Достоинства этой памяти – низкое потребление энергии, высокое быстродействие. В CMOS - памяти компьютера находятся важные для его работы настройки, которые пользователь может менять для оптимизации работы компьютера. Питается эта память от небольшого аккумулятора, встроенного в материнскую плату.

C.4. Недостатки перезаписываемой памяти.

Основной недостаток ПЗУ – невозможность обновить информацию в этом виде памяти, – одновременно является и его преимуществом: данные невозможно потерять случайно и умышленно. Особенно это стало актуальным на рубехе XX – XXI веков, с вытеснением микросхем ПЗУ на CMOS и flash-память. Рассмотрим возникающие проблемы.

C.4.1. Потеря данных в CMOS.

Компьютеры с ISA шиной (содержащие процессоры вплоть до i80286), имели минимум настроек. Часто они вполне нормально работали в своей основной конфигурации.

Ситуация изменилась после появления на компьютерах памяти более чем 16 Мбайт, ШВУ контроллеров и PCI-шины. Как выяснилось, в большинстве случаев стандартная настройка материнской платы стала неприменимой. Для сохранения настроек пользователя их стали хранить в CMOS-памяти.

Иногда содержимое CMOS-памяти разрушается. Это возможно в следующих случаях:

Воздействие вируса. При своей работе вирус может специально внедряться в CMOS-память, чтобы обеспечиватиь лучшие условия для его распространения либо специально вывести компьютер из строя.

Неисправность аккумулятора. В некоторых случаях аккумулятор CMOS-памяти может разряжаться (от времени или короткого замыкания на плате.) В этом случаесодержимое CMOS может разрушиться не сразу, а по прошествии двух - трех суток.

Скачок напряжения при работе с CMOS. В этом случае последствия непредсказуемы.

Установка пароля на загрузку. Иногда пользователь для защиты от несанкционированного доступа устанавливает "пароль на загрузку". Если он потом забудет пароль, то для запуска компьютера будет необходим сброс параметров CMOS-памяти путем короткого замыкания ее аккумулятора.

Для восстановления параметров CMOS-памяти после ее сброса существуют опции "стандартной" и безопасной" настройки этой памяти на материнской плате. Пользователю в этом случае придется восстанавливать не все, а только часть параметров. Опции "стандартной" и "безопасной" настройки хранятся в ПЗУ и изменить их невозможно!

C.4.2. Потеря данных в flash-памяти.

Потеря данных в flash-памяти возможна по тем же причинам, что и в CMOS-памяти. Однако для флэш-памяти нет возможности вернуться к первоначальным установкам! В связи с этим потеря информации в флэш-памяти может быть непоправимой.

... В 1998 году автор узнал о новом черезвычайно опасном вирусе –"Чернобыль". Опасность заключалась в его действии – ровно в годовщину аварии на Чернобыльской АЭС этот вирус портил содержимое флэш-памяти и наиболее важной ее части – BIOS. В результате компьютер не мог вообще осуществлять операции ввода-вывода, в том числе и загрузку операционных систем. CMOS-память же оставалась в полном порядке! Поскольку микросхема с BIOS обычно была припаяна к материнской плате, приходилось выкидывать всю материнскую плату.

Автору известен только один способ 100% гарантии избежать действия этого вируса – аппаратно запретить перзапись флэш-памяти. Дело в том, что новые версии этого вируса размножаются лавинообразно, и нет гарантии, что он сработает именно в эту дату.