- •Билет №3. Укорачивающие и расширяющие rc-цепи. Влияние неучтенных параметров.

- •А) входные характеристики б) выходные характеристики

- •Билет № 5. Временные процессы в транзисторном ключе оэ.

- •Ключ оэ с введением нелинейной обратной связи.

- •Билет № 8.Простейший элемент ттл. Основной элемент ттл.

- •Билет № 9.Электрические характеристики микросхем ттл: амплитудно-передаточная характеристика, характеристика уровня технологии.

- •Билет № 10.Специальная организация выходов ттл.

- •Билет № 12.Разновидности триггерных схем. Микросхемы jk- и d-триггеров ттл.

- •Билет № 13.Простейшие релаксаторы ттл. Канонические схемы.

- •Билет № 16.Микросхемы с триггерной памятью. Регистры и счетчики.

- •Несогласование межблочной связи.

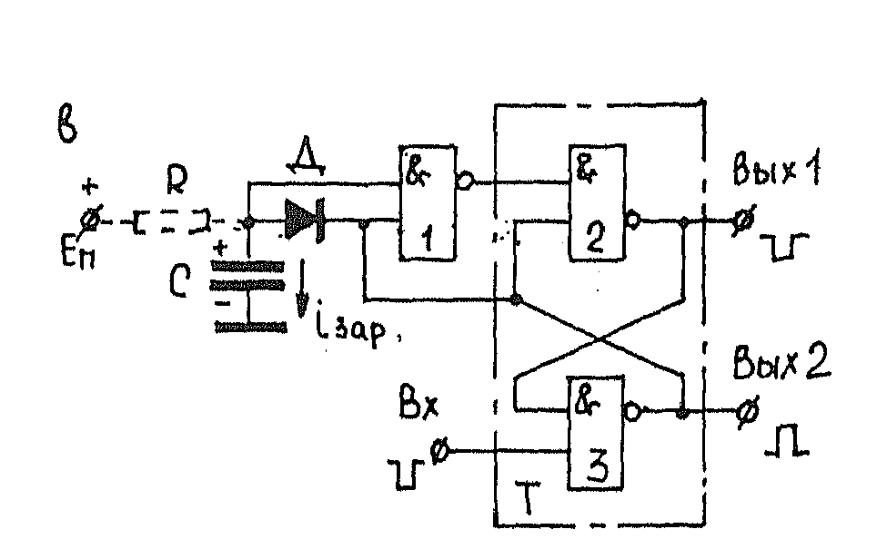

Билет № 13.Простейшие релаксаторы ттл. Канонические схемы.

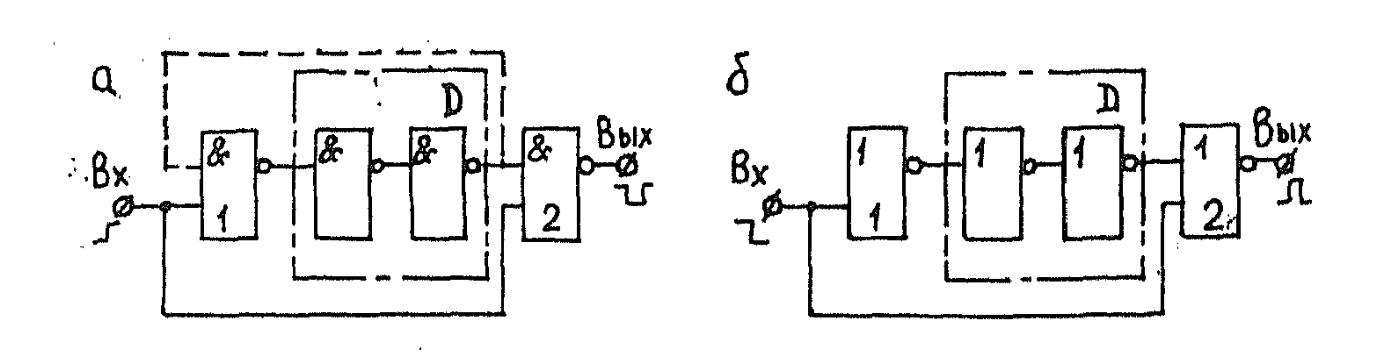

Применение линейных ИС в комбинации с «навесными» компонентами позволяет реализовать обычные схемы мультивибраторов и блогинггенераторов. В цифровой аппаратуре предпочтение отдают логическим ИС. Генераторы импульсов на их основе обладают определенной спецификой. Среди ИС-генераторов принято различать формирователи «коротких» импульсов по фронту и срезу входного сигнала и релаксаторы в ждущем и автоколебательном режимах. Канонические схемы формирователей содержат инвертор – элемент 1 и выходной элемент И-НЕ, (ИЛИ-НЕ) – элемент 2. Последовательно инвертором включают элемент задержки D. Это цепочка из четного числа инверторов, соединенных каскадно.

Каноническая схема формирователей а) по фронту, б) по срезу.

Замыканием кольца (пунктир) получаем схему автогенератора, скважность импульсов которого N=2.

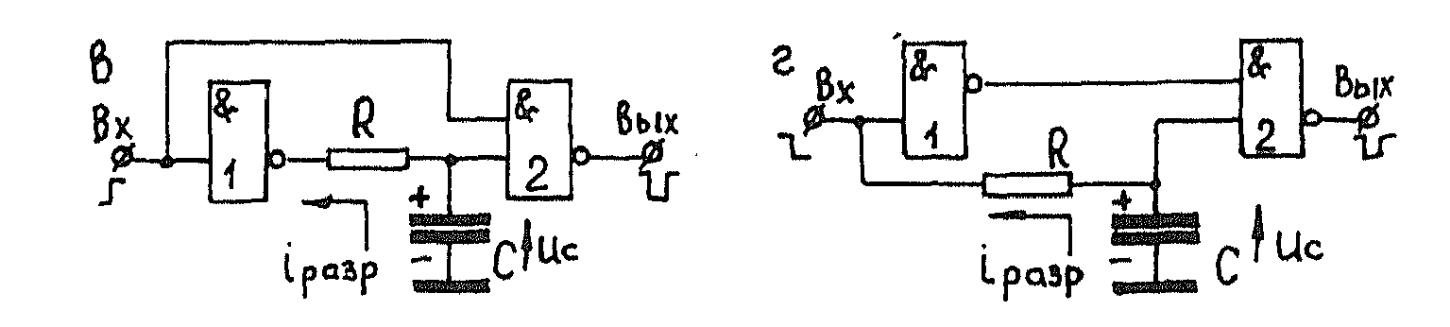

Функцию элемента D может выполнять RС-цепь. В исходном состоянии элемент 2 закрыт, емкость С заряжена, UС(0)=UВЫХ. При наличии входного перепада элемент 2 открывается, начинается разряд емкости. Формирование импульса на выходе завершается, как только UС=UВХ.П.

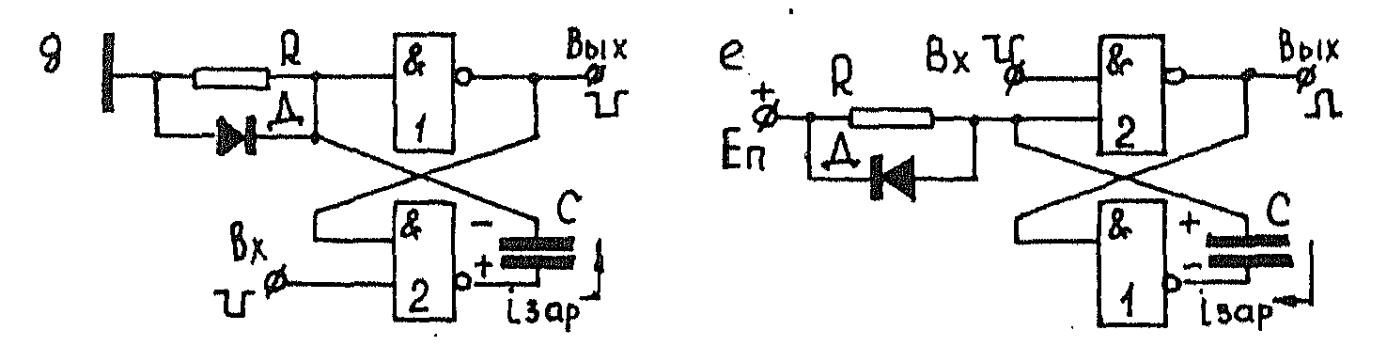

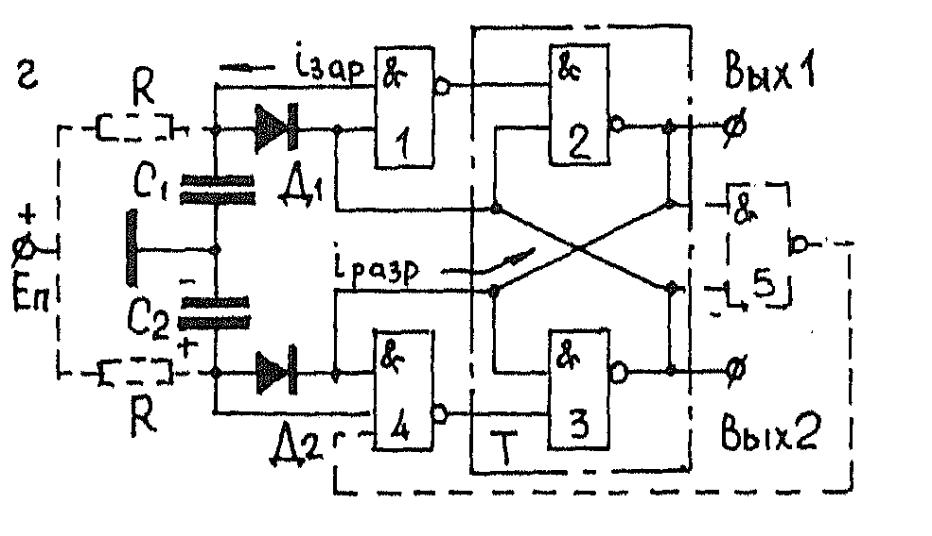

В схемах ждущего релаксатора(рис. е, д) первоначально элемент 1 закрыт, элемент 2 открыт, емкость С практически разряжена. Отрицательный входной импульс переводит схему во временноустойчивое положение, длительность которого определяется процессом заряда емкости. Восстановление исходного состояния связано с быстрым разрядом емкости через открытый диод Д.

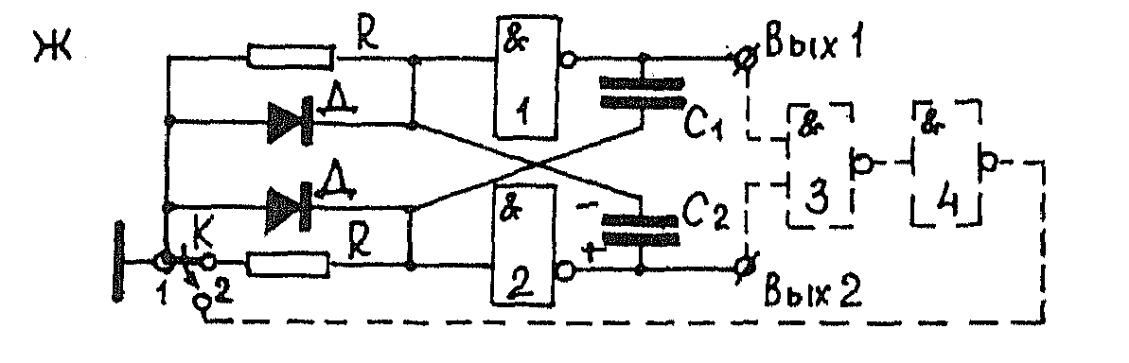

Также построена схема автогенератора. Пусть в исходном состоянии элемент 1 закрыт, элемент 2 открыт, емкость С1 разряжена, С2 заряжена. Быстрый разряд емкости С2 происходит через открытый диод Д. По мере заряда емкости С1 уменьшается потенциал входа элемента 2. При UВХ2 = UВХ.П. в схеме возникает регенерация.

Пусть С1С2, тогда большая емкость С1 должна успеть разрядиться за время заряда меньшей. Для исключения состояния, когда оба элемента закрыты и обе емкости заряжены, вводят элементы 3 и 4. Их наличие гарантирует в указанной ситуации принудительное открывание элемента 2 на время разряда емкости С2 и дальнейшее нормальное протекание процессов в схеме.

Билет № 14.

ИС-генераторы с бистабильной ячейкой. Микросхемы генераторов импульсов ТТЛ.

В процессе заряда времязадающей емкости в схеме автогенератора происходит нарастание вершины импульса на входе, к которому емкость подключена. Использование бистабильной ячейки позволяет получить на обоих выходах релаксатора прямоугольные импульсы. Их длительность определяется моментами поступления соответствующих потенциалов на установочные входы триггера. В ждущем релаксаторе один из сигналов подается непосредственно со входа устройства, другой формируется специальным пороговым элементом внутри самой схемы по окончании в ней релаксационного процесса.

Бистабильные ячейки применяются и в простейших безъемкостных формированиях. Их роль сводится к уменьшению числа используемых элементов при той же величине tИ2 = 3tЗ.СР.

В схеме ждущего релаксатора при отсутствие входного отрицательного импульса элемент 3 открыт, элемент 1 и 2 закрыты, емкость с разряжена. С поступлением входного сигнала элемент 3 и диод Д закрываются, элемент 2 открыт.Идет заряд емкости С через переход эмиттер – база МЭТ элемента 1. Как только UC(t) = UВХ.П., происходит новое переключение схемы, если входной импульс завершен к этому моменту. В ином случае вплоть до окончания входного сигнала на обоих выходах имеем высокие потенциальные уровни.

Автоколебательный режим реализуется переходом к симметричной схеме. Пусть в исходном состоянии элементы 2 и 4 открыты, элементы 3 и 1 закрыты, емкость С1 заряжена, емкость С2 разряжена. Открытое состояние элемента 4 скоротечно, оно завершается быстрым разрядом емкости С2 через малое выходное сопротивление открытого элемента 2. При UС1 = UВХ.П начинается переключение схемы в новое временноустойчивое состояние. Возможно устойчивое положение, когда обе емкости заряжены, а элементы 2 и 3 закрыты. Для его исключения в схему дополняют элемент 5.

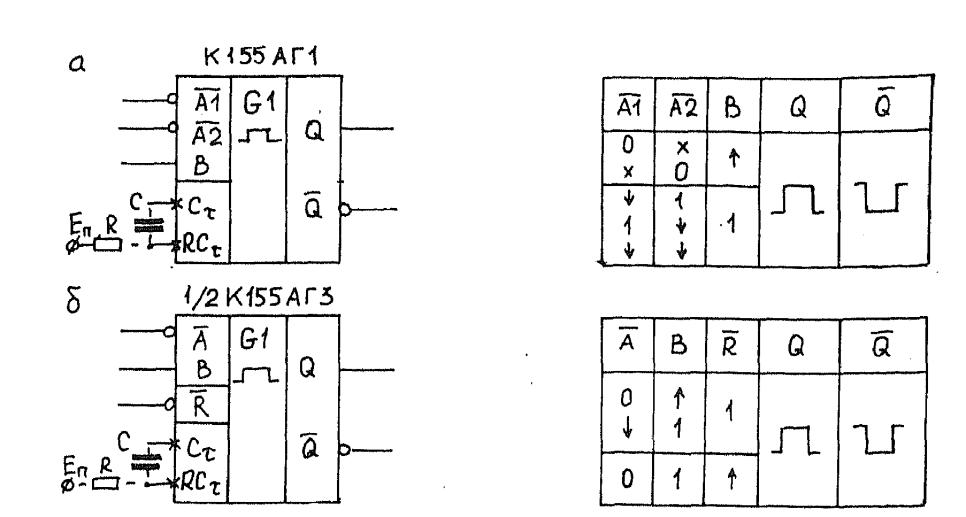

Применение специальных микросхем ждущих генераторов позволяет устранить ограничения, свойственные простейшим релаксаторам: по выбору внешнего резистора R, по длительности входного импульса, по логическим возможностям. В серии К155 есть две такие микросхемы: АГ1 и АГ3 с одним и двумя генераторами в курпусе.

Стрелка, направленная вверх, означает положительный перепад, вниз – отрицательный. Динамическое управление обуславливает отсутствие влияния длительности входных сигналов на функционирование генераторов. Для пассивных схем Q=0, неQ=1.

Входы С и RC являются нелогическими. К ним подключаются времязадающие компоненты С и R. Логические возможности АГ3 выше, чем у АГ1, т.к. формирование импульса на выходе может быть прекращено подачей отрицательно импульса сброса на вход неR; длительность генерируемого импульса можно увеличить повторной подачей импульса запуска; схема автогенератора реализуется на одном корпусе АГ3.

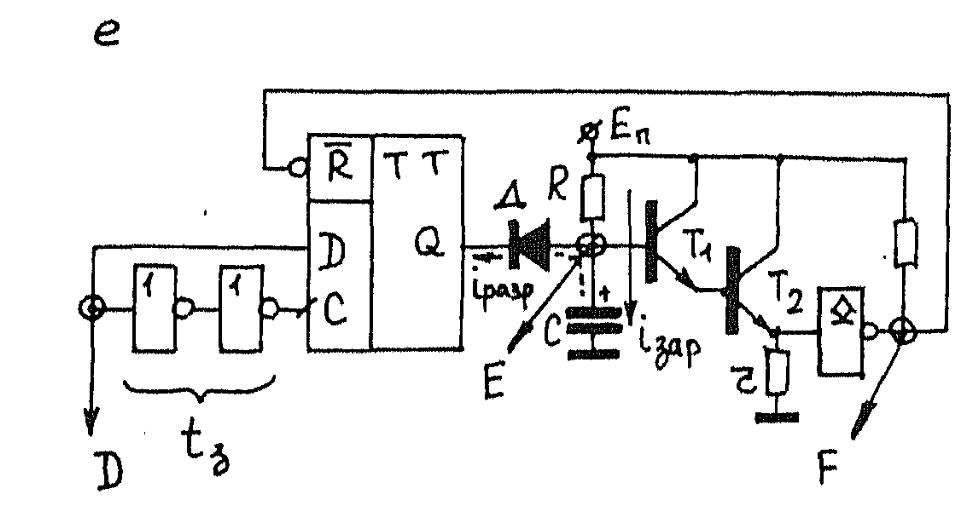

Вариант построения микросхем АГ1 и АГ3. Основу устройства составляет D-триггер, сигнал синхронизации формируется внутри схемы задержкой сигнала D на время последовательного переключения элементов 5 и 6. Время задающая цепь R-C отключается от триггера диодом Д под действием положительного перепада по входу D. К точкам E и F в микросхеме АГ3 подключены входы специальных формирователей для реализации действия кратковременного отрицательного импульса неR, инициализирующий дополнительную цепь быстрого разряда емкости без сброса триггера. После этого конденсатор начинает вновь заряжаться, т.е. проходит повторный запуск процесса генерации.

Билет № 15.

Операционные микросхемы ТТЛ: арифметические микросхемы, дешифраторы. Микросхемы мультиплексоров.

Операционные микросхемы специализированы на выполнении одной или класса операций. Допускается масштабирование, т.е. наращивание разрядности обрабатываемого двоичного кода путем каскадирования или построения пирамидальных структур. К арифметическим относятся микросхемы сумматоров - К155 ИМ 1,2,3, К555 ИМ 6,7; ускорения переносов – К155 ИП4, перемножителя К555 ИП9; АЛУ – К155 ИП3.

Микросхема К155 ИМ1 однозарядный полный сумматор с дополнительной входной логикой, К155 ИМ2 – двухразрядный сумматор, К155 ИМ3 и К555 ИМ6 – четырехразрядные. К155 ИМ3 имеет внутреннюю схему ускорения переносов. Микросхемы К555 ИМ7 и К555 Ип9 используются совместно. Наибольшее применение находят микросхемы АЛУ и ускорения переносов.

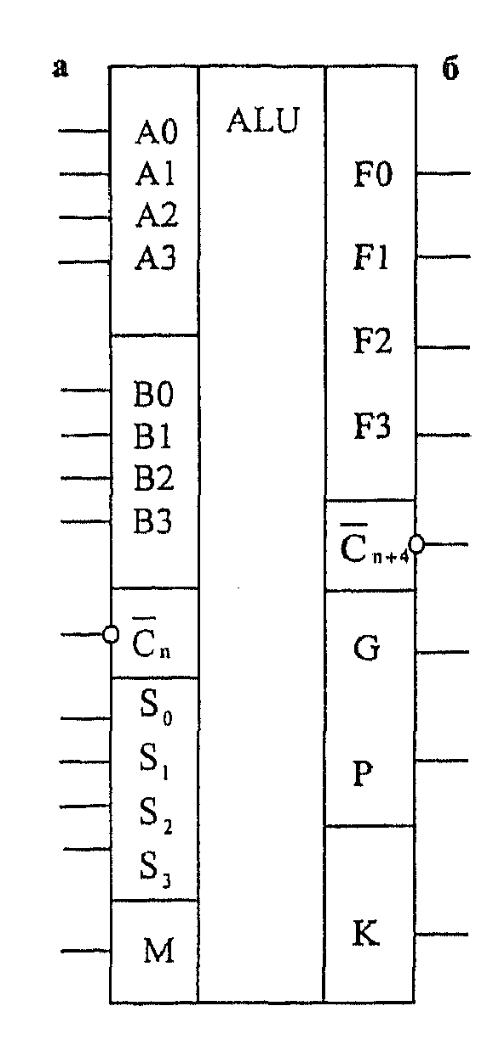

Микросхема

К155 ИП3 четырехразрядное скоростное

АЛУ, может работать в двух режимах,

выполнять 16 логических или 16 арифметических

операций. Для максимального быстродействия

при арифметической обработке данных

имеется схема ускорения переносов.

Логическая работа это выполнение

побитовых операций над парой операндов.

И поэтому АЛУ является универсальным

логическим модулем на две переменные

в каждом из 4-х независимых разрядов.

Выполняется только две арифметические

операции – сложение или вычитание с

возможным добавлением или вычитанием

1. Вариации достигаются тем, что операндами

могут выступать не только входные коды,

но и их побитовые инверсии, дизъюнкции,

конъюнкции.

Микросхема

К155 ИП3 четырехразрядное скоростное

АЛУ, может работать в двух режимах,

выполнять 16 логических или 16 арифметических

операций. Для максимального быстродействия

при арифметической обработке данных

имеется схема ускорения переносов.

Логическая работа это выполнение

побитовых операций над парой операндов.

И поэтому АЛУ является универсальным

логическим модулем на две переменные

в каждом из 4-х независимых разрядов.

Выполняется только две арифметические

операции – сложение или вычитание с

возможным добавлением или вычитанием

1. Вариации достигаются тем, что операндами

могут выступать не только входные коды,

но и их побитовые инверсии, дизъюнкции,

конъюнкции.

А3,…,А0 В3,…,В0 - входы операндов.

неСn – инверсный вход переноса в младший разряд.

S3,…,S0 - сигналы настройки на выполнении функции.

М – сигнал настройки на арифметический (М=0) или логический (М=1)тип функции.

F3,…,F0 - выходы результата.

неСn+4 – инверсный выход переноса в старший разряд.

G и P – выходы генерации и распространение переноса.

К – выход компаратора с открытым коллектором.

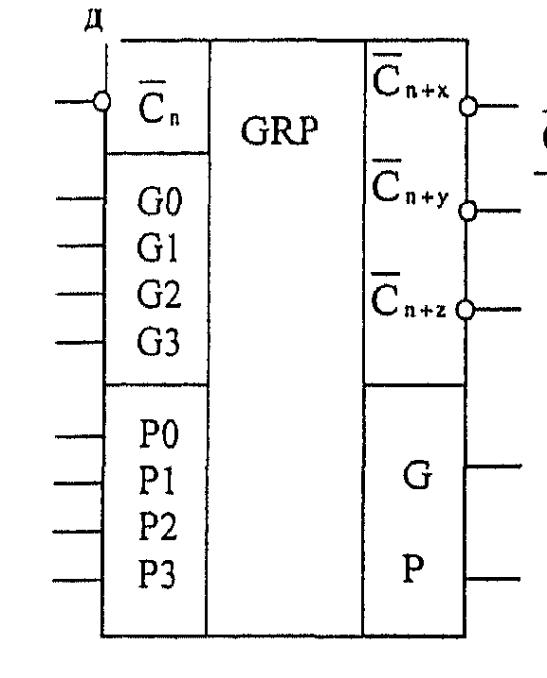

Микросхема К155 ИП4 это схема ускорения переносов, обслуживает 4 корпуса АЛУ, способствуя одновременному формированию переносов на входах всех тетрад 16-рязрядного сумматора, начиная со второй. Все функции переносов формируются 2-уровневым схемами с задержкой 13нс относительно сигналов Gi Pi. Эти сигналы генерируются всеми тетрадами одновременно, т.к. зависят только от значений битов слагаемых. Формирование сигналов Р и G происходит с задержкой 12нс относительно момента поступления слагаемых. Другие задержки АЛУ – tF = 24нс, tcn+4 = 12нс. Если к моменту поступления сигнала неGn формирование сигналов G и P завершено, то tF уменьшается до 12нс. Время операции сложения в данном устройстве равно 37нс. Для 16-разряного АЛу с последовательными переносами между тетрдами tП = 48нс. 32-разрядный сумматор строится из двух секций со связью по сигналу неС16, при этом

t =62нс. Эффект ускорения увеличивается до 35%, t снижается в 1,5 раза. Эффект от построения 64-разрядного АЛу составляет 40%, t уменьшается в 1,7 раза. Но если в 64-разрядном варианте используются 4 секции, а переносы между ними организовать параллельно с помощью микросхемы ИП4 второй степени, то получается ускорение в 3 раза. Т.о. наибольший эффект от применения микросхем ИП4 достигается при попстроении многоступенчатых схем ускорения переносов многоразрядных АЛУ.

Дешифратор, устройство для расшифровки (декодирования) сообщения и перевода содержащейся в нём информации на язык (в код) воспринимающей системы. Дешифратор - это комбинационное устройство, предназначенное для преобразования параллельного двоичного кода в унитарный, т.е. позиционный код. В общем случае дешифратор имеет n входов и m выходов. Поступающая на входы деширатора информация преобразуется — дешифрируется, — и на соответствующем выходе (группе выходов) выделяется сигнал, указывающий признак (или содержание) входной информации. Любому сигналу или комбинации сигналов на входах дешифратора соответствует определённый сигнал или комбинация сигналов на его выходах.

Логика работы микросхемы такова: на входы данных микросхемы подается цифровой код. Некое трехразрядное двоичное число. D0 – младший разряд числа, D2 – старший. Как известно тремя разрядами можно записать восемь различных значений. То есть при помощи трех разрядов можно представить числа от 0 до 7. Каждому числу соответствует свой выход дешифратора. Дешифратор, имеющий четыре информационных входа, будет иметь, соответственно, восемь выходов. Дешифраторы, имеющие максимально возможное количество выходов при данном количестве входов называются полными дешифраторами.

Д ешифраторов

с более, чем тремя входами данных,

выполненных в виде отдельных микросхем,

практически не производят, так как они

имели бы недопустимо большое количество

выводов. Однако наличие входов выбора

микросхемы позволяет каскадировать

дешифраторы. Для построения такой схемы

потребовался один дешифратор на два

входа и четыре дешифратора на три входа.

ешифраторов

с более, чем тремя входами данных,

выполненных в виде отдельных микросхем,

практически не производят, так как они

имели бы недопустимо большое количество

выводов. Однако наличие входов выбора

микросхемы позволяет каскадировать

дешифраторы. Для построения такой схемы

потребовался один дешифратор на два

входа и четыре дешифратора на три входа.

Дешифраторы широко применяются в микропроцессорной технике. И главное их применение – это обеспечение возможности подключения нескольких регистров или ячеек памяти к одной шине данных.

В состав различных серий ТТЛ входит 7 типов микросхем дешифраторов. Они различаются по числу дешифраторов в корпусе, по числу адресных входов в каждом дешифраторе, по формату адресного кода. Например микросхема К155ИД3 .

Мультиплексор - это устройство, которое осуществляет выборку одного из нескольких входов и подключает его к своему выходу, в зависимости от состояния двоичного кода, переключатель сигналов, управляемый двоичным кодом и имеющий несколько входов и один выход. К выходу подключается тот вход, чей номер соответствует двоичному коду. Устройство, преобразующее параллельный код в последовательный. Функционально мультиплексор состоит из m элементов конъюнкции, выходы которых объединены дизъюнктивно с помощью элемента ИЛИ с m входами. На одни входы всех элементов конъюнкции подаются информационные сигналы, а другие входы этих элементов соединены с соответствующими выходами дешифратора с n входами.

В составе серий ТТЛ есть более 11 типов

микросхем мультиплексоров. Эти схемы

различаются по числу входных сигналов,

наличием или отсутствием парафазного

выхода или специальных входов разрешения.

Выходы некоторых МС имеют три состояния

для организации работы на общую шину.

Микросхема К155 КП2 – это 2 четырехвходовых

мультиплексор, имеющие общие входы

адреса А1,А0.

Разрядность передаваемого кода растет

с увеличением числа используемых

корпусов.

составе серий ТТЛ есть более 11 типов

микросхем мультиплексоров. Эти схемы

различаются по числу входных сигналов,

наличием или отсутствием парафазного

выхода или специальных входов разрешения.

Выходы некоторых МС имеют три состояния

для организации работы на общую шину.

Микросхема К155 КП2 – это 2 четырехвходовых

мультиплексор, имеющие общие входы

адреса А1,А0.

Разрядность передаваемого кода растет

с увеличением числа используемых

корпусов.