- •Лекція №1 Основні положення задачі курсу

- •Лекція №2 Характеристика напівпровідників

- •Приєднання кристала до основи корпусу

- •Лекція №8 Гібридні інтегральні мікросхеми План

- •Загальні вимоги до логічних імс

- •Десятична система числення

- •Двійкова система численя

- •Література: с.В. Симонович и др. Информатика. Базовый курс. – сПб: Питер, 2005 – 640 с.

- •Відправлення сигналів

- •Обробка сигналів

- •Лекція №20 Дослідження роботи регістрів План

- •Призначення виводів

- •Лекція №17

- •Лекція №23 Взаємодія вузлів пеом-80

- •Література:

- •Лекція №24 Характеристика вузлів пеом-80

- •Література:

- •Загальна лекція

- •2. Однопрограмний і мультипрограмний режими керування

- •3. Сторінкова організація пам’яті

- •4. Використання віртуальної пам’яті в ос Windows та ос Unix

- •Лекція №25 Характеристика мікропроцесора к1810вм86

Лекція №17

Програмований таймер KP580BH53

План

Програмований таймер КР580ВН53

Призначення програмованого таймера КР580ВН53

Технічна характеристика

Умовне графічне позначення та призначення виводів

Структурна схема та принцип роботи

Побудова керуючого слова

Приклад програми в Assembler

Висновки

Програмувальний таймер використовується для завдання часових інтервалів у мікропроцесорних системах і може застосовуватися як одновібратор із програмувальною тривалістю імпульсів, програмований дільник частоти й лічильник зовнішніх подій.

Технічні характеристики

Технологія п-МОП

Тип корпуса 2120.24-3

Число виводів 24

Тактова частота сигналів, що надходять на входи

CLC, МГц ≤2

Споживана потужність, Вт ≤1

Навантажувальна здатність 1 ТТЛ вхід

Напруга, В:

джерела живлення +5 ±5%

вихідне низького рівня (IOL=2 мА) ≤0,45

вихідне високого рівня (IOH = -400 мкА) ≥2,4

вхідне низького рівня ≤0,8

вхідне високого рівня ≥2

Діапазон робочих температур, °С від -10 до +70

Маса, г <5

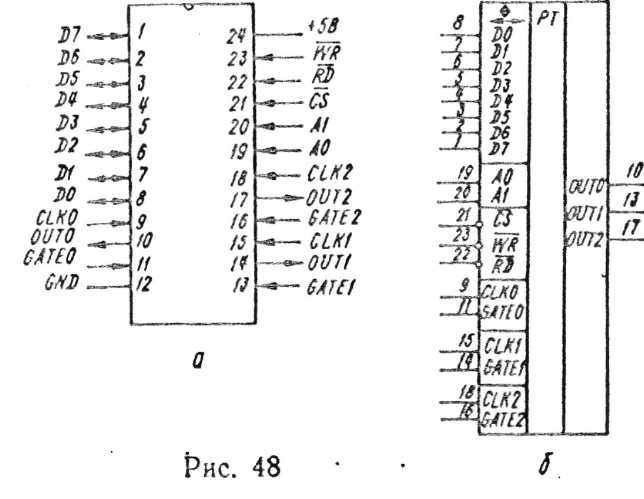

. На мал. 48, а показане схематичне зображення корпуса мікросхеми таймера, а на мал. 48,6 — умовна позначка на принциповій електричній схемі. У табл. 18 наведене функціональне призначення виводів.

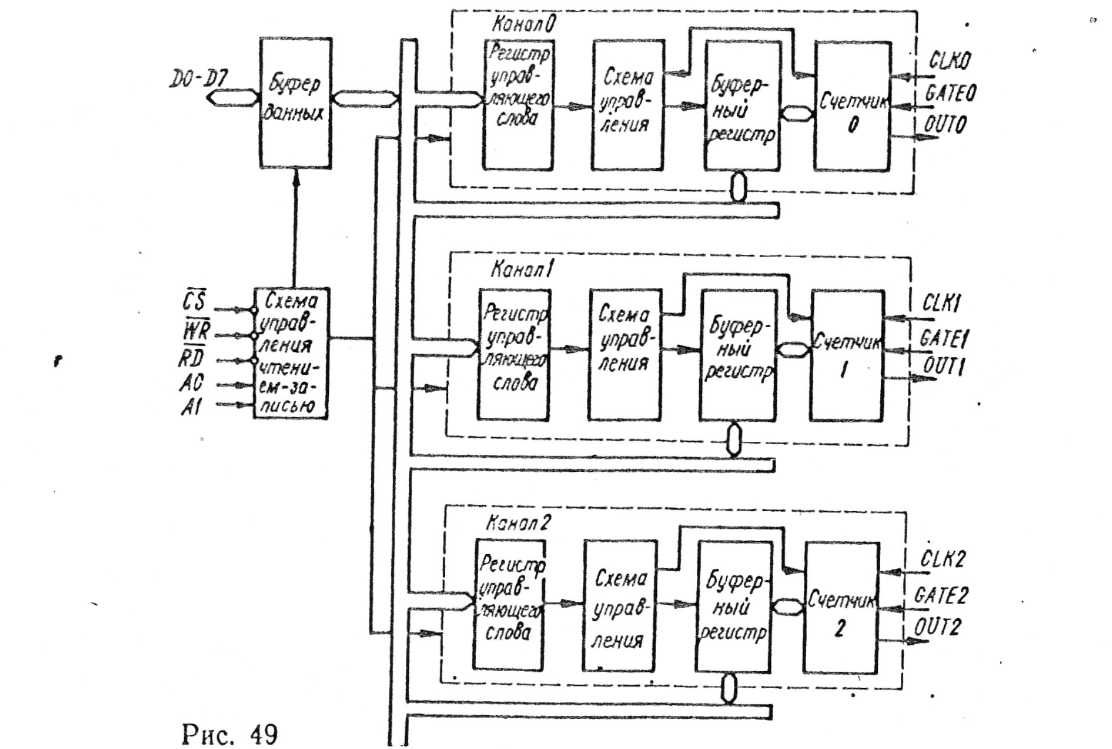

До складу таймера входять: буфер шини даних, схема керування введенням-виведенням, три канали, кожний з яких містить регістр керуючого слова, схему керування каналом, буфер, 16-розрядний лічильник, що працює на вирахування (мал. 49).

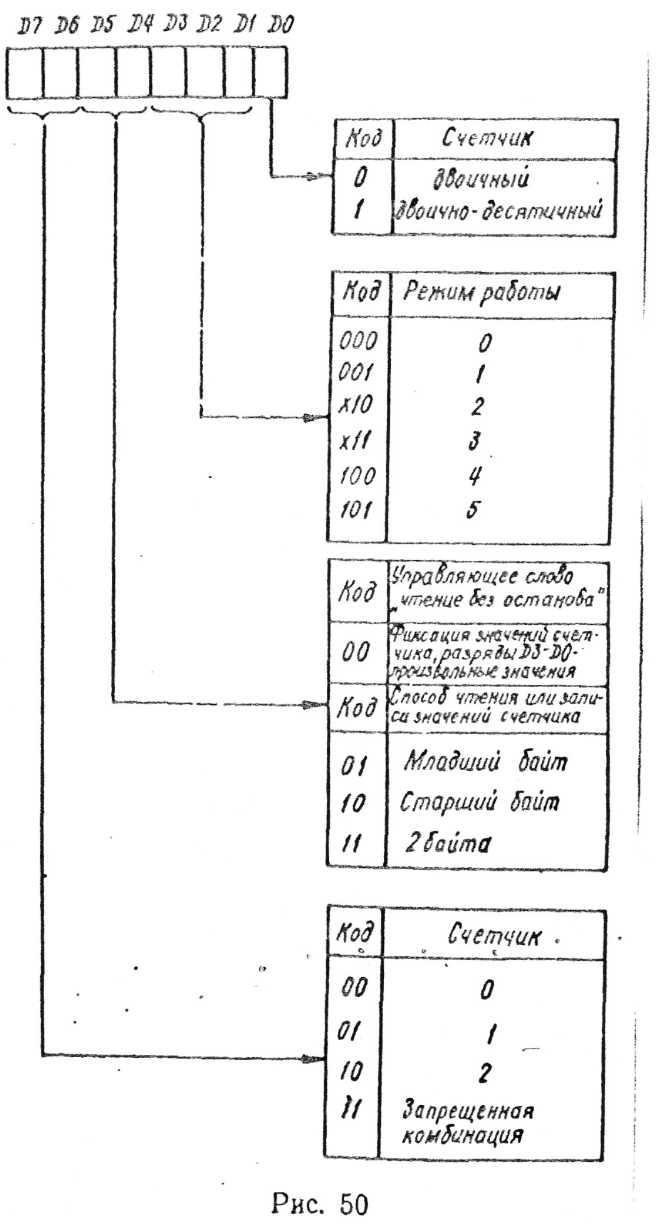

Програмування таймера. Кожний з лічильників залежно від настроювання може бути або двійковим, або десятковим, а також працювати в одному із шести режимів - 0, 1,2, 3, 4, 5. Для програмування режиму роботи кожного з лічильників в 8-розрядний регістр керуючого слова необхідно командою OUT заслати з мікропроцесора по шині даних відповідний код - керуюче слово. При цьому на входи таймера А0 і А1 повинні бути подані сигнали високого рівня, на входи CS і WR - дозволяючі сигнали низького рівня. Запис керуючих слів для різних лічильників можна робити в будь-якій послідовності. Залежно від комбінацій керуючих сигналів на входах CS, WR,

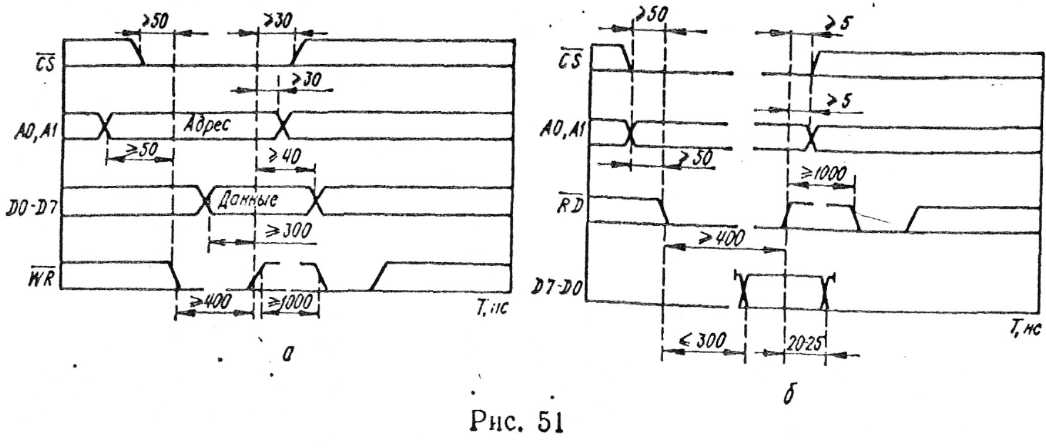

RD, А0, А1 різні пристрої таймера підключаються до шини даних відповідно до табл. 19, з якої видно, що записувати інформацію можна в лічильники й регістр керуючого слова, а зчитувати тільки з лічильників. Структура керуючого слова зображена на мал. 50. Слідом за керуючим словом за допомогою команди OUT у лічильник таймера заноситься початковий уміст, 2 або 1 байт. Тривалість сигналу запису їх повинна бути не менш 40 нс. Інтервал між сигналами WR при багаторазовому записі не менш 1 мс (мал. 51 ,а,б).

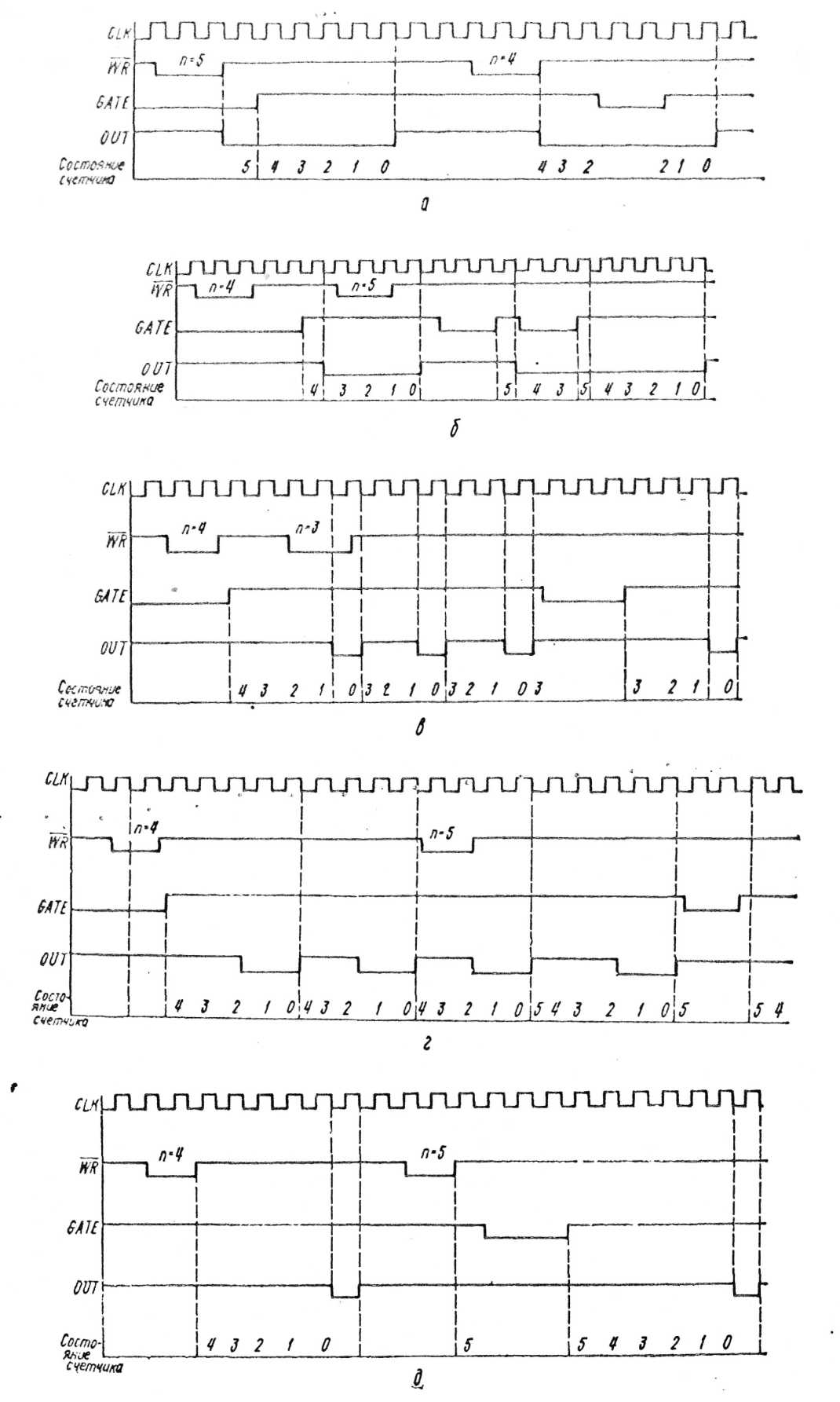

Режим 0 (мал. 52, а). З моменту запису числа в лічильник, настроєний на режим 0, до закінчення рахунку на відповідному виході OUT тримається сигнал низького рівня. Після закінчення рахунку рівень сигналу на виході становиться високими і зберігається до наступного завантаження

Номер виводу |

Позначення |

Тип виводу |

Функціональне призначення |

|||||

12 24 1-8

21 23 22 19, 20

9,15,18

11,13,16 10,14,17 |

GND +5В D 7-D0

CS WR RD А0, А1

CLC0 -CLC2

GATEO-GATE2

OUT 0-OUT2 |

— — Входи-Виходи з високоімпедансним станом Вхід » » Входи

»

»

Виходи |

Загальний Живлення Дані виводи 1—8 підключаються до шини даних системи

Вибір мікросхеми Запис Читання Вибір каналу, регістрів керуючих слів Синхровходи. На виводи 9, 15, 18 подаються синхроімпульси, підрахунок яких виконується відповідно на лічильниках 0—2 Керуючі входи лічильників 0-2 Виходи лічильників |

|||||

CS |

WR |

RD |

А1 |

А0 |

Напрямок передачі інформації |

|||

0 |

0 |

1 |

0 |

0 |

D7-D0-лічильник 0 |

|||

0 |

0 |

1 |

0 |

1 |

D7-D0-лічильник 1 |

|||

0 |

0 |

1 |

1 |

0 |

D7 -DO-лічильник 2 |

|||

0 |

0 |

1 |

1 |

1 |

D7-DO-регістр керуючого слова |

|||

0 |

1 |

0 |

0 |

0 |

Лічильник 0-D7-DO |

|||

0 |

1 |

0 |

0 |

1 |

Лічильник 1-D7-DO |

|||

0 |

1 |

0 |

1 |

0 |

Лічильник 2-D7-D0 |

|||

0 |

X |

0 |

1 |

1 |

D7-DO- у високоімпедансному стані |

|||

0 |

1 |

1 |

X |

X |

D7-DO- у високоімпедансному стані |

|||

1 |

0 |

0 |

0 |

0 |

D7-DO- у високоімпедансному стані |

|||

Режим 1 (програмувальний одновібратор) (мал. 52,6). На виході лічильника, що працює в цьому режимі, формується негативний імпульс тривалістю пТсlс, причому низький рівень на виході OUT установлюється із другого такту синхросерії після надходження на вхід GATE сигналу високого рівня. На відміну від режиму 0 нове число, завантажене під час рахунку, не впливає на стан виходу лічильника, а враховується на наступному запуску. Крім того, у даному режимі програмується не момент переходу до високого рівня сигналу на виході лічильника, а тривалість негативного імпульсу. Особливістю даного режиму є також те, що перезапуск лічильника можна здійснити без попереднього перезавантаження, що необхідна в режимі 0.

Режим 2 (програмувальний дільник частоти)

(рис. 52,в). Щоразу після прорахунку числа, записаного в лічильник, на виході OUT у до такті (k=0 (mod n)) з'являється негативний імпульс тривалістю в один період тактової частоти. Завантаження лічильника новим числом під час рахунку не впливає на момент появи імпульсу на виході OUT. Лічильник перебудовується на новий коефіцієнт перерахування лише після його запуску. При зникненні сигналу високого рівня на вході GATE припиняється рахунок, і на виході OUT установлюється напруга високого рівня. Перезапуск лічильника здійснюється при "наявності сигналу високого рівня на керуючому вході GATE.

Режим 3 (програмувальний дільник частоти на 2) (мал. 52,г). Якщо в лічильник, настроєний на даний режим, завантажене парне число, то тривалості негативних і позитивних напівперіодів на виході OUT рівні між собою й визначаються по формулі Tclcn/2. У випадку непарного n негативний напівперіод вихідного сигналу менше позитивного на Тсlс. Завантаження лічильника новим числом під час рахунку не впливає на поточний період, однак наступний прорахунок буде здійснюватися з новим коефіцієнтом перерахування. Низький рівень сигналу на вході GATE (або спад сигналу) забороняє рахунок, і на виході лічильника встановлюється сигнал високого рівня. Сигнал високого рівня дозволяє рахунок, а позитивний перепад запускає лічильник з початкового стану. Слід зазначити, що числом 3 лічильники в цьому режимі завантажувати не можна.

Режим 4 (лічильник подій) (мал. 52,д). У режимі 4 по закінченні рахунку числа, завантаженого в лічильник, на виході OUT з'являється негативний імпульс тривалістю Tclc- Запис у лічильник під час рахунку молодшого байта не впливає на поточний рахунок, а запис старшого байта перезапускає лічильник. Напруга низького рівня або негативний фронт на вході GATE забороняє рахунок, а сигнал високого рівня — дозволяє.

Режим 5 (лічильник подій з автозавантаженням) (мал. 52,е). Відмінність від режиму 4 полягає в тому, що лічильник є що перезапускається, тобто кожне наростання сигналу на вході GATE перезапускає лічильник. Завантаження лічильника новим числом не впливає на тривалість поточного циклу, однак наступний буде визначатися знову занесеним числом.

Якщо потрібне зчитування вмісту лічильника, то воно може здійснюватися двома способами: з зупинкою і без зупинки лічильника, У першому випадку робота лічильника припиняється або зняттям сигналу на вході GATE, або блокуванням надходження тактових імпульсів. Читання вмісту лічильника здійснюється або за допомогою двох команд IN (спочатку молодший байт, а потім старший, якщо в керуючому слові було D5=1; D4=1), або за допомогою однієї команди IN (молодший байт, коли D5=0; D4=1, або старший байт, коли D5=1, D4=0). Читання без зупинки можливо лише у випадку попереднього завантаження командою OUT керуючого слова з нулями в розрядах D4, D5. У розрядах D7 і D6 вказується номер лічильника, а вміст розрядів D3 - DO несуттєво. Після завантаження цього керуючого слова вміст лічильника читається двома командами IN.

Питання:

Що таке програмовани таймер КР580ВН53?

Яке його призначення?

Література:

Товкес В.С., Шабаев В.Н., Мікропроцесорні системи(Частина I)

Товкес В.С., Шабаев В.Н., Мікропроцесорні системи (Частина II)

Лекція №18

Синтез синхронних автоматів

План

Основна модель синхронного автомата

Процес синтезу синхронного автомату

Основна модель синхронного автомата

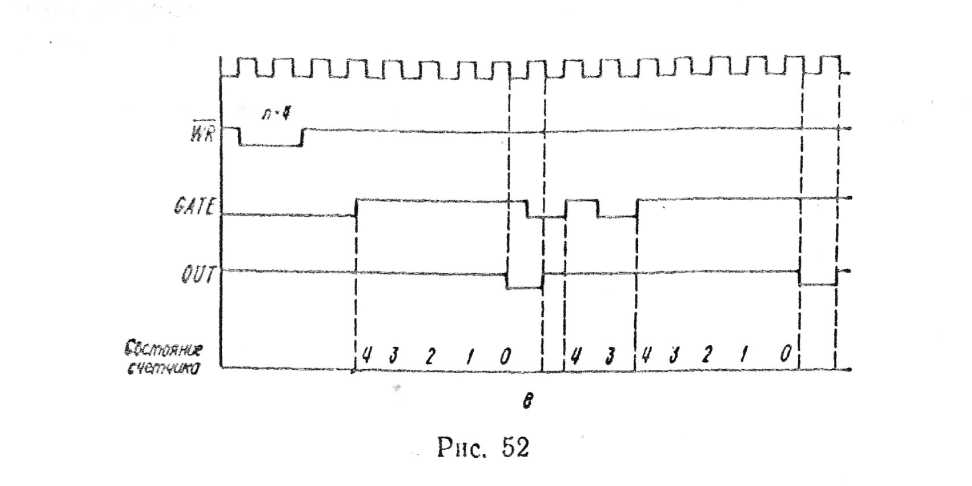

Основна модель синхронного автомата (мал. 4.1) відрізняється від моделі асинхронного потенційного автомата (див. мал. 3.1) лише властивостями ЕП типу D, які управляються тактовим сигналом Н. У синхронних ЕП тактовий сигнал Н чинить на них імпульсну дію тільки у момент зміни з 1 на 0 (чи тільки з 0 на 1), а зміни інформаційних сигналів

Dr = Q+, г = 1,2,.., m(4.1)

не впливають на ЕП, тобто формула (4.1) справедлива тільки при dH = 1, а при dH = 0 сигнал Q+ = Qr . Помітимо, що поняття "тригер" і "ЕП" для синхронних автоматів рівнозначні. З (4.1) витікає, що функція переходів тригера типу D

Qt = Dr(4.2)

з урахуванням тактового сигналу dH описується мультиплексною функцією

Qt = Dr - dHS/Qr - dH.(4.3)

Зрозуміло, що інформаційні сигнали Dr не повинні змінюватися при dH = 1, оскільки вони при цьому мають невизначене значення Ф, а значить, порушується детермінована переходів автомата. З цього виходить, що і вхідні сигнали автомата хр не повинні змінюватися при dH = 1. Ці обмеження на зміни інформаційних сигналів описуються

рівняннями

VDT dH = 0, Vzp - dH = 0.(4.4)

На мал. 4.2 показані тимчасові діаграми, що пояснюють роботу синхронного автомата. Моменти зміни тактового сигналу з 1 на 0 задають дискретний час <д = 1,2,3,.. . Тільки в ці дискретні моменти часу внутрішній стан автомата може змінюватися. Перехідний процес, викликаний в КС цією зміною в даний момент часу <д, повинен закінчитися до наступного дискретного моменту часу /д + 1 для виконання першої умови з (4.4). З цього виходить, що максимальна частота тактового сигналу має бути обмежена деякою величиною. Зрозуміло, що мінімальне допустиме значення періоду тактового сигналу Т# (мал. 4.2) повністю визначається швидкодією ЕП і КС.

Замінивши в (3.1) і (3.2) безперервний час на дискретний, отримаємо функції переходів і виходу синхронного автомата :

Qt = fr(xn,.., xuQm,.., Qi), г = 1,2,.., та(4.5)

zq = <pq(xn,.., xi, Qm,.., Qi), q= 1,2,.., до (4.6)

де хр = xp(ta), р = l, 2,.., n; QT = QT{ta), Qt - Qr(ta+ 1), zq = zq(ta). Нагадаємо, що умови (4.4) повинні дотримуватися в обов'язковому порядку. Виконання цих умов гарантує детерміновану переходів автомата при помилкових значеннях функції (4.5) під час перехідного процесу, оскільки вони зможуть з'явитися тільки при значенні сигналу dH = 0, а значить не викличуть спрацьовування ЕП. Отже можна сказати, що синхронні ЕП (тригери) мають властивості, що фільтрують, оскільки усі зміни інформаційних сигналів ті, що відбуваються на інтервалі часу, коли сигнал dH = 0, не пропускаються на їх вихід. З цього виходять важливі для синтезу синхронних автоматів висновки:

КС можуть синтезуватися скованими від змагань;

допускаються несусідні зміни станів входу;

допускаються змагання ЕП, тобто кодування внутрішніх станів автомата може вироблятися довільним способом (можливе несусіднє кодування).

Таким чином, при проектуванні синхронних автоматів не вимагається враховувати перехідні процеси, а досить тільки виконати умови (4.4), що досягається відповідним вибором значення частоти тактового сигналу Н і забороною на зміни вхідних сигналів хр при dH = 1. Якщо ці сигнали поступають від зовнішнього джерела, не синхронізованого з тактовим сигналом, то слід використовувати схеми тимчасової прив'язки, як які можна застосувати D -триггери, що описуються функцією переходів (4.3), :

Qt = xp - dH\/Qp - d~H.

Виключення з розгляду в синхронних автоматах перехідних процесів значно спрощує методи їх синтезу.

Відповідність вихідних сигналів синхронних автоматів zq функціям виходу (4.6) гарантована тільки в дискретні моменти часу <д, коли сигнал dH = 1 (під час перехідного процесу на виходах zq можуть з'являтися помилкові значення цих сигналів із-за змагань ЛЕ в КС і змагань ЕП). При максимально допустимій частоті тактового сигналу рівність (4.6) виконуватиметься тільки і тільки в дискретні моменти часу ta = 1,2,3,.. . Вихідні сигнали zq в цьому випадку слід стробувати (виділяти) сигналом dH, тобто використовувати їх у вигляді zq dH. Такі імпульсні вихідні сигнали не завжди практично прийнятні. Перетворити їх в потенційні сигнали можна за допомогою D -триггеров, включивши на виходах zq (див. мал. 4.1) такі ж ЕП, що і формуючі внутрішні сигнали QT. Дійсно, підставивши в (4.3) замість Dr сигнали z4, отримаємо:

,,- ,,- f z" при dH = 1

де zq = г,(<д), z* = zg(ta - 1), тобто в даному випадку вихідні потенційні сигнали автомата z* набувають істинного значення в дискретний момент часу ta і зберігають його до моменту часу <л + 1, тобто запізнюються на один такт по відношенню до сигналів Qr. Такий прийом отримання вихідних сигналів завжди використовується при проектуванні синхронних автоматів з максимально досяжною швидкодією.

Якщо вхідні сигнали автомата хр і вихідні сигнали ЕП Qr змінюються тільки при значеннях тактового сигналу Я = О (перехідний процес, що виникає в автоматі у момент зміни тактового сигналу з 1 на 0, повинен закінчуватися до моменту його зміни з 0 на 1), то помилкові значення вихідних сигналів zq можна виключити за допомогою операції zq Я. В цьому випадку значення вихідних сигналів в точності відповідатимуть функції виходу (4.6) не в одній точці <д, для якої сигнал dH = 1, а на інтервалі часу, протягом якого значення тактового сигналу Я = 1. Такий метод усунення помилкових значень вихідних сигналів може бути використаний при відносно низькій частоті тактового сигналу в порівнянні з максимально допустимою частотою, визначуваною швидкодією використовуваних в автоматі ЛЕ і ЕП.

У асинхронних потенційних автоматах внутрішні стани змінюються під впливом зміни вхідних сигналів хр, а в синхронних - під впливом сигналу dH = 1, тому стани синхронного автомата можуть змінюватися і при незмінному стані його входу. Це означає, що на деякі синхронні автомати взагалі можна не подавати вхідні сигнали. Прикладами таких автоматів є синхронні лічильники, використовувані, наприклад, як таймери, що формують задані інтервали часу. Автомати, що не мають жодного фізичного входу, описуються відповідно до (4.5) і (4.6) функціями переходів і виходу

Qt = MQm,.., Qi), г= l, 2,.., m, )

z, = v,(Qm,.., Qi), "=1,2,..,* J{

і називаються автономними автоматами.

Основна модель являється найбільш проста, що пояснюється наявністю в ній тільки синхронних тригерів типу D, описуваних примітивною функцією переходів (4.2). У інших моделях автоматів використовуються тригери інших типів, функції переходів яких не дозволяють виразити функції збудження їх входів тільки через сигнал <3+. З цим пов'язано деяке ускладнення процедури синтезу автоматів, але функції збудження можуть виявитися значно простіше, ніж у D -триггеров. У загальному випадку автомат може містити декілька різних типів тригерів.

Питання:

Намалюйте діаграми, на яких буде показано роботу синхронного автомата?

Які автомати називаються автономними?

Електроний ресурс:

http://sio.su/manual_127_29_gen.html

Лекція №19

Мікропроцесор К1810ВМ86. Призначення, основні технічні характеристики

План

Призначення мікропроцесорного комплекту К1810

Технічні характеристики МП К1810ВМ86

Мікропроцесорний комплект К1810 призначений для побудови як простих одноплатних МІКРОЕОМ так і потужних мультипроцесорних пристроїв в системах управління технологічними процесами і обробки сигналів [15]. Ядром цього МПК став МП I - 8086, розроблений в 1978 р. Цей МП став потужним засобом для створення ПЕВМ. Проте він цілком може бути використаний і для розробки МК. Склад МПК 1810 [9]:

- К1810ВМ86 - мікропроцесор;

- К1810ВМ87 - співпроцесор для реалізації операцій з

плаваючою комою;

- К1810ВМ88 - 8-розрядний мікропроцесор;

- К1810ГФ84 - тактовий генератор;

- К1810ВН59 - контроллер переривань;

- К1810ВГ88 - контроллер шин.

Технічні характеристики МП К1810ВМ86

Технічні характеристики К1810ВМ86 наступні [9,15]: - ШД - 16 розрядів; - ША - 20 розрядів; - адресний простір - 220 = 1Мбайт; - програмно-доступні регістри - 12 (AX, BX, DX, CX, BP, SI, DI, IP, CS, SS, DS, ES); - пам'ять - сегментована по 64 кбайта; - довжина команди - змінна від 1-го до 6-ти байт; - максимальна тактова частота fТ = 5 Мгц; - використовується 40-выводный корпус. Особливості МП К1810ВМ86 : - розширена система адресації - 24 способи; - наявність команд множення, ділення і послідовності байтів і слів; - наявність шести регістрів черги - прообраз Кеш-пам'яті. Регістри черги запол¬няются наступною командою. Заповнення регістрів черги відбувається одночасно з ви¬полнением попередньої команди; - розвинена система переривань, використовується 256 запитів на переривання; - є апаратні засоби для реалізації багатопроцесорної системи. По організації пам'яті МП К1810ВМ86 є машиною Фон-Неймановского типу, оскільки пам'ять даних і пам'ять команд знаходяться в єдиному адресному просторі. Крім того, МП К1810ВМ86 відноситься до ВС з програмним управлінням, при якому потрібний дешифратор команд.

Питання:

Призначення мікропроцесорного комплекту К1810

Надайте склад мікропроцесора?

Перелічіть технічні характеристики МП К1810ВМ86 ?

Література:

Товкес В.С., Шабаев В.Н., Мікропроцесорні системи(Частина I)

Товкес В.С., Шабаев В.Н., Мікропроцесорні системи (Частина II)

Лекція №20

Формування фізичної адреси. Організація зовнішньої пам'яті.

План

Фізична адреса

Формування фізичної адреси

Формування виконавської адреси

Фізична адреса

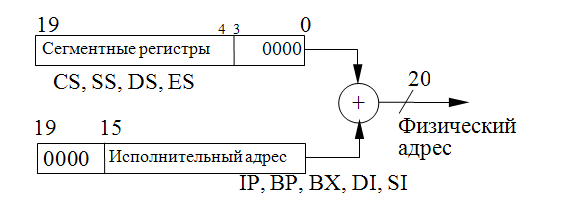

МП К1804 має 20-розрядну ША, яка забезпечує адресний простір в 1 Мбайт. Адреса на ША МП називається фізичною адресою. У МП широко використовуються різні способи непрямої адресації, коли джерелом адреси служать індексні і базові 16-розрядні регістри. В цьому випадку говорять про виконавську ( чи логічному) адресу - EA. Виконавську адресу можна визначити як адреса в межах сторінки пам'яті, номер якої визначений сегментним регістром. Яким же чином формується 20-розрядна фізична адреса з 16-розрядної виконавської адреси? На малюнку 3.4.1 представлена схема формування фізичної адреси, прийнята для МП К1810ВМ86.

Формування

фізичної адреси

Формування

фізичної адреси

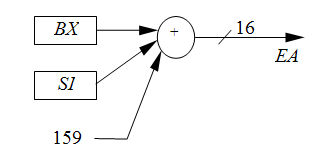

Для формування фізичної адреси виконується підсумовування виконавської адреси з вмістом сегментного регістра, зрушеного на 4 розряди вліво. Виконавська адреса формується за допомогою комбінації вмісту декількох (до двох) регістрів і за допомогою прямого адресного зміщення, вказаного в команді. Наприклад, виконавська адреса в команді MOV AX, [BX+SI+159] формується з двох регістрів і додаткового прямого зміщення (малюнок 3.4.2).

Формування виконавської адреси

При проектуванні МК необхідно врахувати, що пуск МП К1810ВМ86 після зняття сигналу скидання SR виконується з фізичної адреси FFFFOh. Ця адреса виходить в результаті підсумовування за схемою, представленою на малюнку 3.4.1, і з урахуванням того, що в сегментний регістр завантажується код FFFFh, а регістр адреси в межах поточного сегменту IP формує код 0000h.

Організація зовнішньої пам'яті

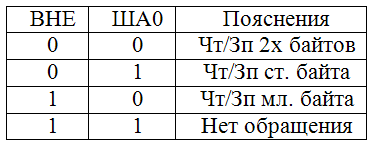

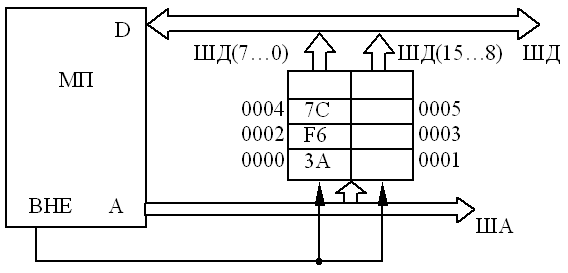

Пам'ять в МП, що розробляються фірмою Intel, організована побайтно. Навіть у МП останнього покоління типу Pentium при 64-розрядній ШД пам'ять все одно організована побайтно. Для реалізації можливостей, які відкривають ШД більше за один байт в усіх МП цієї архітектури передбачено читання кодів з пам'яті словами. Нагадаємо, що слово - це основний формат шини даних даної обчислювальної системи. Для МП К1810ВМ86 слово - це 16 розрядів, тобто два байти. Тому, разом з режимами побайтного звернення до зовнішньої пам'яті в цьому МП передбачений режим читання-запису слова

Режим читання-запису слова

Організація

зовнішньої пам'яті

Організація

зовнішньої пам'яті

Для можливості звернення по словах і по байтах пам'ять розділена на 2 банки з парними і непарними адресами, причому осередки з парними адресами підключаються до молодшого байта ШД, а з непарними - до старшого. Для вибору відповідного банку пам'яті використовується сигнал BHE спільно з розрядом ША0. Таким чином при проектуванні МК потрібно два ПЗП і два ОЗУ. Сигнал вибору банку пам'яті повинен враховувати таблицю приведену вище і загальний сигнал дозволу вибору пам'яті - ПЗП або ОЗУ.

Питання:

Що таке фізична адреса?

Як формується фізична адреса?

Як формується виконавської адреси?

Електроний ресурс:

http://microprocesser.narod.ru/ind5.html

Лекція №21

Мікросхема К1810ВМ86 (Intel 8086)

План

Мікросхема К1810ВМ86 (Intel 8086).

Функціональна схема

Мікросхема К1810ВМ86 (Intel 8086).

Шестнадцатиразрядный однокристальний МП виконує близько 2 млн. операцій в секунду. Синхронізується тактовою частотою 25 МГЦ.

Має 20-ти розрядну шину адреси, що дозволяє забезпечити пряму адресацію 1 Мбайт зовнішньої пам'яті. Область адресного простору пам'яті розбита на сегменти по 64 Кб. Така організація пам'яті забезпечує зручний механізм обчислення фізичних адрес . ША і ШД мультиплексированы. При організації обчислювальних систем їх треба розділити (регістри-клямки). МП може звертатися як до пам'яті, так і до зовнішніх пристроїв.

При зверненні до зовнішніх пристроїв використовуються 16 молодших ліній ША. Отже можна підключити 64 До 8-бітових зовнішніх пристроїв, або 32 До 16-ти розрядних. МП має багаторівневу систему переривань : 256 векторів переривань. Цей МП є подальшим вдосконаленням К580ВМ80. Система команд схожа, але більше розширена. Програмне забезпечення легко перекладається з одного МП на інший.

Функціональна схема:

Див. мал.

У

перший такт обміну на AD0 - 15 встановлюються

молодші 16 біт адреси пам'яті або адреса

зовнішнього пристрою, супроводжується

ця інформація сигналом ALE. У другому

такті обміну виставляються дані, які

супроводжуються сигналом DEN. ALE і DEN

управляють регістрами-клямками. AD16/ST3

- AD19/ST6 - мультиплексовані лінії адреси

стану

У

перший такт обміну на AD0 - 15 встановлюються

молодші 16 біт адреси пам'яті або адреса

зовнішнього пристрою, супроводжується

ця інформація сигналом ALE. У другому

такті обміну виставляються дані, які

супроводжуються сигналом DEN. ALE і DEN

управляють регістрами-клямками. AD16/ST3

- AD19/ST6 - мультиплексовані лінії адреси

стану

У перший такт обміну видається 4 старші розряди адреси пам'яті, а при зверненні до зовнішнього пристрою - нулі. У другому такті видаються сигнали стану МП, причому сигнали ST3 - ST4 визначають сегментний регістр що бере участь у формуванні фізичної адреси.

ST3 |

ST4 |

Рег. |

0 1 0 1 |

0 0 1 1 |

ES SS CS DS |

Сегментні регістри. Беруть участь у формиро- вании фізичної адреси.

ST5 - дублює стан прапора дозволу переривань.

BHE - дозвіл старшого байта. Працює спільно з сигналом А0, забезпечуючи механізм передачі інформації по ШД.

-

BHE

A0

Вид передачі даних

0

0

1

1

0

1

0

1

Передається 16-ти бітове слово

Передається старший байт AD8 - AD15

Передається молодший байт AD0 - AD7

Немає звернення

RD -сигнал

читання.

RD -сигнал

читання.

WR - сигнал запису.

M/IO - звернення до пам'яті або зовнішніх пристроїв.

DT/R - напрям передачі інформації :

"1" - в МП; "0" - з МП.

INTA, INTR - запит на масковане переривання (INTA - підтвердження переривання).

NMI - запит на немасковане переривання.

HOLD - запит на переходження в режим прямого доступу до пам'яті.

HLDA - підтвердження захоплення шини.

TEST - перевірочний вхід, використовується в команді WAIT для організації неодружених тактів : "1" - МП виконує "0", з періодичністю 5 Т перевіряє стан цього сигналу.

MN/MX - мінімальний / максимальний режими, що визначають конфігурацію обчислювальної системи. MN - обмеження об'єму пам'яті і так далі.

Питання:

Що собою представляє мікросхема К1810ВМ86 (Intel 8086)?

Намалюйте функціональну схему?

Електроний ресурс:

http://www.studfiles.ru/dir/cat32/subj1245/file11267/view113893.html

Лекція №22

Архітектура МП. Сегментація пам'яті і обчислення адрес

План

Архітектура МП

Сегментні регістри

Архітектура МП

МП містить у своєму складі 14 регістрів загального призначення.

AX=AH+AL

BX=BH+BL

CX=CH+CL

DX=DH+DL

Усі інші регістри загального призначення є неподільними:

SP використовуються при зверненнях до стека для зберігання

BP адресної інформації

SI при зверненні до пам'яті або зовнішнього пристрою

DI

Сегментні регістри:

CS - визначать початкову адресу сегменту коду в якому зберігається програма;

SS - зберігає початкову адресу сегменту стека;

DS - початкова адреса сегменту даних;

ES - початкова адреса додаткового сегменту під дані;

IP - зберігає зміщення чергової команди переданої для виконання.

DA=CS+IP

F - регістр прапорів

|

|

|

00F |

DF |

IF |

SF |

ZF |

|

AF |

|

PF |

CF |

AD15 AD0

CF - прапор перенесення, фіксує виникнення перенесення при складанні або при відніманні, а також висунення старшого байта при операціях зрушення;

PF - прапор парності, фіксує парне число;

AF - прапор допоміжного перенесення, фіксує перенесення або позику з розряду D4 в D3 при операції складання і з D3 в D4 при відніманні. Використовується при перетворенні кодів з двійкового в двійково-десятковий і навпаки;

ZF - прапор нуля, сигналізує про отримання нульового результату;

SF - прапор знаку, дублює стан старшого біта результату операції;

OF - прапор переповнювання розрядної сітки, сигналізує про втрату старшого біта при складанні.

Названі 6 прапорів сигналізують про результати арифметичних операцій. Що залишилися 3 прапори відносяться до прапорів управління :

DF - прапор напряму обробки команд програми, "0" -выполняется команда від менших адрес до великих.

IF - прапор дозволу переривань, якщо він встановлений, то процесор реагує на запити переривання по входу INTR;

TF - прапор трасування, "1" - МП виконує команди програми в покроковому режимі.

До складу МП входить пристрій управління, який дешифрує команди і забезпечує відповідні сигнали, що управляють. Є регістр - черга команд об'ємом 6 байт в який завантажується чергова команда призначена для виконання. Буфер шини адреси - даних є 16 двонаправлених підсилювачів, що забезпечують номінальну здатність навантаження шини. Буфер адреси складається з 4-х двонаправлених підсилювачів тих, що виконують аналогічну функцію. Суматор адрес служить для обчислення фізичних адрес елементів пам'яті. АЛУ - 16-ти розрядне.

Сегментація пам'яті і обчислення адрес.

Пам'ять в ЕОМ на базі К1810ВМ86 організовується як одновимірний масив байтів, кожен з яких має свою 20-розрядну фізичну адресу(00000 - FFFFF).

Порядок розміщення даних в пам'яті звичайний: слово займає 2 сусідні елементи пам'яті, причому першим йде молодший байт слова, а другим старший. Фізичною адресою слова вважається адреса молодшого байта слова.

20-ти бітова фізична адреса елементу пам'яті міститься в об'єкті: сегмент + зміщення. Причому на сегмент і на зміщення відводиться по 2 байти. Отже повна фізична адреса розміщується в 4-х елементах пам'яті.

0 0002 зміщення

0002 зміщення

0 0003

00004 сегмент

00005

Фізичною адресою цього модуля вважається адреса молодшого байта зміщення.

Увесь простір пам'яті об'ємом 1М розбите на сегменти по 64 До (16 сегментів). Кожному сегменту програмою задається його початкова адреса який заноситься в сегментні регістри (CS, SS, DS, ES).Така організація обчислень 20-ти розрядної фактичної адреси обумовлена тим, що МП являється 16-ти розрядним і усі обчислювальні операції повинні виконуватися словами.

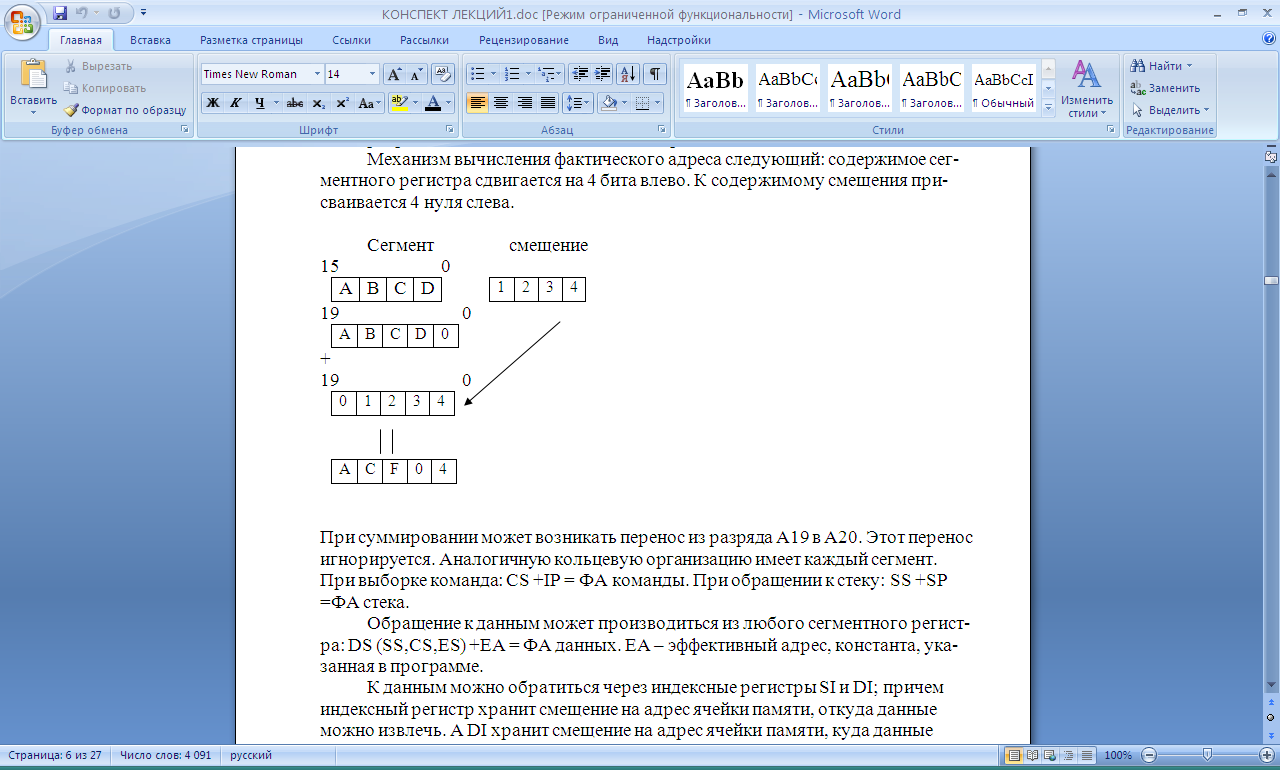

Механізм обчислення фактичної адреси наступний: вміст сегментного регістра зрушується на 4 біта вліво. До вмісту зміщення привласнюється 4 нулі ліворуч.

Сегмент зміщення

При підсумовуванні може виникати перенесення з розряду A19 в A20. Це перенесення ігнорується. Аналогічну кільцеву організацію має кожен сегмент. При вибірці команда: CS +IP = ФА команди. При зверненні до стека: SS +SP =ФА стека.

Звернення до даних може вироблятися з будь-якого сегментного регістра: DS (SS, CS, ES) +EA = ФА даних. EA - ефективна адреса, константа, вказана в програмі.

До даних можна звернутися через індексні регістри SI і DI; причому індексний регістр зберігає зміщення на адресу елементи пам'яті, звідки дані можна витягнути. А DI зберігає зміщення на адресу осередку пам'яті, куди дані можна направити: DS(SS, CS, ES) +SI=ФА даних; ES+DI =ФА даних. Звернення через регістр BX : ES(CS, SS, DS)+BX= ФА даних. Така модульна організація пам'яті посегментний дозволяє писати програми у вигляді окремих модулів.

Питання:

Яка архітектура МП?

Розкажіть про сегментні регістри?

Література:

А.В. Белов Создаем устройства на микроконтроллерах Год: 2007

Гусев В.Г., Гусев Ю.М. Электроника