- •Лекція №1 Основні положення задачі курсу

- •Лекція №2 Характеристика напівпровідників

- •Приєднання кристала до основи корпусу

- •Лекція №8 Гібридні інтегральні мікросхеми План

- •Загальні вимоги до логічних імс

- •Десятична система числення

- •Двійкова система численя

- •Література: с.В. Симонович и др. Информатика. Базовый курс. – сПб: Питер, 2005 – 640 с.

- •Відправлення сигналів

- •Обробка сигналів

- •Лекція №20 Дослідження роботи регістрів План

- •Призначення виводів

- •Лекція №17

- •Лекція №23 Взаємодія вузлів пеом-80

- •Література:

- •Лекція №24 Характеристика вузлів пеом-80

- •Література:

- •Загальна лекція

- •2. Однопрограмний і мультипрограмний режими керування

- •3. Сторінкова організація пам’яті

- •4. Використання віртуальної пам’яті в ос Windows та ос Unix

- •Лекція №25 Характеристика мікропроцесора к1810вм86

Призначення виводів

Висновок |

Позначення |

Тип виводу |

Призначення |

1 |

RESET |

Вихід |

Установка в початковий стан ("Скидання") мікропроцесора і системи |

2 |

RESIN# |

Вхід |

Вхід для генерації сигналу "Скидання" |

3 |

RDYIN |

Вхід |

Сигнал "Готовність" |

4 |

RDY |

Вихід |

Сигнал "Готовність" |

5 |

SYN |

Вхід |

Сигнал синхронізації |

6 |

C |

Вихід |

Тактовий сигнал, синхронний з фазою С2 |

7 |

STB# |

Вихід |

Стробуючий сигнал стану |

8 |

GND |

- |

Загальний |

9 |

Ucc2 |

- |

Напруга живлення +12 В |

10 |

С2 |

Вихід |

Тактові сигнали фаза С2 (+12 В) |

11 |

С1 |

Вихід |

Тактові сигнали фаза С1 (+12 В) |

12 |

OSC |

Вихід |

Тактові сигнали опорної частоти (ТТЛ) |

13 |

TANK |

- |

Висновок для підключення коливального контура |

14, 15 |

X1, X2 |

- |

Висновки для підключення резонатора |

16 |

Ucc1 |

- |

Напруга живлення +5 В |

Питання:

Що таке генератор КР580ГФ2?

Як генератор тактових сигналів працює?

Дайте характеристику виводів генератора?

Література:

Гусев В.Г., Гусев Ю.М. Электроника М: Высшая школа, 1991 г.

Лекція №13(ср)

Дослідження генератора тактових сигналів

План

Генератор сигналів

Тактові генератори

Схема тактового генератора

Генератор сигналів - цей пристрій, що дозволяє отримувати сигнал певної природи (електричний, акустичний або інший), що має задані характеристики (форму, енергетичні або статистичні характеристики і т. д.). Генератори широко використовуються для перетворення сигналів, для вимірів і в інших областях. Складається з джерела (пристрої з самозбудженням, наприклад підсилювача охопленого ланцюгом позитивного зворотного зв'язку) і формувача (наприклад, електричного фільтру)

Тактові генератори

У багатьох цифрових схемах все залежить від порядку, у якому виконуються дії. Іноді одна дія повинне передує іншій, іноді дві дії повинні відбуватися одночасно. Для контролю часових відносин у цифрові схеми вбудовуються тактові генератори, щоб забезпечити синхронизацію.

Тактовий генератор - це схема, що викликає серію імпульсів. Всі імпульси однакові по тривалості. Інтервали між послідовними імпульсами також однакові. Часовий інтервал між початком одного імпульсу та початком наступного називається часом такту. Частота імпульсів звичайно від 1 до 500 МГЦ.

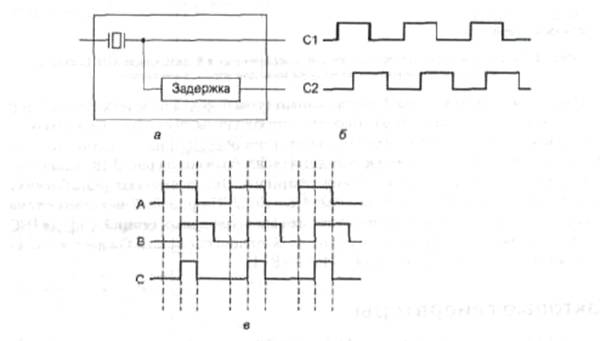

Частота тактового генератора звичайно контролюється кварцовим генератором, щоб досягти високої точності. У комп'ютері за час одного такту може відбутися багато подій. Якщо вони повинні здійснюватися в певному порядку, то такт варто розділити на підтакти. Щоб досягти кращого дозволу, ніж в основного тактового генератора, потрібно зробити відгалуження від лінії, що задає, тактового генератора й встановити схему з певним часом затримки. Таким чином виробляється вторинний сигнал тактового генератора, що зрушений по фазі щодо первинного (Рис. 1, а). Часова діаграма (Рис. 1, б ) забезпечує чотири початки відліку часу для дискретних подій:

1. Наростаючий фронт С1.

2. Задній фронт С1.

3. Наростаючий фронт С2.

4. Задній фронт С2.

Зв'язавши різні події з різними фронтами, можна досягти необхідної послідовності виконання дій. Якщо в межах одного такту необхідно більше чотирьох початків відліку, можна зробити ще кілька відгалужень від задаючої лінії, з різним часом затримки.

Рис. 1. Тактовий генератор (а); тимчасова діаграма для тактового генератора (б);

породження асинхронних тактових імпульсів (е)

У деяких схемах важливі тимчасові інтервали, а не дискретні моменти

часу. Наприклад, деяка подія може відбуватися в будь-який час, коли рівень імпульсу С1 високий, а не на наростаючому фронті. Інша подія може відбуватися тільки в тому випадку, коли рівень імпульсу С2 високий.

Якщо необхідно більше двох інтервалів, потрібно забезпечити більше ліній що передають синхронізуючі імпульси або зробити так, щоб стани з високим рівнем імпульсу у двох тактових генераторів частково перетиналися в часі. В останньому випадку можна виділити 4 окремих інтервали: С1 І С2, С1 І С2, С1 І С2 та С1 І С2.

Тактові генератори можуть бути синхронними. У цьому випадку час стану звисоким рівнем імпульсу дорівнює часу стану з низьким рівнем імпульсу (рим .6,б). Щоб одержати асинхронну серію імпульсів, потрібно зрушити сигнал генератора, що задає, використовуючи ланцюг затримки. Потім потрібно з'єднати отриманий сигнал з початковим сигналом за допомогою логічної функції І (див.Рис. 1, в, сигнал С).

Питання:

Дайте визначення поняттю генератор сигналів?

Дайте визначення поняттю генератору тактових сигналів?

Намалюйте схему тактового генератора?

Література:

Гусев В.Г., Гусев Ю.М. Электроника М: Высшая школа, 1991 г.

Лекція №14(ср)

Програмований парралельный та послідовний інтерфейс

План

Програмований парралельный інтерфейс

Програмований послідовний інтерфейс

Програмований парралельный інтерфейс

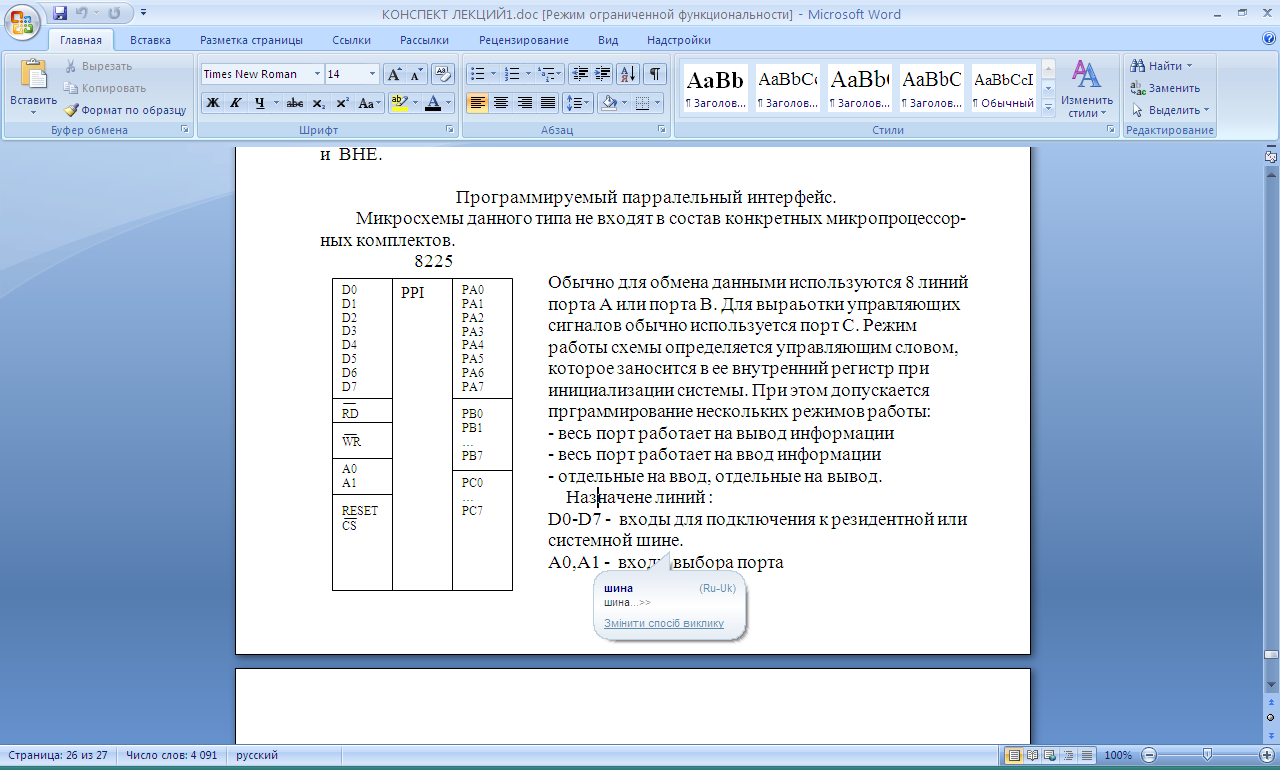

Мікросхеми цього типу не входять до складу конкретних микропроцессорных комплектів.

Зазвичай для обміну даними використовуються 8 ліній порту А або порту B. Для выраьотки сигналів, що управляють, зазвичай використовується порт С. Режим роботи схеми визначається словом, що управляє, яке заноситься в її внутрішній регістр при ініціалізації системи. При цьому допускається прграммирование декількох режимів роботи :

увесь порт працює на виведення інформації

увесь порт працює на введення інформації

окремі на введення, окремі на вивід.

Призначення ліній :

D0 - D7 - входи для підключення до резидентної або системної шини.

A0, A1 - входи вибору порту

Так як архітектура центрального процесора 16-ти розрядна, а мікросхема порту 8-ми розрядна можливі 2 варіанти підключення цієї мікросхеми. При передачі 8-ми розрядних даних інтерфейс підключається до молодшого байта шини даних, а центральний процесор програмується на виведення цього байта. Для передачі усього слова треба використовувати 2 контроллери.

Програмований послідовний інтерфейс.

Послідовний обмін даних регламентується в стандарті RS232C. Цей стандарт передбачає для передачі інформації 3 лінії зв'язку : загальна, лінія передачі (ВА) і лінія прийому (ВВ). Протокол обміну даними має наступний формат:

Функціонально послідовний інтерфейс реалізується на 2-х зрушуючих регістрах:

Послідовний інтерфейс може працювати в синхронному і асинхронному режимі. Синхронний режим має на увазі роботу інтерфейсу приймача і передавача під управлінням системного генератора.

Питання:

Який принцип роботи програмованого парралельного інтерфейсу?

Який принцип роботи програмованого послідовного інтерфейсу?

Електроний ресурс:

http://www.studfiles.ru/dir/cat32/subj1245/file11267/view113893.html

Лекція №15

Програмований паралельний інтерфейс КР580ВВ55(ср)

План

Мікросхема КР580ВВ55

Призначення виводів мікросхеми КР580ВВ55

Зчитування інформації з каналу інтерфейсу

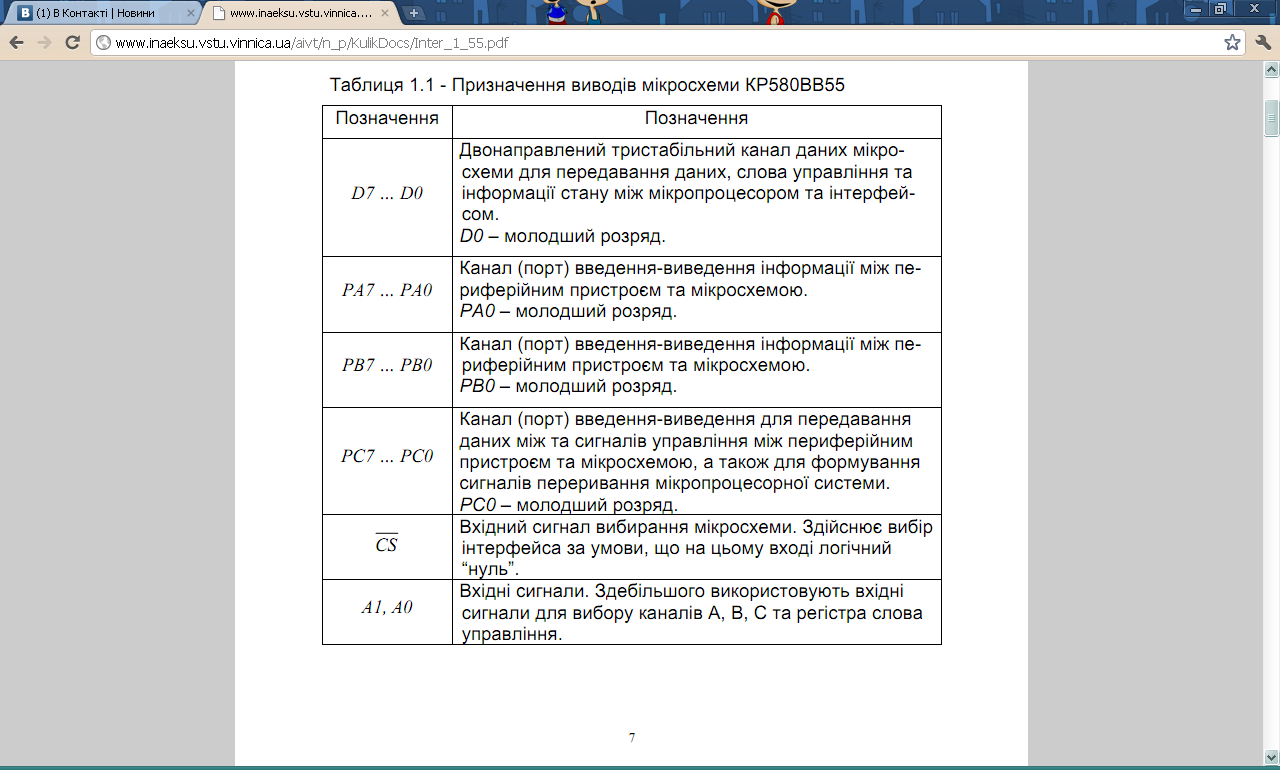

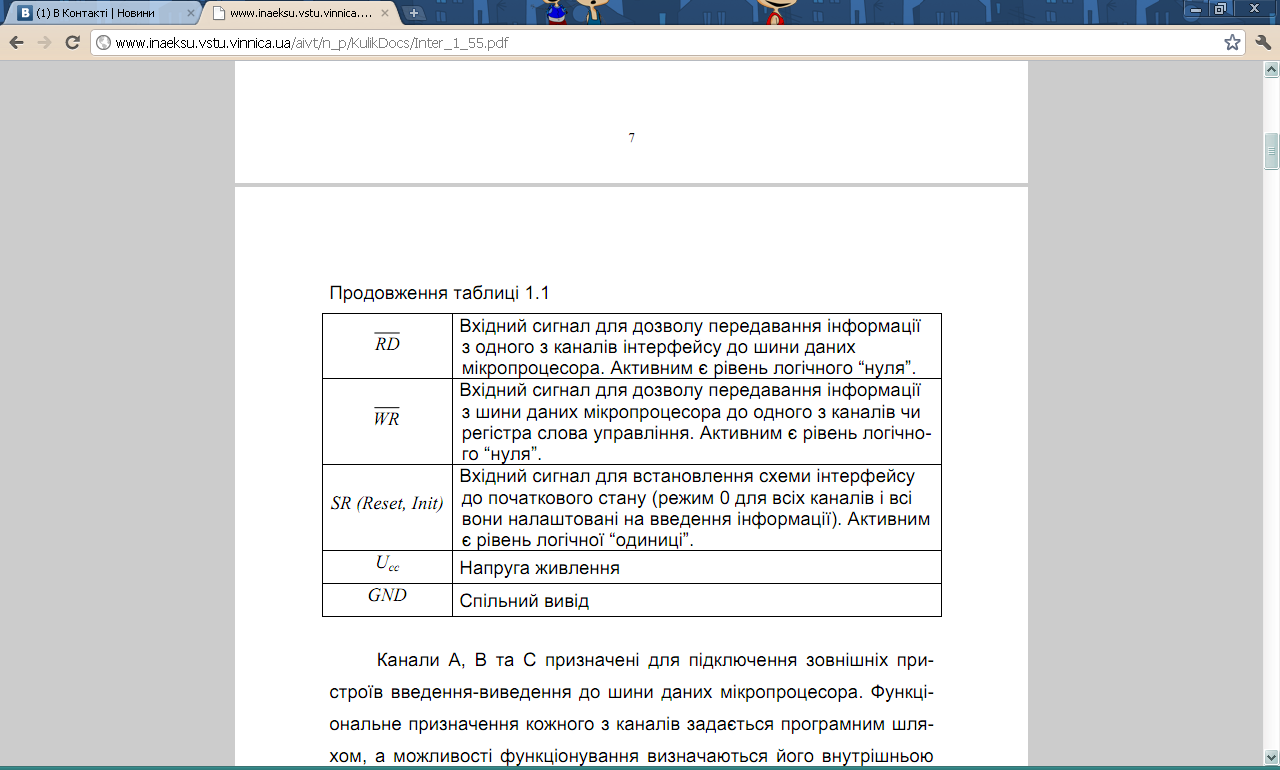

Мікросхема КР580ВВ55 являє собою однокристальний програ-мований пристрій введення-виведення паралельної інформації у рі-зних режимах і призначена для засобів оброблювання інформації увипадку реалізації зв’язку периферійних пристроїв із мікропроцесор-ною системою. Призначення виводів

мікросхеми наведене у таблиці1.1 [1 - 5].

Канали А, В та С призначені для підключення зовнішніх при-строїв введення-виведення до шини даних мікропроцесора. Функці-ональне призначення кожного з каналів задається програмним шля-хом, а можливості функціонування визначаються його внутрішньоюструктурою. Для програмування режиму роботи каналів потрібно:

здійснити скидання мікросхеми;

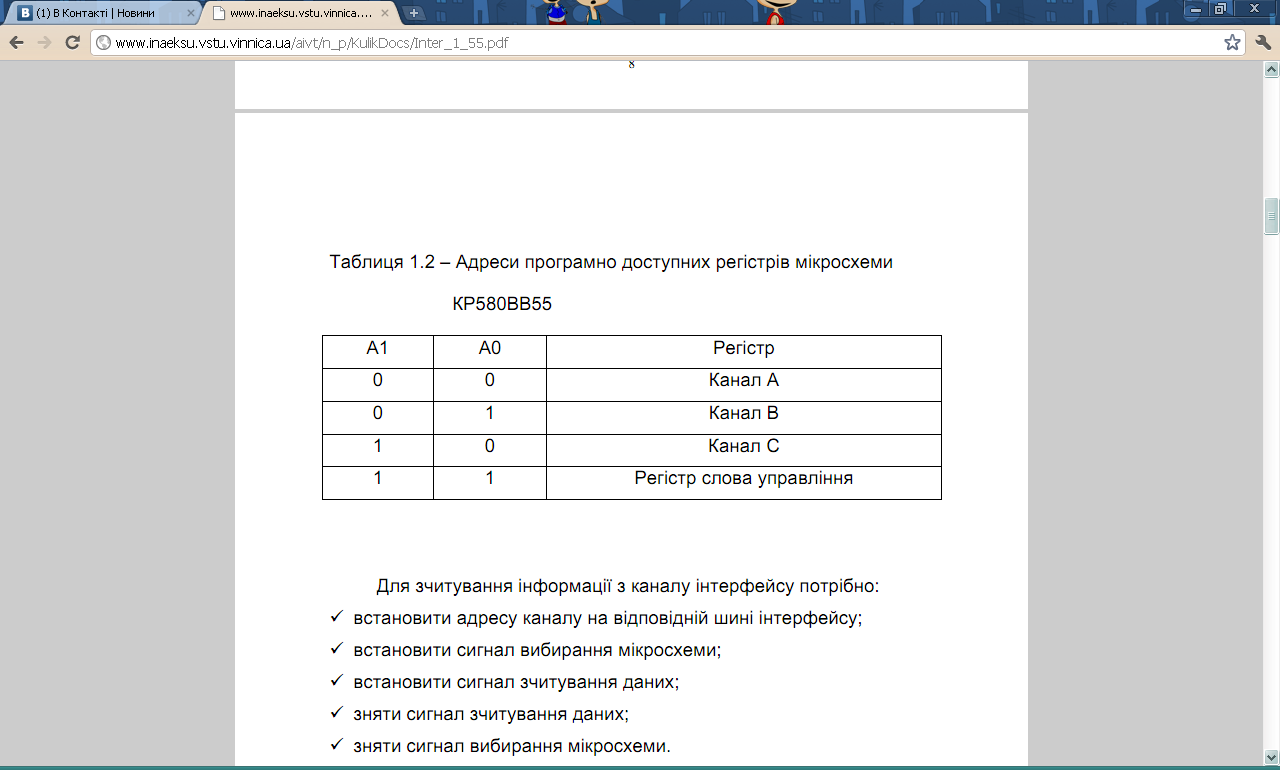

встановити на шину адреси мікросхеми адресу регістра словауправління у відповідності із таблицею 1.2;

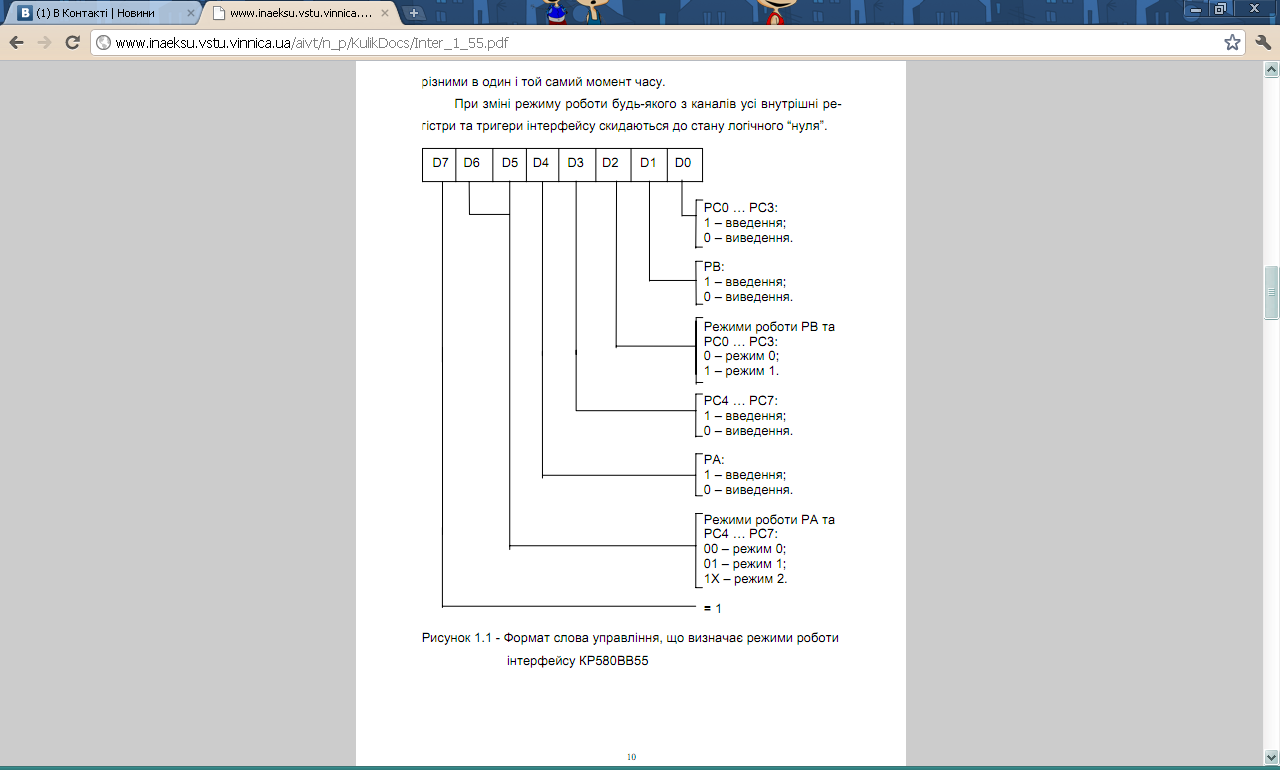

встановити на шині даних слово управління у відповідності із ри-сунком 1.1;

перевести до активного стану сигнал вибирання мікросхеми;

перевести до активного стану сигнал записування інформації;

зняти сигнал запису інформації;

зняти сигнал вибирання мікросхеми.

Для зчитування інформації з каналу інтерфейсу потрібно:

встановити адресу каналу на відповідній шині інтерфейсу;

встановити сигнал вибирання мікросхеми;

встановити сигнал зчитування даних;

зняти сигнал зчитування даних;

зняти сигнал вибирання мікросхеми.

Режим роботи кожного каналу визначається вмістом регістраслова управління. Здійснюючи записування слова управління до ре-гістра, можна перевести інтерфейс до одного з трьох основних ре-жимів роботи:

♦ режим 0 – просте введення-виведення інформації;

♦ режим 1 – стробоване введення-виведення інформації;

♦ режим 2 – двонаправлений канал.

Режими

роботи

каналів

можна

змінювати

як

на

початку,

так

іпід

час

виконання

системою

програми,

що

дозволяє

обслуговуватирізні

периферійні

пристрої

у

певному

порядку

однією

мікросхемоюКР580ВВ55.

Режими роботи

каналів А та В можуть бути встановлені9різними

в один і той самий момент часу. При зміні

режиму роботи будь-якого з каналів усі

внутрішні ре-гістри та тригери інтерфейсу

скидаються до стану логічного “нуля”.

Комбінуючи

режими роботи каналів, можна забезпечити

мож-ливість роботи інтерфейсу практично

з будь-яким периферійнимпристроєм, який

працює у паралельному коді. Будь-який

з восьми розрядів регістра каналу С

може бути про-грамним шляхом встановлений

до стану логічної “одиниці” чи скину-тий

до стану логічного “нуля”. Для цього

потрібно здійснити запису-вання слова

управління, формат якого поданий на

рисунку. 1.2. Якщо інтерфейс запрограмований

на режим роботи 1 чи 2, токаналом С

формуються сигнали, які можуть

використовуватися у ви-гляді сигналів

запиту переривання роботи мікропроцесорної

систе-ми. Заборонити чи дозволити

формування цих сигналів можна

вста-новленням (скиданням) відповідних

розрядів у регістрі каналу С. Цяособливість

інтерфейсу дозволяє мікропроцесору

заборонити чи до-зволити обслуговування

будь-якого зовнішнього пристрою без

ана-лізу запиту переривання у схемі

переривання.

Комбінуючи

режими роботи каналів, можна забезпечити

мож-ливість роботи інтерфейсу практично

з будь-яким периферійнимпристроєм, який

працює у паралельному коді. Будь-який

з восьми розрядів регістра каналу С

може бути про-грамним шляхом встановлений

до стану логічної “одиниці” чи скину-тий

до стану логічного “нуля”. Для цього

потрібно здійснити запису-вання слова

управління, формат якого поданий на

рисунку. 1.2. Якщо інтерфейс запрограмований

на режим роботи 1 чи 2, токаналом С

формуються сигнали, які можуть

використовуватися у ви-гляді сигналів

запиту переривання роботи мікропроцесорної

систе-ми. Заборонити чи дозволити

формування цих сигналів можна

вста-новленням (скиданням) відповідних

розрядів у регістрі каналу С. Цяособливість

інтерфейсу дозволяє мікропроцесору

заборонити чи до-зволити обслуговування

будь-якого зовнішнього пристрою без

ана-лізу запиту переривання у схемі

переривання.

Питання:

1. Яке функціональне призначення мікросхеми КР580ВВ55?

2. У яких режимах можуть працювати канали інтерфейса? Як їх можна комбінувати?

3. Яким чином здійснюється безпосореднє встановлення розрядів каналу С?

Електроний ресурс:

http://www.inaeksu.vstu.vinnica.ua/aivt/n_p/KulikDocs/Inter_1_55.pdf

Лекція № 16

Програмований контролер переривань КР580ВН59(ср)

План

Призначення програмованого контролера переривань КР580ВН59

Технічні характеристики

Умовне графічне позначення і призначення виводів

Функціональна схема і принцип роботи

Настройка контролера по алгоритму

Схема каскадування

Висновки

Тези лекції:

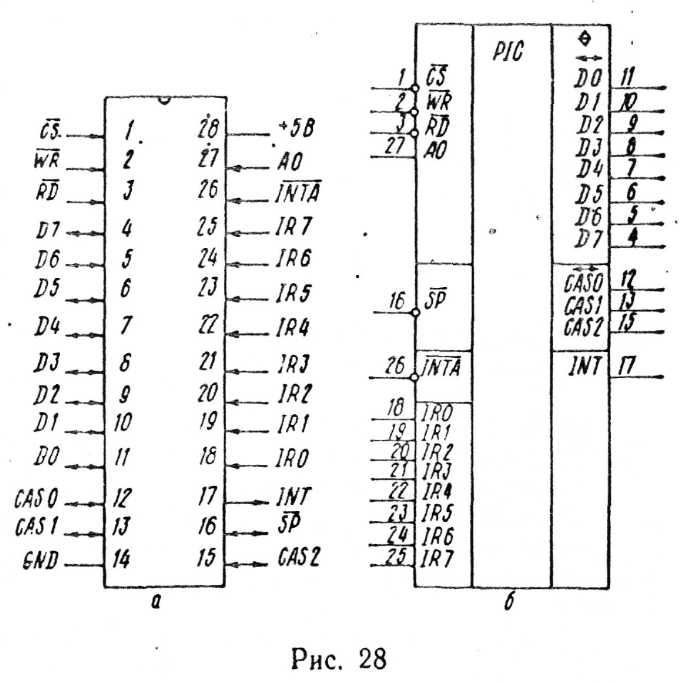

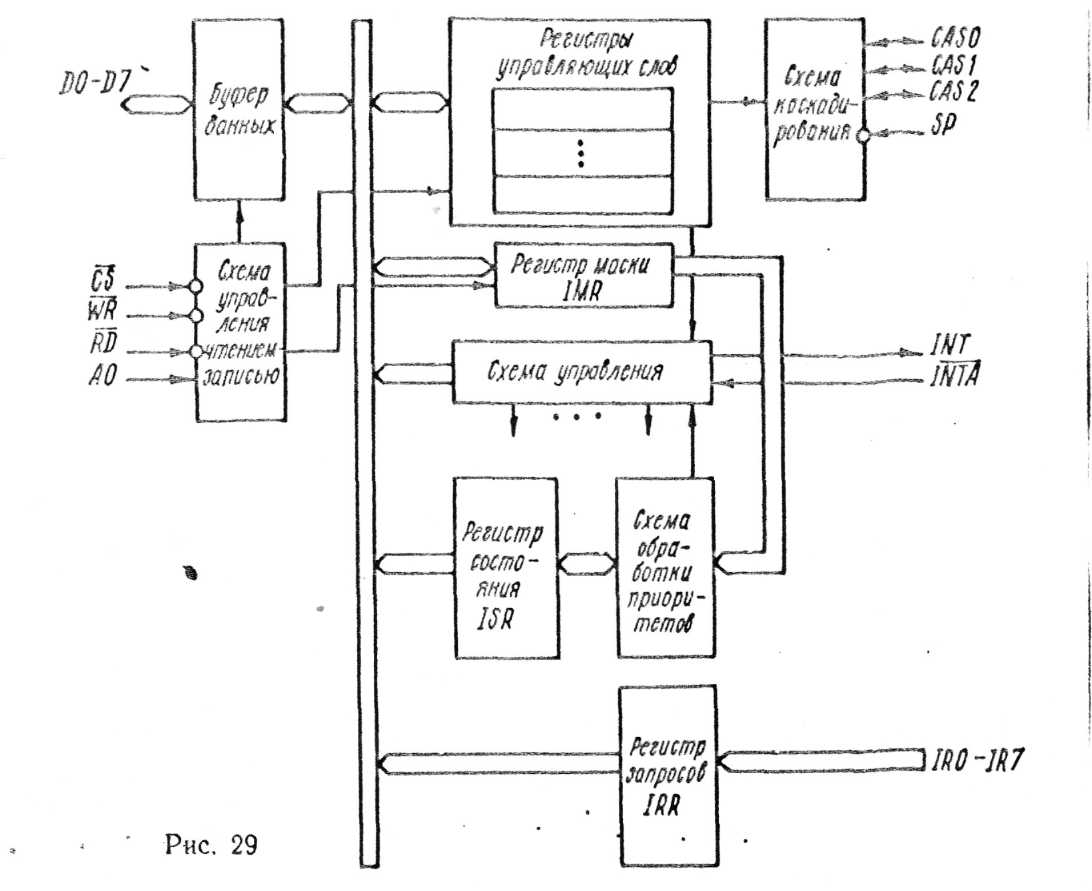

Програмувальний контролер переривань реалізує векторну восьмирівневу систему переривань. контролер виконує наступні функції: 1) фіксацію запитів на переривання від 8 зовнішніх джерел; 2) програмне маскування запитів, що надходять; 3) присвоєння фіксованих або циклічно змінюваних пріоритетів входам контролера, на які надходять запити; 4) формування коду операції команди call (перехід на підпрограму обробки переривання) і 16-розрядної адреси цієї підпрограми; 5) послідовне опитування зовнішніх пристроїв для визначення, чи бідує пристрій в обміні. кількість зовнішніх джерел, що обслуговуються, може бути збільшене до 64 каскадуванням контролерів (один - ведений, вісім - ведучих).

технічні характеристики

технологія п-моп

кількість виводів 28

тип корпуса 2121.28

споживана потужність, вт < 1

навантажувальна здатність 1 вхід ттл схеми

напруга, в:

живлення +5 ± 5 %

вихідне низького рівня (iol=-2,2ма) <0,45

вихідне високого рівня (iон=400 мка) >2

вхідне низького рівня <0,8

вхідне високого рівня <2

діапазон робочих температур, °с -10…+70

маса, г <5

На

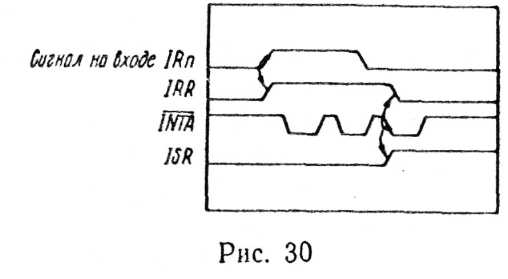

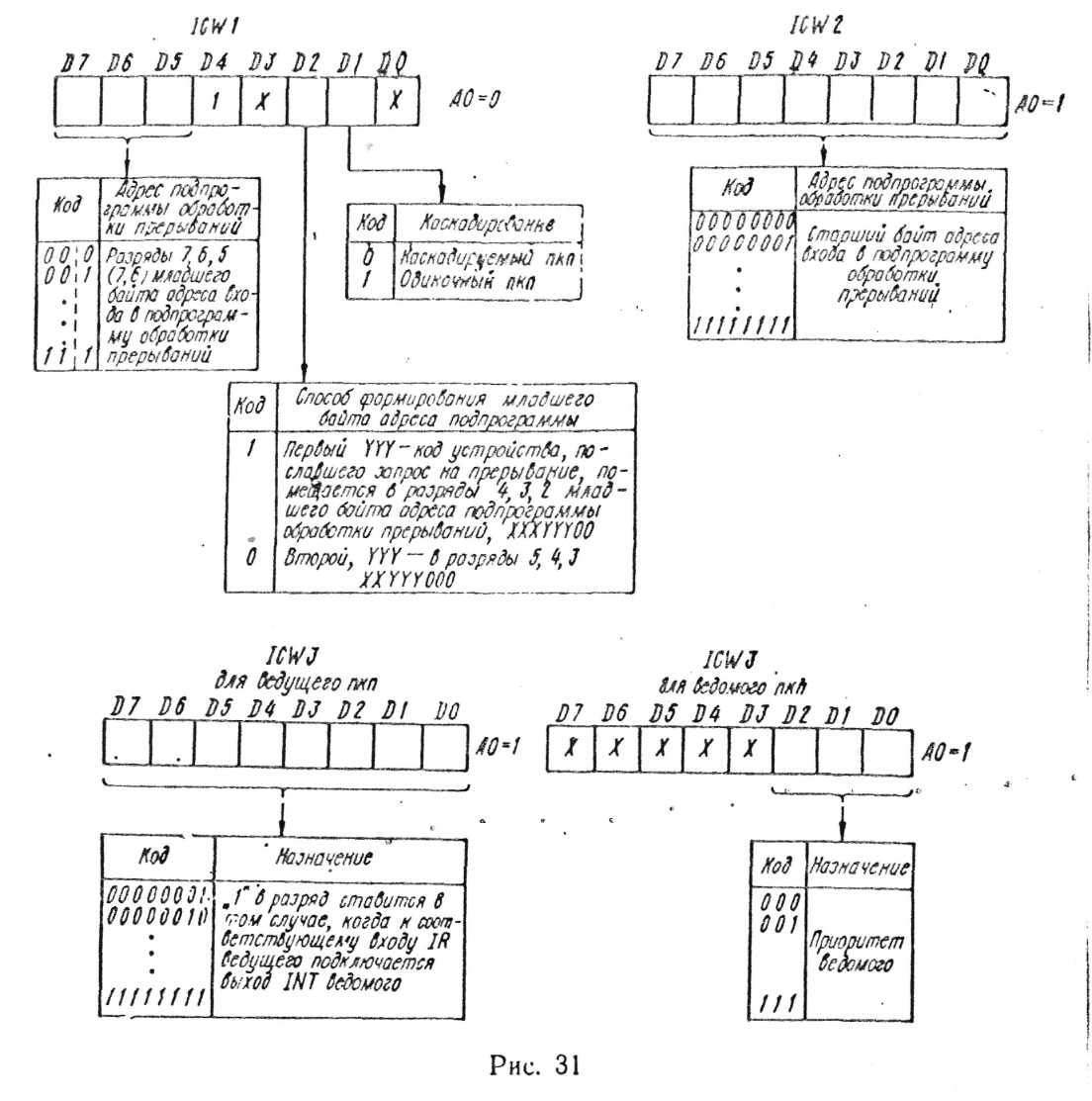

Схема керування ПКП формує сигнал запиту на переривання, що надходить на вхід INT мікропроцесора. Якщо мікропроцесору дозволене переривання, він відповідає контролеру сигналом, що надходить на вхід INTA. По цьому сигналі на шину даних видається перший байт команди CALL (11001101) — перехід на підпрограму обробки переривань. Вхідний до складу мікропроцесорних систем, системний контролер формує ще два сигнали, що надходять на вхід ПКП INTA, по яких видаються другий і третій байти команди CALL, що містять адресу підпрограми обробки перериванні. Крім того, по третьому сигналі, що надходить на вхід INТА контролера, скидається в «ОБ» розряд регістра запитів IRR (відповідний входу, по якому надійшов запит на переривання) і встановлюється в «1» відповідний розряд Таблиця 13

Старший байт адреси також записується в ПКП за допомогою команди OUT при настроюванні. Останньою командою підпрограми обробки переривань повинна бути OUT, За допомогою цієї команди в ПКП засилається операційне керуюче слово для закінчення режиму обслуговування переривання, у результаті чого скидається відповідний розряд регістра стану, що фіксує обслуговування запиту на переривання.

При обслуговуванні запиту, що надійшов на вхід одного з ведених ПКП, по першому сигналі на вході 1NTA, ведучий видає на шину даних перший байт команди CALL, а на входи CAS0 -CAS2 ведених - номер обслуговуваного веденого ПКП. Із приходом наступних

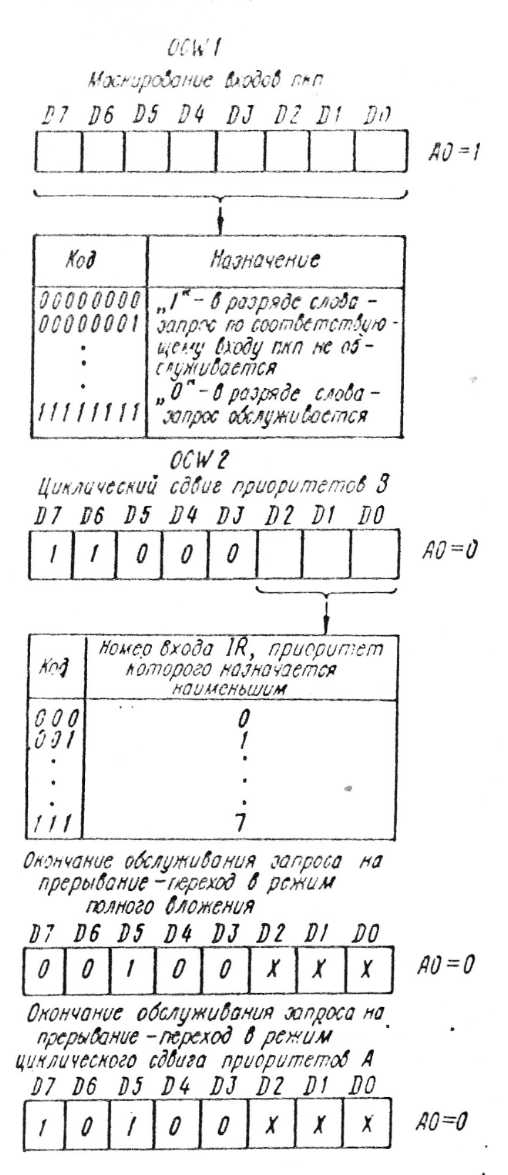

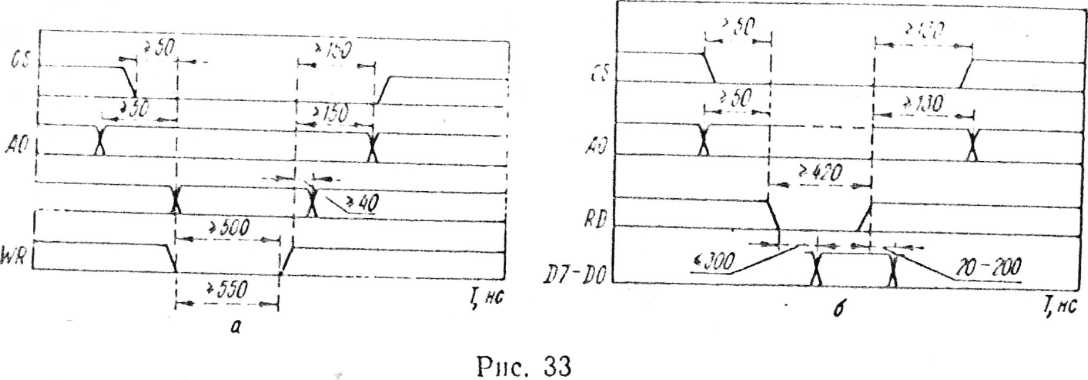

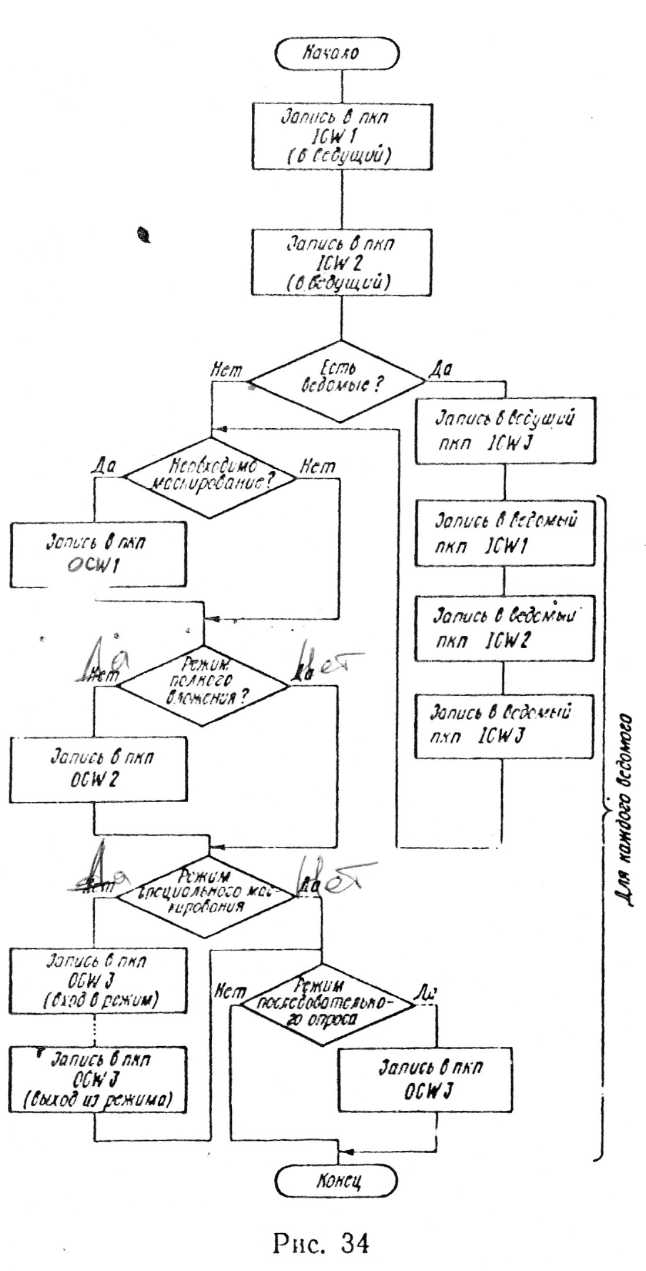

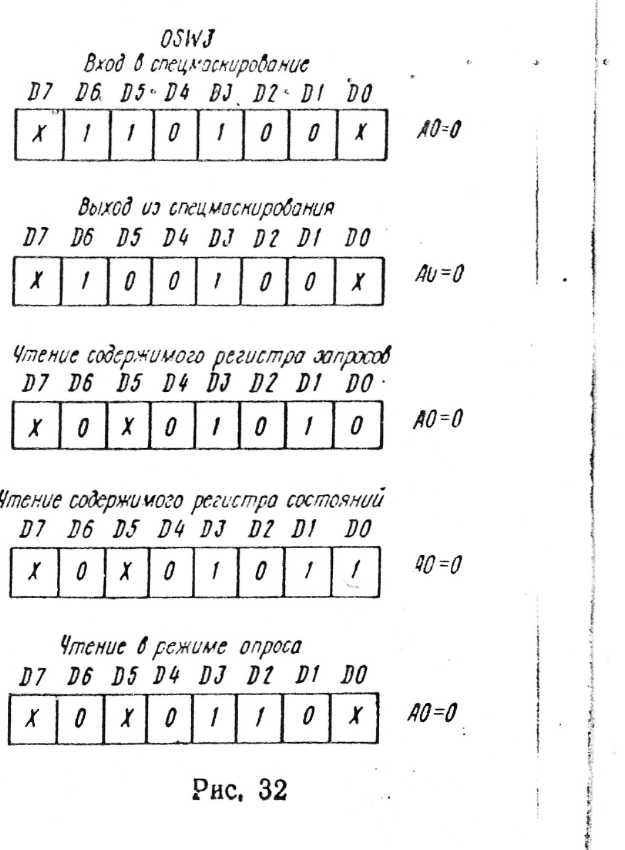

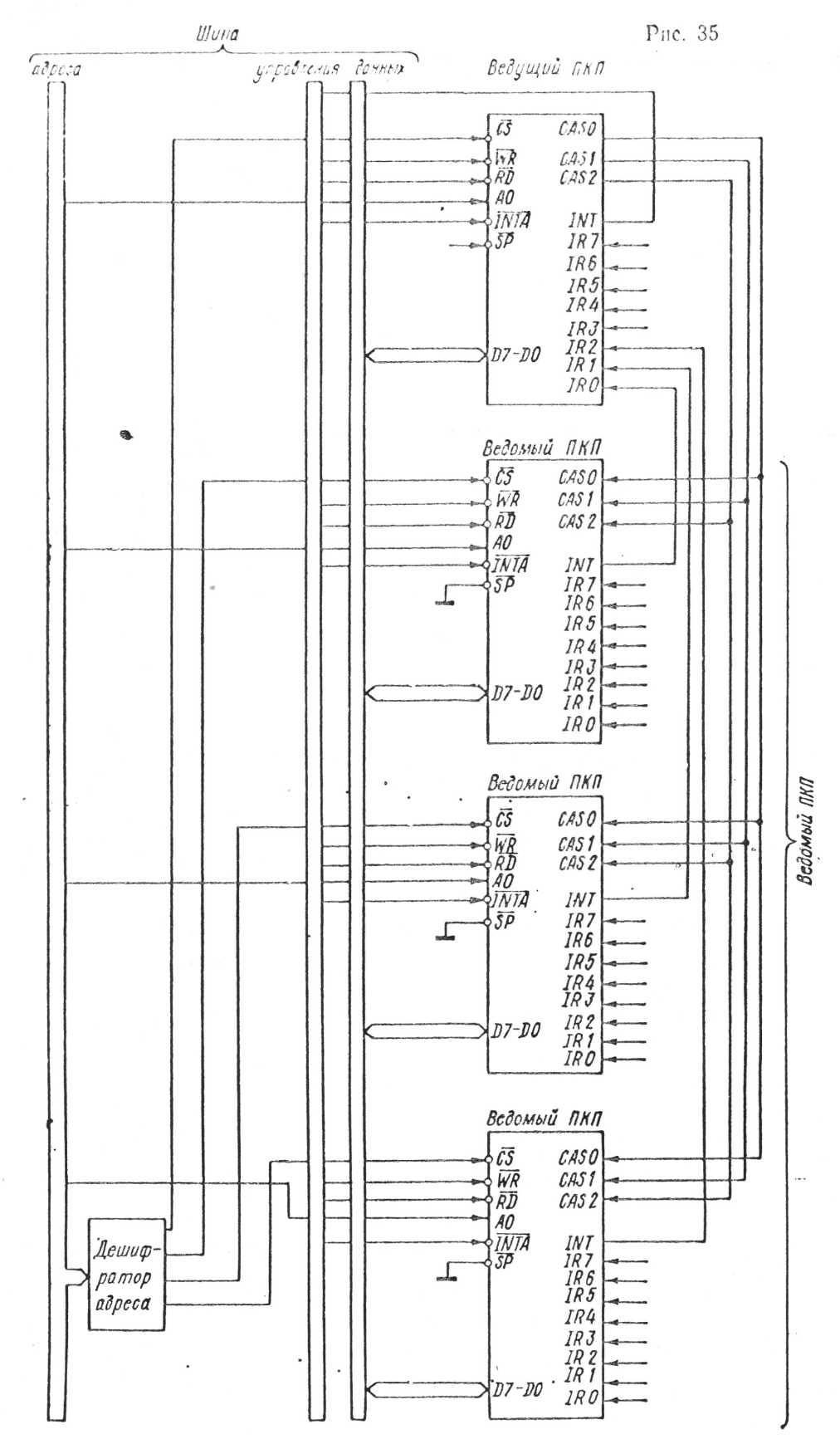

сигналів на вхід INTA ведений ПКП, номер якого збігся з номером на CAS0 -CAS2видає на шину даних послідовно 2 байти адреси підпрограми обробки переривань. У каскадованих системах по закінченні обслуговування підпрограми обробки переривань необхідно за допомогою команд OUT заслати два керуючі операційні слова: одне у ведучий ПКП, інше у ведений. Формати керуючих слів ініціалізації ICW1, ICW2, ICW3 і операційних керуючих слів OCW1, OCW2, OCW3 зображені на мал. 31 і 32. Тимчасові діаграми сигналів при записі керуючих слів у ПКП і читанні інформації із ПКП зображені на мал. 33 (а й б).

Режим повного вкладення підпрограм обробки переривань. У цьому режимі пріоритети входів ніколи не змінюються, вони встановлені в такий спосіб: IR0 має вищий пріоритет, a IR7 - нижчий. Якщо одночасно надходять запити на кілька входів ПКП, то обслуговується запит, що надійшов па вхід з найбільшим пріоритетом. якщо під час обслуговування по одному із входів надійде запит на вхід з більш високим пріоритетом, то пкп перерве обслуговування й перейде до підпрограми переривань, ініціалізованої новим запитом. запити, що надійшли по входах з більш низькими пріоритетами, не переривають поточного обслуговування. наприклад, є сигнали запитів на переривання на входах ir1 і ir4. ці сигнали встановлюють в «1» відповідні розряди регістра irr. коли на вхід inta приходить третій сигнал «підтвердження переривання», він скидає той розряд регістра запитів на переривання 1rr і встановлює той розряд регістра стану jsr, що відповідає запиту з найвищим пріоритетом.

таким чином, регістр стану відображає поточний стан системи переривання, тобто вказує на те, який із запитів обслуговується тепер. наприклад, якщо обслуговується запит, що надійшов на вхід ir4 (відповідний розряд регістра irr установлений в «1»), те запити, що надходять на входи ir5 -ir7, обслуговуватися не будуть. якщо надійде запит на шину з більше високим пріоритетом, наприклад ir1, то він запам'ятається у відповідному розряді регістра irr, а тому що цей вхід має більше високий пріоритет, то сформується сигнал запиту на переривання. у відповідь на цей сигнал від мікропроцесора надійдуть сигнали, що підтверджують переривання, і відповідний розряд регістра isr установиться в «1». при цьому він заборонить переривання по даному вході й входам з більше низькими пріоритетами. система перерве виконання підпрограми переривання по запиті на вході ir4 і перейде до підпрограми, що обслуговує переривання по запиті на вході 1r1. після виконання цієї підпрограми завантаженням ocw2 розряд 1 регістра стану скидається й триває виконання перерваної підпрограми переривання.

циклічне зрушення пріоритетів. режим а. на відміну від попереднього режиму пріоритети можуть бути динамічно змінені. входу, запит на переривання по якому був тільки що обслужений, завантаженням керованого слова ocw2 привласнюється нижчий пріоритет. розподіл входів у порядку зростання пріоритетів ліворуч праворуч

ir7 ir6 ir5 ir4 1r3 1r2 ir1 ir0

після першого обслуговування ir2 ir1 iro ir7 ir6 ir5 1r4 ir3

після другого обслуговування ir5 ir4 ir3 ir2 ir1 iro ir7 ir6

примітка. знак * позначає запит на переривання.

режим зрушення пріоритетів а не є постійним подібного до режиму повного вкладення. для виконання кожного зрушення пріоритетів необхідно завантажувати керуюче слово ocw2 (закінчення обслуговування запиту на переривання — перехід у режим циклічного зрушення пріоритетів а) у пкп послу завершення виконання кожної підпрограми обробки переривань. режим циклічного зрушення пріоритетів дозволяє позбутися від недоліку, що полягає в тім, що при частих запитах на переривання по i входах з вищими пріоритетами запити по входах з нижчими пріоритетами можуть не обслуговуватися. застосування цього режиму доцільно й у випадку обслуговування пристроїв з однаковими пріоритетами.

Для того щоб перейти в режим циклічного зрушення пріоритетів А зі скиданням відповідного розряду регістра стану, необхідно але адресі з А0 = 0 за допомогою команди OUT записати в ПКП операційне керуюче слово OCW2:

MVI А, 0А0Н; OCW2=10100000 i OUT PICUL; A0 = 0

Циклічне зрушення пріоритетів. Режим В. У режимі В користувач може програмно управляти призначенням входу з нижчим пріоритетом.

Приклад. Входу IR5 може бути привласнений нижчий пріоритет.

Старий розподіл пріоритетів IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0

Новий розподіл пріоритетів IR5 IR4 IR3 IR2 IR1 IRO IR7 IR6

Пріоритети в режимі В можуть бути змінені в будь-який момент часу за допомогою команди OUT, що посилає в ПКП керуючі операційні слова OCW2 (циклічне зрушення пріоритетів В, спеціальне закінчення обслуговування запиту на переривання — перехід у режим циклічного зрушення пріоритетів В).

Для того щоб перейти в режим циклічного зрушення пріоритетів У без скидання відповідних розрядів регістра стану ISR, необхідно виконати наступне:

MVI А, ОС5Н; OCW2 = 11000101; 5 - номер входу, якому буде привласнений найменший пріоритет

OUT PICUL; А0= 0

Для того щоб перейти в режим У зі скиданням відповідних розрядів, регістра стану, необхідно виконати наступне:

MVI А, ОЕ6Н; OCW2= 11100110; 6 - номер входу, якому буде привласнений найменший пріоритет

OUT PICUL; А0 = 0

Режим спеціального маскування. ПКП надає й іншу можливість маскування запитів на переривання - так званий режим спеціального маскування, службовець для того, щоб дозволити переривання по входах, що має більше низький пріоритет, чим у входу, запит по якому обслуговується в сучасний момент. У цьому режимі запити, що надходять на входи з більше низькими пріоритетами, обслуговуються доти, поки не відмінний режим спеціального маскування. Режим спеціального маскування призначається динамічно після початку обслуговування запиту. Для того щоб перейти в режим спеціального маскування, необхідно виконати наступні команди:

MVI А, 68Н; OCW3 = 01101000

OUT PICUL А0 = 0 !

Вийти з режиму спеціального маскування потрібно по командам

MVI Л, 48Н; OCW3 = 01001000

OUT PICUL; А0 = 0

Режим послідовного опитування. У цьому режимі мікропроцесор за допомогою ПКП опитує послідовно джерела запитів на обмін багаторазовим завантаженням керуючого слова OCW3 і читанням командою IN ПКП. Для того щоб перейти в режим послідовного опитування, необхідно за допомогою команди OUT послати в ПКП за адресою АТ - 0 операційне керуюче слово OCW3:

MVI А, 00001100В; OCW3 OUT PICUL; А0=0

Контролер виставляє на шину даних інформацію, що інтерпретується в такий спосіб: молодші розряди байта вказують номер зовнішнього пристрою з найвищим пріоритетом, одиниця в старшому розряді байта вказує на те, що є запит від цього Пристрою. Байт читається в мікропроцесор за допомогою команди IN:

IN PICUL; А0-0

Під час виконання опитування мікропроцесором повинні бути заборонені переривання. Обслуговування запиту на обмін полягає в програмному декодуванні інформації, одержуваної від ПКП, і виконанні відповідної програми, що реалізує обмін між мікропроцесором і обраним пристроєм. Настроювання каскаду, що складає з одного провідного й трьох ведених ПКП, (мал. 35) на режим з повним вкладенням підпрограм переривань і маскуванням 7-го й 5-го входів проілюструємо на прикладі. 1CW1 = 00010100

каскадування - 1-й спосіб подання адреси

настроювання провідного MVI Л. 14Н; ICW1 = 00010100

OUT PICUL; А0 = 0 MVI А, 40Н; 1CW2 = 01000000

OUT PICUH; А0= 1

MVI А, 07Н; 1CW3 = 00000111 - буде використовуватися три ведених OUT PICUH; А0 = I ;

настроювання 1-го веденого MVI А, I0N; ICWI = 00010000

OUT SPICUL; А0 = 0 MVI А, 48Н; ICW2 = 01001000

OUT SPICUH; А0 = 1 MVI А, 0; ICW3 = 00000000 - пріоритет

OUT SPICUH; А0 = 1

настроювання 2-го веденого

настроювання 3-го веденого

MVI А, ОАОН; маскування, маска =10100000

OUT P1CUN; А0 = 1

Вміст регістра запитів IRR і регістра стану IRS може бути прочитане шляхом завантаження в ПКП за допомогою команди OUT (Л0 = 0) операційного керуючого слова OCW3 з наступним виконанням команди IN (А0 = 0), наприклад:

MVI А, 00001010; OCW3

OUT PICUL ; А0 = 0

IN PICUL ; А0 = 0

Якщо після завантаження відповідного керуючого слова OCW3 інші керуючі слова не завантажувалися, то вміст регістрів можна багаторазово читати за допомогою команди IN. Зчитування вмісту регістра маски здійснюється за допомогою команди IN (АТ = 1) без завантаження OCW3. Необхідно ще раз підкреслити, що будь-яку підпрограму обробки переривань для роботи в системі із ПКП КР580ВН59 необхідно завершувати завантаженням операційного керуючого слова OCW2:

MVI А, 64Н; OCW2 = 01100100

OUT PICUL ; А0 = 0

RET

Питання:

Яке призначення програмованого контролера преривань KP580BH59?

Перерахувати технічні характеристики?

Надайте функціональну схему і принцип роботи.

Література: Товкес В.С., Шабаев В.Н., Мікропроцесорні системи(Частина I)

Товкес В.С., Шабаев В.Н., Мікропроцесорні системи (Частина II)