- •2. Архитектура вс параллельной обработки информации

- •2.1.Основные определения

- •2.2. Особенности архитектур эвм и вс прошедших поколений

- •2.3. Пути повышения производительности вычислительных средств и требования к вычислительным системам параллельной обработки информации

- •Перспективы и проблемы использования высокопроизводительных вс параллельной обработки информации

- •2.4. Способы параллельной обработки информации. Уровни обработки (гранулярность обработки)

- •2.5. Классификация вс с функциональной точки зрения

- •2.6. Проблемы неймановской архитектуры

- •2.7 . Особенности risс-архитектуры.

- •2.Х. Классификация вычислительных моделей и механизмов обработки

- •2.8. Вычислительные модели (системы) с управлением потоком данных (потоковые машины) и редукционные машины

- •2.9. Матричные (векторные) процессоры (simd-архитектуры)

- •2.10. Пример разрядно-модульного матричного процессора simd-архитектуры (параллельный процессор для обработки двухмерных изображений, передаваемых из космоса).

- •Разрядно-модульная матричная окмд

- •2.11. Особенности реализации мультимедийных алгоритмов на основе архитектур simd в современных простейших микропроцессорах

- •2.12. Процессоры со многими алу

- •2.13. Процессоры с конвейеризацией команд

- •2.14. Конвейерные операционные устройства обработки информации

- •2.15. Направления развития современных архитектур процессоров

- •2.16. Суперскалярные вычислительные системы

- •2.17. Микропроцессор Pentium 4.

- •2.18. Суперкомпьютер Gray

- •Секция регистров

- •2.19. Многопроцессорные системы.

- •Что это дает?

- •2.20. Разновидности ос многопроцессорных систем,

- •2.21. Мультипроцессорные системы на базе мп Alpha 21364

- •2.22. Однокристальные многопроцессорные системы

- •2.23. Векторно-конвейерные супер-эвм Cray c90, t90

- •2.24. Многопроцессорные вычислительные системы семейства мвс (мвс - 1000)

- •2.25. Многопроцессорная вычислительная система Эльбрус.

- •2.26. Многоядерные многопотоковые микропроцессоры

- •2.27. Кластерные системы.

- •2.28. Концепция grid-архитектур

- •2.29. Транспьютеры. Особенности архитектур мультитранспьютерных систем.

- •2.30. Транспьютерная многопроцессорная система для цифровой обработки сигналов. Транспьютерная многопроцессорная система цифровой обработки сигналов

- •2.31. Примеры формального представления сегментированных программ для параллельного исполнения.

- •2.32. Показатели производительности вычислительных систем.

2.8. Вычислительные модели (системы) с управлением потоком данных (потоковые машины) и редукционные машины

Особенностью потоковых машин является то, что последовательность вычислений задается не последовательностью команд, что характерно для неймановской архитектуры, а по мере готовности данных для выполнения команд. Данные загружаются в операционное устройство, если оно свободно, и для определенной команды имеются все необходимые данные.

Принципиальным отличием от неймановских машин является то, что команды выполняются не в порядке их следования, а по готовности операндов. Как только на входе операционного блока появляются данные, соответствующая команда блока захватывает эти данные и выполняется соответствующая операция. Машины, основанные на модели с потоком данных, называются потоковыми:

- отсутствие побочного эффекта;

- эффективная реализация параллельных вычислений.

Пример. a = (b+c)*(b-c). Для отображения хода процесса используются специальные «фишки». Потоковые принципы описываются с помощью графов и сетей Петри.

Такой подход используется в параллельных системах: однородных вычислительных средах (однотипные архитектуры процессоров (процессорных элементов ПЭ), настаиваемых на выполнение определенных программ; передача данных с использованием средств коммутации.

Рис.

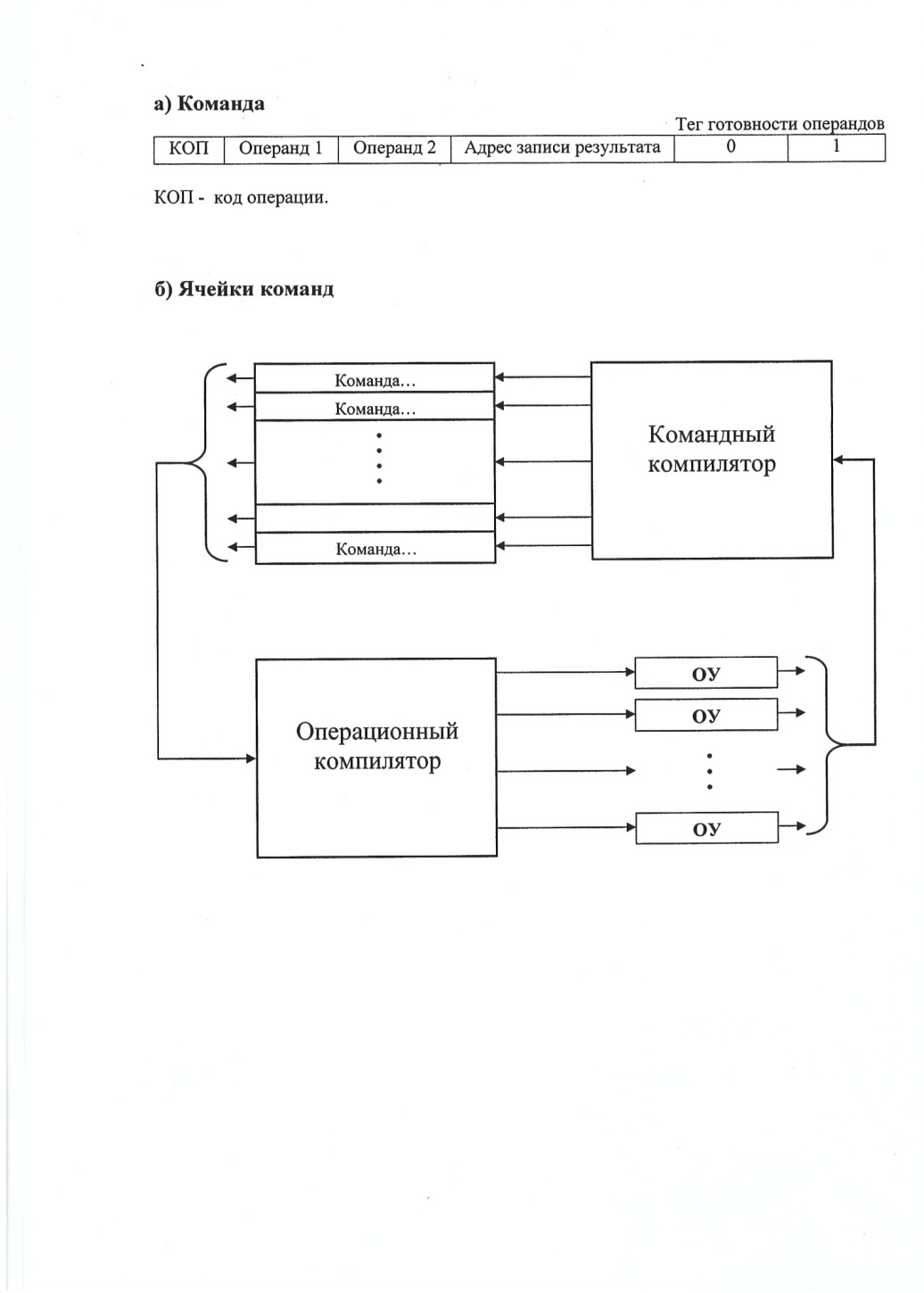

Принцип управления вычислительным процессом на основе потока данных используется в современных микропроцессорах, в частности, в суперскалярных архитектурах (Рис.). Сущность этих процессов состоит в следующем. Команда имеет код операции, может содержать два операнда, а также имеет два разряда (теги) для идентификации наличия (готовности) операндов к вычислениям. Команды хранятся в ячейках команд. Устройство управления при обнаружении двух единиц (двух готовых операндов) в одной из команд анализирует наличие среди операционных устройств (ОУ) свободное, которое по функциональным возможностям может реализовать операцию данной команды. При наличии такого устройства код операции и коды операндов передаются через операционный компилятор в соответствующее выбранное операционное устройство. Полученный результат записывается в память по адресу, указанному в команде.

Механизм редукционных машин основан на принципе редукции, т.е. сокращения посредством перезаписи строк символов (формул) в программе или сокращения в графах.

Запуск вычислений осуществляется при необходимости получения данных.

Пример. Исходные данные: граф программы, находящийся в памяти. a = (b+c)*(b-c).

В памяти:

а )

)

b )

)

c

)

d)

)

d)

Нет побочного эффекта. Реализуется последовательность решения математических выражений. Это направление удобно для параллельной реализации.

2.9. Матричные (векторные) процессоры (simd-архитектуры)

По классификации потоки команд - потоки данных эти архитектуры относятся к типу SIMD.

Можно выделить два основных направления:

матричный процессор с локальной памятью;

матричный процессор с общей памятью.

Матричный процессор с локальной памятью.

Имеется множество одинаковых процессорных элементов (как правило, они простые). На все процессоры одновременно поступает одна и та же команда или группа команд (SIMD). Каждый процессорный элемент использует данные из своей индивидуальной памяти (или оперативной памяти). Имеется возможность обмена данными или условиями перехода через сеть связи между процессорными элементами. Количество ПЭ – от 8-и до 16-и тысяч. Обычно ПЭ своих средств ввода-вывода не имеют.

П – память; ПЭ – процессорный элемент.

Матричный процессор с общей памятью.

МП – модуль памяти. ПЭ могут выполняться в виде отдельных процессоров, в значительной мере упрощенных; могут изготавливаться на пластине как множество ПЭ.

ПЭ-ты коммутируются сетью связи в соответствии с алгоритмом решения задачи. Каждый ПЭ настраивается на выполнение соответствующей одинаковой для всех команды или группы команд.

В современных многоядерных процессорах ПЭ являются в значительной мере высокофункциональными с развитой системой команд (например, процессоры для обработки графической информации).