- •Івано-Франківський національний технічний

- •Університет нафти і газу

- •Комп’ютерні системи

- •Конспект лекцій

- •Лекція № 1

- •1.1 Архітектура комп’ютерних систем

- •1.2 Паралельна обробка інформації

- •Контрольні запитання

- •Лекція №2 Основи теорії комп’ютерних систем

- •2.1 Класифікація комп’ютерних систем

- •Рисинук 2.2 - Класи комп’ютерних систем

- •2.2 Паралельні алгоритми

- •2.3 Характеристика типових схем комунікації в багатопроцесорних комп’ютерних системах

- •2.4 Закон Амдала

- •Контрольні запитання

- •Лекція №3 Конвеєрні комп’ютерні системи

- •3.1 Обробка інформації векторним процесором

- •3.2 Процесор з паралельним алп

- •3.3 Структура векторного процесора

- •3.4 Векторно-конвеєрні комп’ютерні системи

- •Контрольні запитання

- •Лекція №4 Матричні комп’ютерні системи

- •4.1 Матричний процесор

- •4.2 Матрична комп’ютерна система

- •If a (умова a) then do в

- •4.3 Архітектура матричних комп’ютерних систем

- •4.4 Структура процесорного елементу

- •4.5 Підключення і відключення процесорних елементів.

- •Контрольні запитання

- •Лекція № 5 Комп’ютерні системи класу simd

- •Контрольні запитання

- •Лекція № 6 Мультипроцесорні комп’ютерні системи

- •6.1 Загальна характеристика мультипроцесорних комп’ютерних систем

- •6.2 Мультипроцесори типу numa

- •6.3 Мультипроцесори типу coma

- •6.4 Мультипроцесорна комп’ютерна система Sun Enterprise 10000:

- •Контрольні запитання

- •Лекція №7 Мультикомп’ютерні комп’ютерні системи

- •7.1 Загальна характеристика мультикомп’ютерних комп’ютерних систем

- •Мультикомп’ютерна кс

- •7.2 Рівні комплексування у кс

- •7.3 Кластери

- •7.4 Топологія кластерних пар

- •7.5 Кластер Beowulf

- •7.6 Кластер ac3 Velocity Cluster

- •7.7 Кластер ncsa nt Supercluster

- •Контрольні запитання

- •Лекція № 8 Комп’ютерні системи з нетрадиційною архітектурою

- •8.1 Асоціативні кс

- •8.2 Систолічні кс

- •8.3 Класифікація структур систол

- •8.4 Кс з наддовгими командами (vliw)

- •8.5 Комп’ютерні системи з явним паралелізмом команд

- •8.6 Кс з обробкою за принципом хвильового фронту

- •8.7 Кс на базі трансп'ютерів і з неоднорідним доступом до пам'яті

- •Контрольні запитання

- •Лекція № 9 Організація пам’яті у комп’ютерних системах

- •9.1 Запам’ятовувальні пристрої комп'ютера

- •9.2 Системи із загальною і розподіленою пам'яттю

- •9.3 Багаторівнева організація загальної пам'яті

- •9.4 Пам'ять з чергуванням адрес

- •9.5 Асоціативна пам'ять

- •Контрольні запитання

- •Лекція № 10 Системи введення-виведення

- •10.1 Мережева базова система введення-виведення netbios

- •10.2 Пристрої для зберігання bios

- •10.3 Виробники bios

- •10.4 Принцип роботи bios

- •Контрольні запитання

- •Лекція № 11 Інтерфейси

- •Контрольні запитання

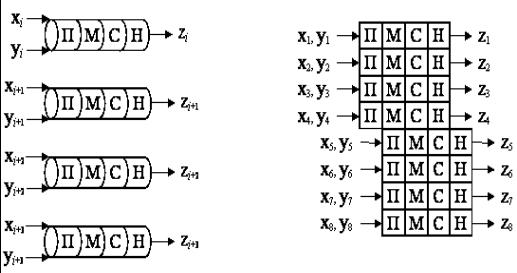

3.2 Процесор з паралельним алп

Якщо паралельно використовуються конвеєрні АЛП, то можливий ще один рівень конвеєризації. Обчислювальні системи, де реалізована ця ідея, називаються векторно-конвеєрними. Комерційні векторно-конвейєрні КС відомі як суперЕОМ (рис.3.3). Треба відмітити, що в склад даних систем для забезпечення універсальності включений також скалярний процесор

|

|

Рисунок 3.3 – Процесор з масивом паралельних арифметико-логічних пристроїв

3.3 Структура векторного процесора

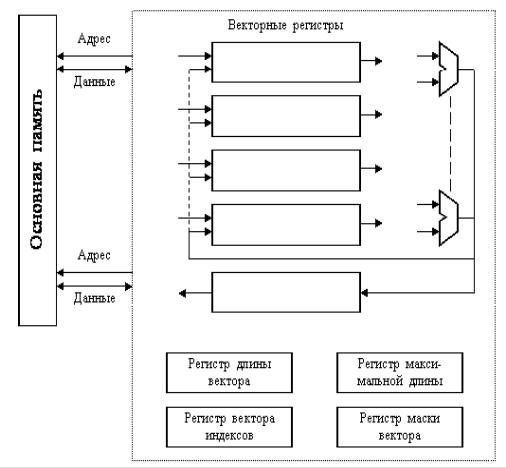

Узагальнена структура векторного процесора приведена на рис.3.4. На схемі показані основні вузли процесора, без деталізації деяких зв'язків між ними.

Особливості векторного процесора:

- обробка всіх n компонентів векторів-операндів задається однією векторною командою;

- елементи векторів представляються числами у формі з плаваючою комою;

- арифметико-логічний пристрій векторного процесора може бути реалізовано у вигляді:

- єдиного конвеєрного пристрою, здатного виконувати всі предбачені операції над числами з плаваючою комою;

- арифметико-логічний пристрій складається з окремих блоків складання і множення, а іноді і блоку для обчислення зворотної величини, коли операція ділення x/y реалізується у вигляді x(1/y). Кожний з таких блоків також конвеєризований.

Рисунок 3.4 – Узагальнена структура векторного процесора

Склад векторної системи:

- скалярный процесор, що дозволяє паралельно виконувати векторні і скалярні команди;

- векторні регістри для зберігання векторів-операндів, які є сукупністю скалярних регістрів, об'єднаних в чергу типу FIFO, здатну зберігати 50-100 чисел з плаваючою комою.

Набір векторних регістрів (Va, Vb, Vc...) є в будь-якому векторному процесорі. Система команд векторного процесора підтримує роботу з векторними регістрами і обов'язково включає команди:

- завантаження векторного регістра вмістом послідовних елементів пам'яті, вказаних адресою першої комірки цієї послідовності;

- виконання операцій над всіма елементами векторів, що знаходяться у векторних регістрах;

- збереження вмісту векторного регістра в послідовності комірок пам’яті, вказаних адресою першої комірки цієї послідовності;

- регістр довжини вектора. Цей регістр визначає, скільки елементів фактично містить оброблюваний в даний момент вектор, тобто скільки індивідуальних операцій з елементами потрібно зробити;

- регістр максимальної довжини вектора, що визначає максимальне число елементів вектора, яке може бути одночасно оброблене апаратурою процесора. Цей регістр використовується при розділенні дуже довгих векторів на сегменти, довжина яких відповідає максимальному числу елементів, що обробляються апаратурою за один прийом;

- регістр маски вектора служить для виконання таких операцій, в яких повинні брати участь не всі елементи векторів. У цьому регістрі кожному елементу вектора відповідає один біт. Установка біта в одиницю дозволяє запис відповідного елемента вектора результату у вихідний векторний регістр, а скидання в нуль - забороняє.

- регістр вектора індексів по структурі аналогічний регістру маски. Служить для виконання операцій упакування/розпаковування для отримання вектора, що містить ненульові елементи і для зворотної операції відповідно. У векторі індексів кожному елементу початкового вектора відповідає один біт. Нульове значення біта свідчить, що відповідний елемент вихідного вектора рівний нулю.

Переваги векторного процесора:

- замість багаторазового вибору одних і тих же команд досить здійснити вибір тільки однієї векторної команди, що дозволяє скоротити витрати за рахунок пристрою управління і зменшити вимоги до пропускної здатності пам'яті;

- векторна команда забезпечує процесор упорядкованими даними. Коли ініціюється векторна команда, КС знає, що їй потрібно вибрати n пар операндів, розташованих в пам'яті впорядкованим чином. Так, процесор може вказати пам'яті на необхідність почати вибір таких пар. Якщо використовується пам'ять з чергуванням адрес, ці пари можуть бути отримані із швидкістю однієї пари за цикл процесора і направлені для обробки в конвеєризованний функціональний блок. За відсутності чергування адрес або інших засобів вибору операндів з високою швидкістю переваги обробки векторів істотно знижуються.