- •Івано-Франківський національний технічний

- •Університет нафти і газу

- •Комп’ютерні системи

- •Конспект лекцій

- •Лекція № 1

- •1.1 Архітектура комп’ютерних систем

- •1.2 Паралельна обробка інформації

- •Контрольні запитання

- •Лекція №2 Основи теорії комп’ютерних систем

- •2.1 Класифікація комп’ютерних систем

- •Рисинук 2.2 - Класи комп’ютерних систем

- •2.2 Паралельні алгоритми

- •2.3 Характеристика типових схем комунікації в багатопроцесорних комп’ютерних системах

- •2.4 Закон Амдала

- •Контрольні запитання

- •Лекція №3 Конвеєрні комп’ютерні системи

- •3.1 Обробка інформації векторним процесором

- •3.2 Процесор з паралельним алп

- •3.3 Структура векторного процесора

- •3.4 Векторно-конвеєрні комп’ютерні системи

- •Контрольні запитання

- •Лекція №4 Матричні комп’ютерні системи

- •4.1 Матричний процесор

- •4.2 Матрична комп’ютерна система

- •If a (умова a) then do в

- •4.3 Архітектура матричних комп’ютерних систем

- •4.4 Структура процесорного елементу

- •4.5 Підключення і відключення процесорних елементів.

- •Контрольні запитання

- •Лекція № 5 Комп’ютерні системи класу simd

- •Контрольні запитання

- •Лекція № 6 Мультипроцесорні комп’ютерні системи

- •6.1 Загальна характеристика мультипроцесорних комп’ютерних систем

- •6.2 Мультипроцесори типу numa

- •6.3 Мультипроцесори типу coma

- •6.4 Мультипроцесорна комп’ютерна система Sun Enterprise 10000:

- •Контрольні запитання

- •Лекція №7 Мультикомп’ютерні комп’ютерні системи

- •7.1 Загальна характеристика мультикомп’ютерних комп’ютерних систем

- •Мультикомп’ютерна кс

- •7.2 Рівні комплексування у кс

- •7.3 Кластери

- •7.4 Топологія кластерних пар

- •7.5 Кластер Beowulf

- •7.6 Кластер ac3 Velocity Cluster

- •7.7 Кластер ncsa nt Supercluster

- •Контрольні запитання

- •Лекція № 8 Комп’ютерні системи з нетрадиційною архітектурою

- •8.1 Асоціативні кс

- •8.2 Систолічні кс

- •8.3 Класифікація структур систол

- •8.4 Кс з наддовгими командами (vliw)

- •8.5 Комп’ютерні системи з явним паралелізмом команд

- •8.6 Кс з обробкою за принципом хвильового фронту

- •8.7 Кс на базі трансп'ютерів і з неоднорідним доступом до пам'яті

- •Контрольні запитання

- •Лекція № 9 Організація пам’яті у комп’ютерних системах

- •9.1 Запам’ятовувальні пристрої комп'ютера

- •9.2 Системи із загальною і розподіленою пам'яттю

- •9.3 Багаторівнева організація загальної пам'яті

- •9.4 Пам'ять з чергуванням адрес

- •9.5 Асоціативна пам'ять

- •Контрольні запитання

- •Лекція № 10 Системи введення-виведення

- •10.1 Мережева базова система введення-виведення netbios

- •10.2 Пристрої для зберігання bios

- •10.3 Виробники bios

- •10.4 Принцип роботи bios

- •Контрольні запитання

- •Лекція № 11 Інтерфейси

- •Контрольні запитання

9.3 Багаторівнева організація загальної пам'яті

Сучасні комп'ютерні системи не монолітні, а складаються з ряду рівнів. Це дає можливість реалізувати загальну пам'ять на будь-якому з декількох рівнів:

- загальна пам'ять реалізована на апаратному забезпеченні (одна копія операційної системи з однією таблицею розподілу пам'яті. Для ОС пам'ять монолітна);

- загальна пам'ять реалізована на основі ОС і апаратного забезпечення (такий підхід називається DSM (Distributed Shared Memory - розподілена спільно використовувана пам'ять). Кожна машина містить свою власну віртуальну пам'ять і власні таблиці сторінок. По суті, операційна система просто викликає бракуючі сторінки не з диска, а з пам'яті. Але у користувача створюється враження, що машина містить загальну розділену пам'ять);

- реалізація загальної розділеної пам'яті на рівні програмного забезпечення (при такому підході абстракцію розділеної пам'яті створює мова програмування, і ця абстракція реалізується компілятором).

9.4 Пам'ять з чергуванням адрес

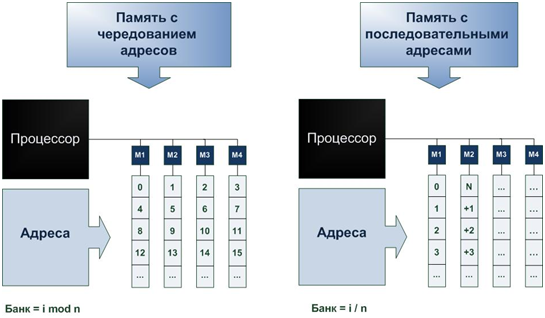

Фізично пам'ять комп’ютерної системи складається з декількох модулів (банків), при цьому істотним питанням є те, як в цьому випадку розподілений адресний простір (набір всіх адрес, які може сформувати процесор). Один із способів розподілу віртуальних адрес по модулях пам'яті полягає в розбитті адресного простору на послідовні блоки. Якщо пам'ять складається з n банків, то комірка з адресою i при поблочному розбитті знаходитиметься в банку з номером i/n. У системі пам'яті з чергуванням адрес (interleaved memory) послідовні адреси розташовуються в різних банках: комірка з адресою i знаходиться в банку з номером i mod n. Нехай, наприклад, пам'ять складається з чотирьох банків, по 256 байт в кожному. У схемі, орієнтованій на блокову адресацію, першому банку будуть виділені віртуальні адреси 0-255, другому - 256-511 і т.д. В схемі з чергуванням адрес послідовні комірки в першому банку матимуть віртуальні адреси 0, 4, 8, а у другому банку - 1, 5, 9 і т.д.

Розподіл адресного простору по модулях дає можливість одночасної обробки запитів на доступ до пам'яті, якщо відповідні адреси відносяться до різних банків. Процесор може в одному з циклів зажадати доступ до комірки i, а в наступному циклі - до комірки j. Якщо i і j знаходяться в різних банках, інформація буде передана в послідовних циклах. Тут під циклом розуміємо цикл процесора, тоді як повний цикл пам'яті займає декілька циклів процесора. Таким чином, в даному випадку процесор не повинен чекати, поки буде завершений повний цикл звернення до комірки i. Розглянутий прийом дозволяє підвищити пропускну спроможність: якщо система пам'яті складається з достатнього числа банків, є можливість обміну інформацією між процесором і пам'яттю з швидкістю одне слово за цикл процесора, незалежно від тривалості циклу пам'яті.

Рішення про те, який варіант розподілу адрес вибрати (поблочний або з розшаруванням), залежить від очікуваного порядку доступу до інформації. Програми компілюються так, що послідовні команди розташовуються в комірках з послідовними адресами, тому висока вірогідність, що після команди, витягнутої з комірки з адресою i, виконуватиметься команда з комірки i +1. Елементи векторів компілятор також поміщає в послідовні комірки, тому в операціях з векторами можна використовувати переваги методу чергування (рис.9.3). З цієї причини у векторних процесорах зазвичай застосовується який-небудь варіант чергування адрес. У мультипроцесорах із спільно використовуваною пам'яттю, проте, використовується поблочна адресація, оскільки схеми звертання до пам'яті в MIMD-системах можуть сильно відрізнятися. У таких системах метою є з'єднати процесор з блоком пам'яті і задіяти максимум інформації, що знаходиться в ньому, перш ніж перемкнутися на інший блок пам'яті.

Рисунок 9.3 – Пам'ять з чергуванням адрес та пам'ять з послідовними адресами