- •Івано-Франківський національний технічний

- •Університет нафти і газу

- •Комп’ютерні системи

- •Конспект лекцій

- •Лекція № 1

- •1.1 Архітектура комп’ютерних систем

- •1.2 Паралельна обробка інформації

- •Контрольні запитання

- •Лекція №2 Основи теорії комп’ютерних систем

- •2.1 Класифікація комп’ютерних систем

- •Рисинук 2.2 - Класи комп’ютерних систем

- •2.2 Паралельні алгоритми

- •2.3 Характеристика типових схем комунікації в багатопроцесорних комп’ютерних системах

- •2.4 Закон Амдала

- •Контрольні запитання

- •Лекція №3 Конвеєрні комп’ютерні системи

- •3.1 Обробка інформації векторним процесором

- •3.2 Процесор з паралельним алп

- •3.3 Структура векторного процесора

- •3.4 Векторно-конвеєрні комп’ютерні системи

- •Контрольні запитання

- •Лекція №4 Матричні комп’ютерні системи

- •4.1 Матричний процесор

- •4.2 Матрична комп’ютерна система

- •If a (умова a) then do в

- •4.3 Архітектура матричних комп’ютерних систем

- •4.4 Структура процесорного елементу

- •4.5 Підключення і відключення процесорних елементів.

- •Контрольні запитання

- •Лекція № 5 Комп’ютерні системи класу simd

- •Контрольні запитання

- •Лекція № 6 Мультипроцесорні комп’ютерні системи

- •6.1 Загальна характеристика мультипроцесорних комп’ютерних систем

- •6.2 Мультипроцесори типу numa

- •6.3 Мультипроцесори типу coma

- •6.4 Мультипроцесорна комп’ютерна система Sun Enterprise 10000:

- •Контрольні запитання

- •Лекція №7 Мультикомп’ютерні комп’ютерні системи

- •7.1 Загальна характеристика мультикомп’ютерних комп’ютерних систем

- •Мультикомп’ютерна кс

- •7.2 Рівні комплексування у кс

- •7.3 Кластери

- •7.4 Топологія кластерних пар

- •7.5 Кластер Beowulf

- •7.6 Кластер ac3 Velocity Cluster

- •7.7 Кластер ncsa nt Supercluster

- •Контрольні запитання

- •Лекція № 8 Комп’ютерні системи з нетрадиційною архітектурою

- •8.1 Асоціативні кс

- •8.2 Систолічні кс

- •8.3 Класифікація структур систол

- •8.4 Кс з наддовгими командами (vliw)

- •8.5 Комп’ютерні системи з явним паралелізмом команд

- •8.6 Кс з обробкою за принципом хвильового фронту

- •8.7 Кс на базі трансп'ютерів і з неоднорідним доступом до пам'яті

- •Контрольні запитання

- •Лекція № 9 Організація пам’яті у комп’ютерних системах

- •9.1 Запам’ятовувальні пристрої комп'ютера

- •9.2 Системи із загальною і розподіленою пам'яттю

- •9.3 Багаторівнева організація загальної пам'яті

- •9.4 Пам'ять з чергуванням адрес

- •9.5 Асоціативна пам'ять

- •Контрольні запитання

- •Лекція № 10 Системи введення-виведення

- •10.1 Мережева базова система введення-виведення netbios

- •10.2 Пристрої для зберігання bios

- •10.3 Виробники bios

- •10.4 Принцип роботи bios

- •Контрольні запитання

- •Лекція № 11 Інтерфейси

- •Контрольні запитання

If a (умова a) then do в

оператор В буде виконаний, якщо умова А справедлива у всіх ПЕ. Для коректного включення/відключення процесорних елементів КМП повинен знати результат перевірки умови А у всіх ПЕ. Така інформація передається в КМП по однонаправленій шині результату. У системі СМ-2 ця шина названа GLOBAL. У системі МРР для тієї ж мети організована структура, звана деревом SUM-OR. Кожен ПЕ розміщує вміст свого однорозрядного регістра ознаки на вході дерева, яке за допомогою операції логічного складання комбінує цю інформацію і формує слово результату, використовуване в КМП для ухвалення рішення.

4.3 Архітектура матричних комп’ютерних систем

У матричних SIMD-системах поширення набули два основні типи архітектурної організації масиву процесорних елементів.

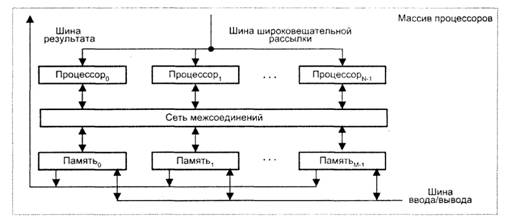

У першому варіанті (рис.4.4), відомому як архітектура типу “процесорний елемент - процесорний елемент” (“ПЕ-ПЕ”):

- N процесорних елементів (ПЕ) зв'язані між собою мережею з'єднань;

- кожен ПЕ - це процесор з локальною пам'яттю;

- процесорні елементи виконують команди, що надходять з КМП по шині широкомовної розсилки, і обробляють дані що зберігаються в їх локальній пам'яті або поступають з КМП;

- обмін даними між процесорними елементами проводиться по мережі з'єднань, тоді як шина введення/виведення служить для обміну інформацією між ПЕ і пристроями введення/виведення;

- для трансляції результатів з окремих ПЕ в контроллер масиву процесорів служить шина результату;

- завдяки використанню локальної пам'яті апаратні засоби КС даного типу можуть бути побудовані дуже ефективно. У багатьох алгоритмах дії по пересилці інформації здебільшого локальні, тобто відбуваються між найближчими сусідами. З цієї причини архітектура, де кожен ПЕ пов'язаний тільки з сусідніми, дуже популярна. Як приклади обчислювальних систем з даною архітектурою можна згадати MasPar MP-1, Connection Machine CM-2, GF11, DAP, МРР, STARAN, PEPE, ILLIAC IV.

Рисунок 4.4 – Архітектура типу “процесорний елемент - процесорний елемент”

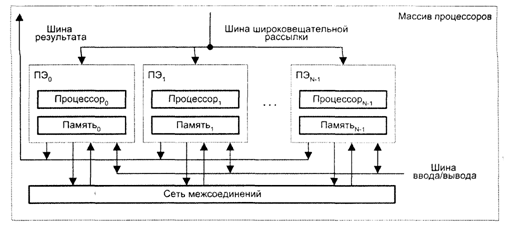

Другий вид архітектури – “процесор-пам'ять” (рис.4.5). В такій конфігурації двонаправлена мережа з'єднань зв'язує N процесорів з М модулями пам'яті. Процесори управляються КМП через широкомовну шину. Обмін даними між процесорами здійснюється як через мережу, так і через модулі пам'яті. Пересилка даних між модулями пам'яті і пристроями введення/виведення забезпечується шиною введення/ виведення. Для передачі даних з конкретного модуля пам'яті в КМП служить шина результату. Прикладами КС з розглянутою архітектурою можуть служити Burroughs Scientific Processor (BSP), Texas Reconfigurable Array Computer (TRAC).

Рисунок 4.5 – Архітектура типу “процесор-пам'ять”

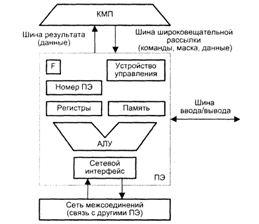

4.4 Структура процесорного елементу

У більшості матричних SIMD-систем як процесорні елементи застосовуються прості RISC-процесори з локальною пам'яттю обмеженої місткості.

Наприклад, кожен ПЕ системи MasPar MP-1 складається з чотирьохрозрядного процесора з пам'яттю місткістю 64 Кбайт. У системі МРР використовуються однорозрядні процесори з пам'яттю 1 кбіт кожен, а в СМ-2 процесорний елемент є однорозрядний процесор з 64 Кбіт локальної пам'яті. Завдяки простоті ПЕ масив може бути реалізований у вигляді однієї надвеликої інтегральної мікросхеми (НВІС). Це дозволяє скоротити число зв'язків між мікросхемами і, отже, габарити КС. Так, одна НВІС в системі СМ-2 містить 16 процесорів (без блоків пам'яті), а в системі MasPar MP-1 НВІС складається з 32 процесорів (також без блоків пам'яті). У системі МР-2 є видимим тенденція до застосування складніших мікросхем, зокрема 32-розрядних процесорів з 256 Кбайт пам'яті в кожному.

Невід'ємними компонентами ПЕ (рис.4.6) в більшості обчислювальних систем є:

- арифметико-логічний пристрій (АЛП);

- регістри даних;

- мережевий інтерфейс (МІ), який може включати в свій склад регістри пересилки даних;

- номер процесора;

- регістр прапора дозволу маскування (F);

- локальна пам'ять.

Рисунок 4.6 – Структура процесорного елемента

Процесорні елементи, керовані командами, що поступають по широкомовній шині з КМП, можуть вибирати дані з своєї локальної пам'яті і регістрів, обробляти їх в АЛП і зберігати результати в регістрах і локальній пам'яті. ПЕ можуть також обробляти ті дані, які поступають по шині широкомовної розсилки з КМП. Крім того, кожен процесорний елемент має право отримувати дані з інших ПЕ і відправляти їх в інші ПЕ по мережі з'єднань, використовуючи для цього свій мережевий інтерфейс. У деяких матричних системах, зокрема в MasParМР-1, елемент даних з ПЕ-джерела можна передавати в ПЕ-приймач безпосередньо, тоді як в інших, наприклад в МРР, - дані заздалегідь повинні бути розміщені в спеціальний регістр пересилки даних, що входить до складу мережевого інтерфейсу. Пересилка даних між ПЕ і пристроями введення/виведення здійснюється через шину введення/виведення КС. У ряді систем (MasParMP-1) ПЕ підключені до шини введення/виведення за допомогою мережі з'єднань і каналу введення/виведення системи. Результати обчислень будь-який ПЕ видає в КМП через шину результату.

Кожному з N ПЕ в масиві процесорів привласнюється унікальний номер, званий також адресою ПЕ, яка є цілим числом від 0 до N- 1. Щоб вказати, чи повинен даний ПЕ брати участь в загальній операції, в його складі є регістр прапора дозволу F. Стан цього регістра визначають сигнали управління з КМП, або результати операцій в самому ПЕ, або і ті та інші спільно.

Ще однією істотною характеристикою матричної системи є спосіб синхронізації роботи ПЕ. Оскільки всі ПЕ отримують і виконують команди одночасно, їх робота жорстко синхронізується. Це особливо важливо в операціях пересилки інформації між ПЕ. У системах, де обмін проводиться з чотирма сусідніми ПЕ, передача інформації здійснюється в режимі “регістр- регістр”.