- •Цифрові еом

- •Керівник роботи _______Єфимець в.М._____________

- •Технічне завдання

- •8. Принципова схема мікрокомп’ютера 33

- •Система команд мікрокомп’ютера

- •Програма задачі в змістовній формі

- •Розподіл адресного простору пам’яті

- •Визначення формату команди

- •Довжина поля коп

- •Кодування машинних операцій

- •Вибір режиму адресації

- •Пряма адресація

- •Опесердковано-регістрова адресація

- •Формати команд і алгоритм функціонування мікрокомп’ютера

- •Формати і цикли команд

- •Програмно-мікропрограмна модель мікрокомп’ютера

- •Операція «Ділення»

- •Розподіл адресного простору пам’яті мікрокоманд

- •7. Структурна схема мікрокомп’ютера.

- •7.1. Процесор.

- •7.1.1. Блок мікропрограмного керування.

- •7.1.2. Блок регістрів

- •7.1.3. Блок обробки даних бод

- •8. Принципова схема мікрокомп’ютера.

- •9. Формат мікрокоманди.

- •10. Закодована мікропрограма мікрокомп’ютера.

- •Список літератури

Розподіл адресного простору пам’яті мікрокоманд

Керуючий пристрій мікрокомп’ютера реалізує принцип програмованої

логіки. Мікропрограми тактів операцій в закодованій формі зберігаються в пам’яті мікрокоманд. Розподіл адресного простору ПМК виконується з урахуванням кількості мікрокоманд в ГМП тактів, способі реалізації декодування поля КОП, а також організації ВІС ВУ4. Орієнтований розподіл мікрокоманд показаний у табл.4.

Таблиця 4

Адреси |

АП ПМК |

Примітка |

0 |

CJP16 |

IPL |

1 |

CJP16 |

NOP |

2 |

CJP49 |

“+” |

3 |

CJP54 |

“*” |

4 |

CJP59 |

“/” |

5 |

CJP64 |

JNZ |

6-10 |

To1 |

|

11-15 |

To2 |

|

16-18 |

Твк |

|

19-24 |

То3 |

|

25-26 |

Т+ |

|

27-34 |

Т* |

|

35-46 |

Т/ |

|

47-48 |

Tjnz |

|

49 |

CJS6 |

Цикл “+” |

50 |

CJS11 |

|

51 |

CJS25 |

|

52 |

CJS19 |

|

53 |

CJP16 |

|

54 |

CJS6 |

Цикл “*” |

55 |

CJS11 |

|

56 |

CJS27 |

|

57 |

CJP19 |

|

58 |

CJP16 |

|

59 |

CJS6 |

Цикл “/” |

60 |

CJS11 |

|

61 |

CJS35 |

|

62 |

CJP19 |

|

63 |

CJP16 |

|

64 |

CJS47 |

Цикл JNZ |

65 |

CJP16 |

Для керування функціонуванням ВІС ВУ4 використовуються мікрокоди,

символічні позначення яких наведені у табл.4. Наприклад, запис CJP19 – це безумовний перехід до мікропідпрограми операції збереження ST за адресою 19. До загальної кількості мікрокоманд мікропідпрограм додається ще одна – МК виходу з мікропідпрограми.

З табл.4 випливає, що ємність пам’яті МК = 66 комірок. Отже, розрядність адреси ПМК: nАПМК=]log266[=7

7. Структурна схема мікрокомп’ютера.

Структурна схема мікрокомп’ютера показана на рис.16. До його складу входять: процесор, пам’ять, пристрої вводу/виводу, генератор тактових імпульсів.

Рис.16.

7.1. Процесор.

Склад процесора: БМК, БОД, блок регістрів.

7.1.1. Блок мікропрограмного керування.

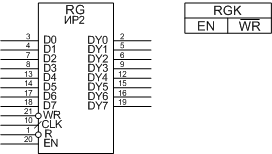

Регістр команд RGK призначений для прийому, зберігання та видачі коду команди. Для реалізації RGK використовуємо ІМС КМ1804ИР2.

Умовно-графічне позначення регістра і поле мікрокоманди керування ним показано на рис.17.

Рис.17

Кількість ІМС ИР2, які необхідні для реалізації регістра RGK, дорівнює:

n/nИР2=24/8=3

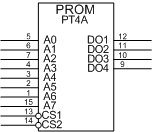

Перетворювач початкової адреси ППА виконує функцію декодера КОП. Реалізується на ВІС КР556РТ4А (рис.18).

Рис.18

Мультиплексор логічних умов MX ЛУ призначений для комутації логічних умов (ЛУ) ПА1, ПА2, ПА3, N, Z, NZ, Т на вхід “СС” ВІС ВУ4. Для вибору ЛУ використовується поле MS в полі мікрокоманди БМК. Розрядність поля визначається за формулою:

nMS=]log2(L+1)[

де L – кількість логічних умов. У нашому випадку L=7.

nMS=]log2(7+1)[=3

Кодування логічних умов в полі MS наведено у табл.5.

Таблиця 5

-

К(MS)

ЛУ

000

“1”

001

N

010

Z

011

NZ

100

ПА1

101

ПА2

110

ПА3

111

Т

Мультиплексор MX реалізується на ІМС КР1533КП5

.

.

Рис.19

Схема керування послідовністю МК призначена для генерації адрес МК і реалізується на ВІС КМ1804ВУ4.

Рис. 20. УГП СКПМК1804ВУ4

Мікрокоманда керування ВІС ВУ4 має таку структуру:

16 |

ВУ4 |

0 |

|||||||||||||||

3 |

I |

0 |

6 |

A |

0 |

2 |

MS |

0 |

CI |

CC |

COM |

||||||

16 |

|

13 |

12 |

|

6 |

5 |

|

3 |

|

2 |

|

|

1 |

|

|

0 |

|

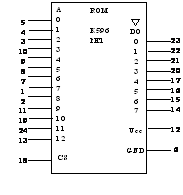

Пам’ять мікрокоманд ПМК називається керуючою і призначена для зберігання мікропрограм операцій. Орієнтована ємність ПМК 66 комірок. Розрядність комірок ПМК відповідає розрядності МК. Реалізується як ПЗП (ROM) на ВІС КР556РТ17, що має організацію 0,5Кх8. (Примітка: як буде визначено пізніше, розрядність мікрокоманди становить nМК=56, отже для реалізації запам’ятовуючого масиву ПМК потрібно буде взяти 56/8=7 мікросхем РТ17).

Рис. 21. УГП ПЗП на ВІС КР556РТ17

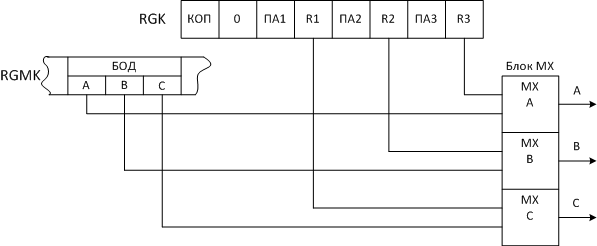

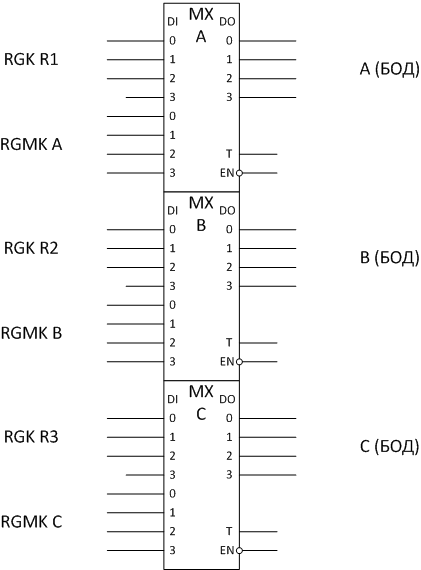

Блок мультиплексорів MX призначений для комутації адрес звернень до регістрів загального призначення (РЗП), що представлені в полях R1, R2, R3 коду команди або адрес звернень до регістрів мікрокоманд, що відображені в полях A, B, C регістра RGMK (поле БОД). Структура блока MX представлена на рис.22.

Блок MX реалізується на ІМС КР1533КП11.

Поле БМК коду мікрокоманди має таку структуру:

20 |

БМК |

0 |

||||||||||||||||

RGMK |

16 |

ВУ4 |

0 |

MX |

MX |

МХ |

||||||||||||

EN |

WR |

3 |

I |

0 |

6 |

A |

0 |

2 |

MS |

0 |

CI |

CC |

COM |

A |

B |

С |

||

Рис.22

Функціональна схема блока MX показана на рис.23.

Рис.23