- •Лекция 1. Основы цифровой техники.

- •Лекция 2. Синтез кцу

- •Лекция 3. Шифраторы. Дешифраторы.

- •Синтез и анализ работы шифраторов на микросхемах логических элементов.

- •1 Элемент 5и-не.

- •Контрольные вопросы:

- •Лекция 4-5. Преобразователи кодов. Мультиплексоры и демультиплексоры.

- •Контрольные вопросы:

- •Лекция 6. Сумматоры. Цифровые компараторы. Арифметическо-логические устройства (алу).

- •Лекция 7-8. Раздел 3. Последовательностные цифровые устройства. Интегральные триггеры.

- •§ 4.3. Структура и особенности работы

- •Лекция 10-11. Счетчики.

- •Лекция 12. Запоминающие устройства.

- •Лекция 13-14. Системы управления.

- •Лекция 15. Общие сведения о микропроцессорах (мп) и микропроцессорных системах (мпс).

- •§ 5.4. Структура и назначение основных узлов микропроцессора серии кр580.

- •Форматы команд.

- •Система команд.

- •Способы адресации.

- •Разработка линейных программ.

- •5. Число "а" из озу

- •7. Вычитание без переноса

- •Микроконтроллеры.

- •1. Структура и назначение основных узлов микропроцессора серии кр580.

- •Практическая работа №1 «Анализ работы логических элементов»

- •Практическая работа №2 «Синтез и анализ работы кцу в базисе и,или,не»

- •Практическая работа № 4 «Синтез и анализ работы шифратора»

- •Практическая работа № 5 «Синтез и анализ работы дешифратора»

- •Практическая работа № 6-7 «Синтез и анализ работы преобразователя кодов»

- •Практическая работа № 10-11 «Синтез счетчика с параллельным переносом»

- •Практическая работа № 12-13 «Построение зу заданной емкости и разрядности»

- •Практическая работа № 14-15 «Синтез и анализ работы уу со схемной логикой»

- •Приложение 1. Справочный материал по микросхемам

- •Сумматор, компаратор, схема контроля ч етности, алу и схема ускоренного переноса.

- •И нтегральные триггеры.

- •Регистры и регистровые файлы.

- •Счетчики.

- •10. Запоминающие устройства.

Лекция 7-8. Раздел 3. Последовательностные цифровые устройства. Интегральные триггеры.

Основой структуры любых последовательностных ЦУ являются элементы памяти, получившие название интегральных триггеров.

Л юбой

интегральный триггер – это простейший

элемент памяти, способный запомнить и

сохранить 1 бит

информации: один 0 или одну 1 (термин

"бит" произошел от английского

binary

digit

– двоичный разряд, знак, цифра).

Соответственно имеет два устойчивых

состояния: 0 и 1. В одном состоянии на

прямом выходе (см. ниже) триггера

удерживается 0, в другом – 1 даже при

сбросе активных сигналов на всех его

входах. Любой интегральный триггер

имеет два комплементарных выхода (см.

рис. 4.1): прямой

юбой

интегральный триггер – это простейший

элемент памяти, способный запомнить и

сохранить 1 бит

информации: один 0 или одну 1 (термин

"бит" произошел от английского

binary

digit

– двоичный разряд, знак, цифра).

Соответственно имеет два устойчивых

состояния: 0 и 1. В одном состоянии на

прямом выходе (см. ниже) триггера

удерживается 0, в другом – 1 даже при

сбросе активных сигналов на всех его

входах. Любой интегральный триггер

имеет два комплементарных выхода (см.

рис. 4.1): прямой

![]() и инверсный

и инверсный

![]() .

.

Интегральные триггеры могут иметь входы следующего назначения:

R (reset), K – входы сброса (в ноль). При подаче активного сигнала на такой вход триггер устанавливается в состояние 0, то есть на его прямом выходе устанавливается уровень логического 0.

S (set), J – входы установки (единицы). При подаче активного сигнала на такой вход триггер устанавливается в состояние 1, то есть на его прямом выходе устанавливается уровень логической 1.

D (data) – информационный вход. На прямом выходе триггера устанавливается такой же сигнал, какой подается на вход D.

Т (complementing) – счетный вход. При подаче активного сигнала на такой вход триггер переключается в другое состояние, то есть тот уровень сигнала, который удерживался на выходе триггера в предыдущий момент времени, меняется на противоположный.

С или CLK (clock) – синхронизирующий вход. Подача активного сигнала на такой вход дает разрешение на срабатывание триггера, причем жестко определяя момент срабатывания . Триггеры, имеющие вход С, называются синхронными, не имеющие такого входа – асинхронными. Асинхронные триггеры практически встречаются редко.

Управление интегральными триггерами.

По способу управления входы интегральных триггеров могут быть статическими и динамическими, для которых активным сигналом является импульс (точнее, фронт импульса, то есть перепад напряжения на входе с уровня логического 0 до уровня логической 1 или наоборот).

Динамические входы могут быть:

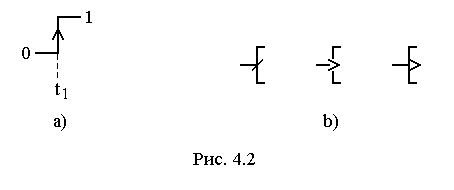

Прямые динамические, для которых активным сигналом является положительный перепад напряжения (передний фронт положительного импульса) от уровня логического 0 до уровня логической 1 в момент t1 (см. рис. 4.2а). В технической и справочной литературе такой активный сигнал принято обозначать: _|¯ , ↑ или Р (positive-going edge - положительный перепад).

Т ри

допустимых стандартом изображения этих

входов приведено на рис. 4.2b.

ри

допустимых стандартом изображения этих

входов приведено на рис. 4.2b.

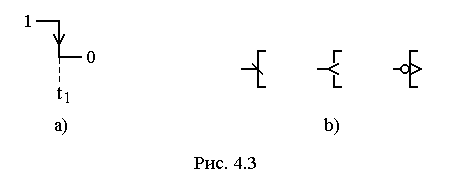

И

нверсные

динамические,

для которых активным сигналом является

отрицательный

перепад

напряжения

(задний фронт положительного импульса)

от уровня логической 1 до уровня

логического 0 в момент t1

(см. рис. 4.3а). В технической и справочной

литературе такой активный сигнал

принято обозначать: ¯|_ , ↓ или N

(negative

edge

- отрицательный перепад) - Три допустимых

стандартом изображения этих входов

приведено на рис. 4.3b.

нверсные

динамические,

для которых активным сигналом является

отрицательный

перепад

напряжения

(задний фронт положительного импульса)

от уровня логической 1 до уровня

логического 0 в момент t1

(см. рис. 4.3а). В технической и справочной

литературе такой активный сигнал

принято обозначать: ¯|_ , ↓ или N

(negative

edge

- отрицательный перепад) - Три допустимых

стандартом изображения этих входов

приведено на рис. 4.3b.

Динамическими, как правило, делают синхронизирующие входы С. В этом случае соответствующий перепад напряжения (перепад логических уровней) на таком входе дает разрешение на срабатывание триггера, а момент перепада t1 жестко определяет момент срабатывания триггера.