- •Лекция 1. Основы цифровой техники.

- •Лекция 2. Синтез кцу

- •Лекция 3. Шифраторы. Дешифраторы.

- •Синтез и анализ работы шифраторов на микросхемах логических элементов.

- •1 Элемент 5и-не.

- •Контрольные вопросы:

- •Лекция 4-5. Преобразователи кодов. Мультиплексоры и демультиплексоры.

- •Контрольные вопросы:

- •Лекция 6. Сумматоры. Цифровые компараторы. Арифметическо-логические устройства (алу).

- •Лекция 7-8. Раздел 3. Последовательностные цифровые устройства. Интегральные триггеры.

- •§ 4.3. Структура и особенности работы

- •Лекция 10-11. Счетчики.

- •Лекция 12. Запоминающие устройства.

- •Лекция 13-14. Системы управления.

- •Лекция 15. Общие сведения о микропроцессорах (мп) и микропроцессорных системах (мпс).

- •§ 5.4. Структура и назначение основных узлов микропроцессора серии кр580.

- •Форматы команд.

- •Система команд.

- •Способы адресации.

- •Разработка линейных программ.

- •5. Число "а" из озу

- •7. Вычитание без переноса

- •Микроконтроллеры.

- •1. Структура и назначение основных узлов микропроцессора серии кр580.

- •Практическая работа №1 «Анализ работы логических элементов»

- •Практическая работа №2 «Синтез и анализ работы кцу в базисе и,или,не»

- •Практическая работа № 4 «Синтез и анализ работы шифратора»

- •Практическая работа № 5 «Синтез и анализ работы дешифратора»

- •Практическая работа № 6-7 «Синтез и анализ работы преобразователя кодов»

- •Практическая работа № 10-11 «Синтез счетчика с параллельным переносом»

- •Практическая работа № 12-13 «Построение зу заданной емкости и разрядности»

- •Практическая работа № 14-15 «Синтез и анализ работы уу со схемной логикой»

- •Приложение 1. Справочный материал по микросхемам

- •Сумматор, компаратор, схема контроля ч етности, алу и схема ускоренного переноса.

- •И нтегральные триггеры.

- •Регистры и регистровые файлы.

- •Счетчики.

- •10. Запоминающие устройства.

Приложение 1. Справочный материал по микросхемам

В этом приложении приведено условное графическое изображение всех микросхем, которые необходимы при выполнении практических работ, а также при курсовой работе; указана нумерация выводов их корпусов, а также при необходимости даются краткие пояснения.

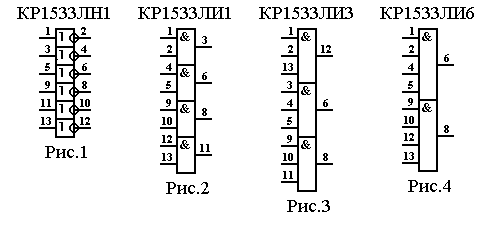

1. Логические элементы.

Р ис.

1. 6 элементов НЕ.

ис.

1. 6 элементов НЕ.

Рис. 2. 4 элемента 2И.

Рис. 3. 3 элемента 3И.

Рис. 4. 2 элемента 4И.

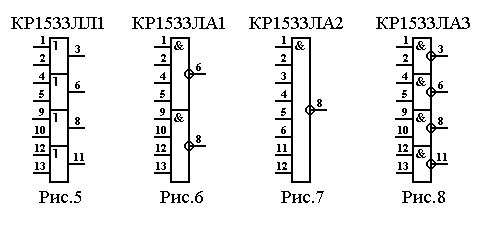

Рис. 5. 4 элемента 2ИЛИ.

Рис. 6. 2 элемента 4И-НЕ.

Рис. 7. 1 элемент 8И-НЕ.

Р ис.

8. 4 элемента 2И-НЕ.

ис.

8. 4 элемента 2И-НЕ.

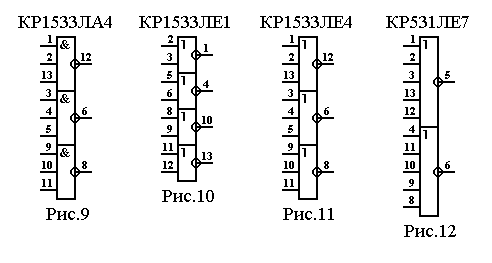

Рис. 9. 3 элемента 3И-НЕ.

Рис. 10. 4 элемента 2ИЛИ-НЕ.

Рис. 11. 3 элемента 3ИЛИ-НЕ.

Рис. 12. 2 элемента 5ИЛИ-НЕ.

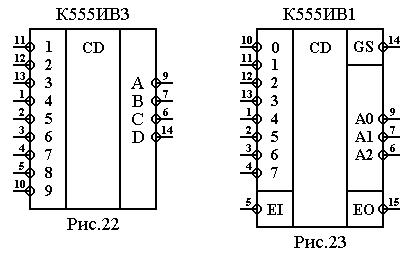

Шифраторы.

Шифраторы.

Рис.22 (с. 70,71). Приоритетный шифратор 10х4.

Рис.23 (с. 71-72). Приоритетный шифратор 8х3.

Дешифраторы.

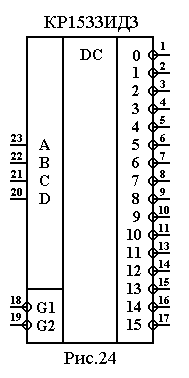

Рис.24 (с.80,81). Дешифратор-демультиплексор 4х16.

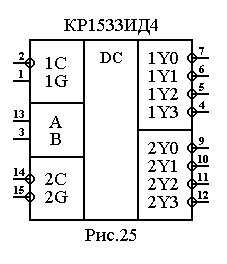

Рис.25 (с. 81-83). Сдвоенный дешифратор-демультиплексор 2х4.

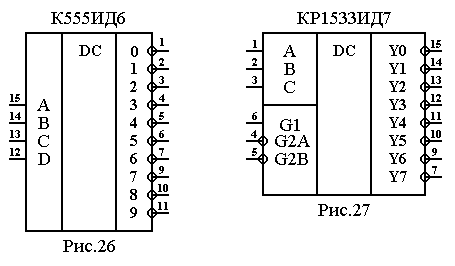

Рис.26 (с. 80). Дешифратор 4х10.

Рис.27 (с. 81). Дешифратор-демультиплексор 3х8.

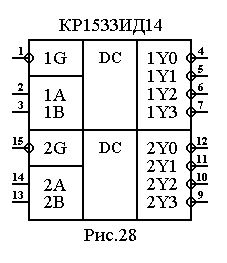

Рис.28 (с. 81,82). Два дешифратора-демультиплексора 2х4.

П

реобразователь

кодов

реобразователь

кодов

и сегментный цифровой индикатор.

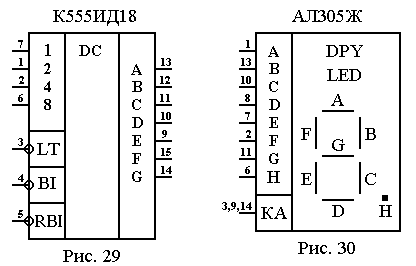

Рис. 29 (с. 88-90). Преобразователь двоично-десятичного кода в семиразрядный код управления сегментными цифровыми индикаторами.

Рис. 30 (с. 88-90). Сегментный цифровой индикатор на световых излучающих диодах с общим катодным выводом.

Мультиплексоры.

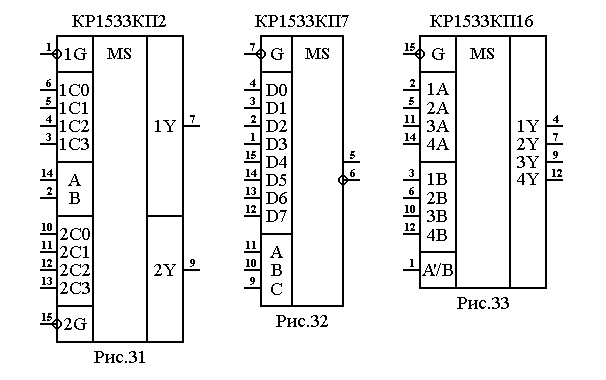

Р ис.31

(с. 97,98). Сдвоенный селектор-мультиплексор

4-1.

ис.31

(с. 97,98). Сдвоенный селектор-мультиплексор

4-1.

П р и м е ч а н и е :

Если микросхема используется как один двухразрядный селектор-мультиплексор 4-1, то ее выводы удобнее располагать так, как показано на рис. 3.25b.

Такую же структуру имеет микросхема КР1533КП19, но у нее инверсные выходы.

Рис.32 (с. 99). Селектор-мультиплексор 8-1.

Рис.33 (с. 99,100). Четырехразрядный селектор-мультиплексор 2-1.

П р и м е ч а н и я :

Если микросхема используется как четыре одноразрядных селектора-мультиплексора 2-1 (счетверенный селектор-мультиплексор 2-1), то ее выводы удобнее располагать так, как на рис. 3.29а.

Такую же структуру имеет микросхема КР1533КП18, но у нее инверсные выходы.

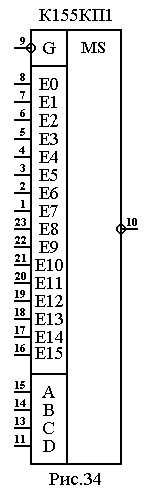

Рис.34 (с. 99). Селектор-мультиплексор 16-1.

Сумматор, компаратор, схема контроля ч етности, алу и схема ускоренного переноса.

Рис.35 (с. 112-113). Четырехразрядный двоичный сумматор со встроенной СУП.

Р ис.

36 (с. 117,118). Четырехразрядный цифровой

компаратор.

ис.

36 (с. 117,118). Четырехразрядный цифровой

компаратор.

Рис. 37. (с. 121,122). Девятиразрядная схема контроля четности.

Рис. 38 (с. 118-121). Четырехразрядное АЛУ.

Рис. 39. Четырехразрядная схема ускоренного переноса для АЛУ.

И нтегральные триггеры.

Рис. 40. Четыре асинхронных RS-триггера, у которых выведены только прямые выходы. Триггеры 1 и 3 имеют объединенные по И входы установки S, то есть установка 1 на выходе этих триггеров производится только при одновременной подаче активных сигналов на оба входа S.

Рис. 41. Синхронный JK-триггер MS-типа с объединенными по И входами J и К, а также дополнительными асинхронными входами сброса CLR и установки PRE.

Рис. 42 (с. 131-133). Два синхронных JK-триггера с асинхронным сбросом CLR.

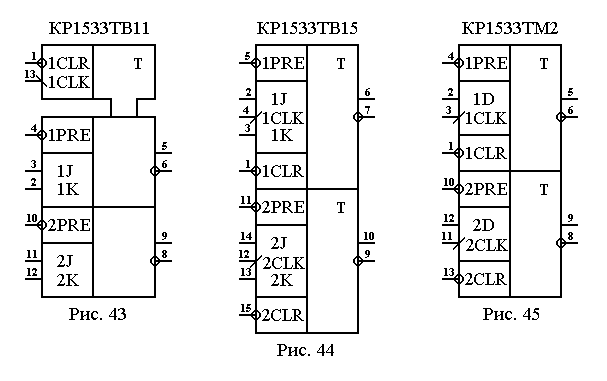

Р

ис.

43. Сдвоенный JK-триггер с

раздельной асинхронной установкой PRE,

общей синхронизацией CLK

и общим асинхронным сбросом CLR.

ис.

43. Сдвоенный JK-триггер с

раздельной асинхронной установкой PRE,

общей синхронизацией CLK

и общим асинхронным сбросом CLR.

Рис. 44. Два синхронных JK-триггера с асинхронными входами установки PRE и сброса CLR.

Рис. 45. Два синхронных D-триггера с асинхронными входами установки PRE и сброса CLR.

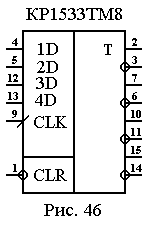

Рис. 46. Четыре D-триггера с общей синхронизацией CLK и общим асинхронным сбросом CLR.